## Technology Focus: Test & Measurement

## Simulation Testing of Embedded Flight Software

NASA's Jet Propulsion Laboratory, Pasadena, California

Virtual Real Time (VRT) is a computer program for testing embedded flight software by computational simulation in a workstation, in contradistinction to testing it in its target central processing unit (CPU). The disadvantages of testing in the target CPU include the need for an expensive test bed, the necessity for testers and programmers to take turns using the test bed, and the lack of software tools for debugging in a real-time environment. By virtue of its architecture, most of the flight software of the type in question is amenable to development and testing on workstations, for which there is an abundance of commercially available debugging and analysis software tools. Unfortunately, the timing of a workstation differs from that of a target CPU in a test bed. VRT, in conjunction with closed-loop simulation software, provides a capability for executing embedded flight software on a workstation in a close-to-real-time environment. A scale factor is used to convert between execution time in VRT on a workstation and execution on a target CPU. VRT includes high-resolution operating-system timers that enable the synchronization of flight software with simulation software and ground software, all running on different workstations.

This program was written by Mohammad Shahabuddin and William Reinholtz of Caltech for NASA's Jet Propulsion Laboratory. *Further information is contained in a TSP (see page 1).*

In accordance with Public Law 96-517, the contractor has elected to retain title to this invention. Inquiries concerning rights for its commercial use should be addressed to:

Innovative Technology Assets Management JPL

Mail Stop 202-233 4800 Oak Grove Drive Pasadena, CA 91109-8099 (818) 354-2240 E-mail: iaoffice@jpl.nasa.gov Refer to NPO-30689, volume and number of this NASA Tech Briefs issue, and the

page number.

## **This technique is especially useful for characterizing thermal-barrier coating materials.**

John H. Glenn Research Center, Cleveland, Ohio

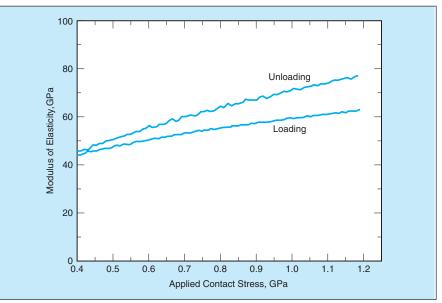

A cylindrical-punch indentation technique has been developed as a means of measuring the nonlinear elastic responses of materials - more specifically, for measuring the moduli of elasticity of materials in cases in which these moduli vary with applied loads. This technique offers no advantage for characterizing materials that exhibit purely linear elastic responses (constant moduli of elasticity, independent of applied loads). However, the technique offers a significant advantage for characterizing such important materials as plasma-sprayed thermal-barrier coatings, which, in cyclic loading, exhibit nonlinear elasticity with hysteresis related to compaction and sliding within their microstructures.

A specimen to be tested by the cylindrical-punch indentation technique is prepared by standard metallographic procedures. The specimen is mounted on a load-versus-displacement-measuring apparatus, which could be any of a variety of indentation-type hardness testers or other conventional mechanical testing instruments. In the indentation test, the flat end of a round cylindrical punch is pushed into the polished, flat surface of the specimen. To minimize impression creep (a time-dependent plastic deformation that could contribute a large error to the modulus data), the specimen is preconditioned by pre-indenting it at a load greater than the load to be applied during the subse-

These **Plots of Modulus of Elasticity** as a function of applied stress were calculated from displacementvs.-load data for a 127-µm-diameter flat-bottom cylindrical tungsten carbide punch against a thermalbarrier coating of plasma-sprayed  $ZrO_2$  containing 8 weight percent of  $Y_2O_3$  during the third loading/unloading cycle of an indentation.