# Reducing Printed Circuit Board Emissions with Low-Noise Design Practices

Arthur T. Bradley<sup>#1</sup>, Jennine Fowler<sup>#2</sup>, Brian Yavoich<sup>#3</sup>, Stephen Jennings<sup>#4</sup>

NASA Langley Research Center

5 North Dryden, MS488, Hampton, VA 23681 USA

<sup>1</sup>arthur.t.bradley@nasa.gov <sup>2</sup>jfowler12391@gmail.com <sup>3</sup>byavoich@gmail.com

4stephen.a.jennings@nasa.gov

Abstract— This paper presents the results of an experiment designed to determine the effectiveness of adopting several low-noise printed circuit board (PCB) design practices. Two boards were designed and fabricated, each consisting of identical mixed-signal circuitry. Several important differences were introduced between the board layouts: one board was constructed using recommended low-noise practices and the other constructed without such attention. The emissions from the two boards were then measured and compared, demonstrating an improvement in radiated emissions of up to 22 dB.

### I. INTRODUCTION

There are numerous papers and textbooks that present recommended low-noise PCB design techniques (1-5). However, empirical data for the effectiveness of such techniques is often not readily available. In this paper, we examine the reduction in radiated emissions that resulted from following several recommended PCB design practices.

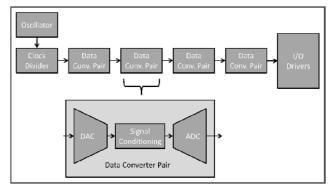

We began by designing a mixed-signal circuit that would be representative of many small-scale sensor conditioning applications. The block diagram of the circuit is given in Fig. 1. The board was completely self-contained, with the exception of a DC power supply connection. Signals were generated on board using an oscillator and digital logic circuitry. The signals were then passed between four pairs of ADCs and DACs, converting back and forth from analog-to-digital and digital-to-analog. The purpose of the conversion was simply to generate realistic digital switching noise. The signal was then buffered for off-board transmission (useful for future cable noise testing experiments).

# II. PRINTED CIRCUIT BOARD DESIGN

Two PCBs were designed containing identical electronic circuitry. The first board, a.k.a. the "Good" board, incorporated several low-noise PCB layout practices—discussed in this paper. The second board, a.k.a. the "Bad" board, neglected to follow these practices. A brief summary of the specific differences is outlined in Table I. A more detailed discussion of each difference follows the table.

Fig. 1 Circuit architecture

TABLE I: DIFFERENCES BETWEEN PRINTED CIRCUIT BOARDS

| Topic                 | "Good" Board                                   | "Bad" Board                                                    |

|-----------------------|------------------------------------------------|----------------------------------------------------------------|

| Stack up              | Signal layers paired around common image plane | Signal layers not adjacent to a single image plane             |

| Crossing splits       | No high-frequency signals cross split          | Digital signals cross<br>split without<br>stitching capacitors |

| Decoupling capacitors | Complex decoupling network                     | Single decoupling capacitor values                             |

| Series<br>termination | Digital signal termination resistors           | No series termination resistors                                |

| Ground planes         | Separate digital and analog ground planes      | Single ground plane                                            |

| Power plane offset    | Keep out zone around board edge                | Planes routed to board edge                                    |

| Guard fence           | Grounded guard fence around board              | No guard fence                                                 |

| I/O<br>configuration  | I/O ground<br>segregated using<br>split        | No I/O ground segregation                                      |

### III. BOARD DIFFERENCES

There were several notable differences between the boards. Each is discussed in this section, along with a brief explanation of why the design practice is potentially important.

# A. Stack Up

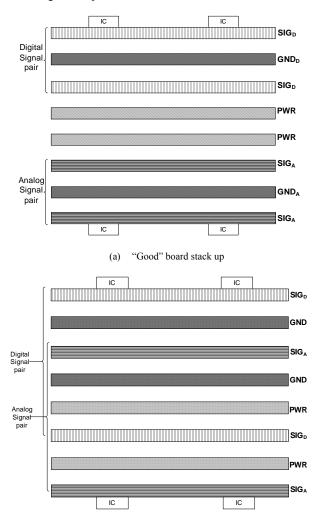

The stack up for the two boards is shown in Fig. 2. Signal pairs on the "Good" board were kept adjacent to their respective image plane. Signal pairs on the "Bad" board were intentionally separated so that the return current had to transition between two non-adjacent image planes, thereby increasing the loop area and associated emissions.

Fig. 2 Stack up of (a) "Good" and (b) "Bad" boards

(b) "Bad" board stack up

# B. Splits

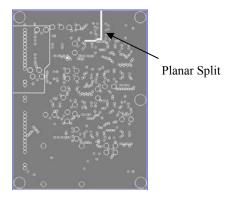

Splits in the ground and power planes are often necessary due to the creation of moats—particularly useful for circuit isolation. Routing signals across planar splits can cause a significant increase in current return loop area and the associated signal emissions.

Fig. 3 Planar split on "Bad" board

The "Bad" was designed with an L-shaped split along the top edge of the board. Eight digital signals were intentionally routed over that split without the use of stitching capacitors. The "Good" board did not include the planar split.

# C. Decoupling

Decoupling capacitors are necessary to reduce the noise resulting from dynamic current switching—especially for digital parts. For the "Bad" board, 0.1  $\mu$ F decoupling capacitors were used on every integrated circuit. For the "Good" board, a network of decoupling capacitors, ranging from 0.001  $\mu$ F to 1  $\mu$ F, was used to help broaden the power-to-ground impedance null, thereby minimizing the switching noise. The same number of capacitors was used on both boards, only the values differed.

### D. Series Termination

Series termination resistors can help dampen the signal reflections associated with digital signals. The "Good" board included 20  $\Omega$  series termination resistors on the output of the ADCs. These resistors were not included on the "Bad" board.

# E. Ground Planes

The "Good" board was designed with separate digital and analog ground planes. By necessity, the two planes were connected together at the ADCs and DACs. The "Bad" board also used two ground planes, but they were stapled together using multiple vias across the surface of the board. Conceptually, this should allow more undesired current spreading between the components.

### F. Power Plane Offset and Guard Fence

The "Good" board was designed with a ½" keep-out zone around the edge of the board. Signal traces and power planes were not allowed in the keep-out zone. An exposed, grounded guard fence was placed in this keep-out area to provide a discharge path for ESD (particularly useful during handling). The guard fence was split along each edge to prevent it from becoming a large loop antenna. The "Bad" board did not include a keep-out zone or guard fence. Fig. 4 shows the two boards. The exposed guard fence is clearly visible on the "Good" board.

Fig. 4 "Good" and "Bad" PCBs

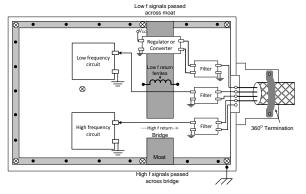

# G. I/O Segregation

It is a common practice to establish a segregated I/O area on PCBs. This isolated area is used to minimize noise coupled between the off board signals and those on the PCB. A 100-mil wide moat, along with a high-frequency bridge, was used on the "Good" board to create this I/O isolation. The segregated I/O design used on the "Good" board is shown in Fig. 5. I/O isolation was not included on the "Bad" board.

Fig. 5 Segregated I/O area

### IV. EXPERIMENTAL SETUP

The test setup is shown in Fig. 6. Radiated emissions were measured using a large biconilog antenna connected to an HP 8437A signal amplifier and Rohde & Schwarz 3GHz spectrum analyzer. PC boards were rotated so that emissions could be measured from the face of the board as well as each edge.

Fig. 6 Measuring radiated emissions

### V. RESULTS

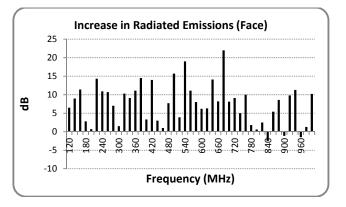

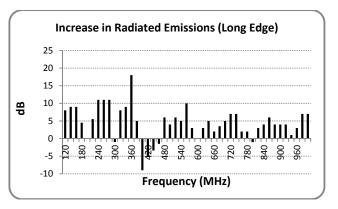

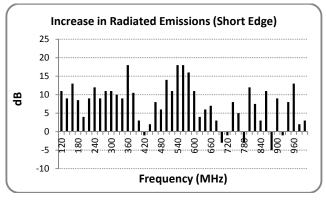

Radiated emissions, from 120 MHz to 1 GHz, were measured at a distance of five inches from the face of the board as well as each edge. The data was then normalized to the "Good" board as shown in Fig. 7. Normalization allowed for a quick determination of the relative benefits of the design practices. For example, a value of +10 dB indicates that the "Bad" board emissions were 10 dB higher than the "Good" board value for the frequency of interest.

(a) Face

(b) Long edge

(c) Short edge

Fig. 7 Increase in "Bad" board radiated emissions

# VI. CONCLUSIONS

As shown in the data, the emissions from the "Bad" board were as much as 22 dB above those of the "Good" board. This represents a significant degradation in emission performance that could easily cause a board to exceed EMC specifications.

It's important to understand that the point of this experiment was not to design the perfect, "ultra-quiet" PCB, but rather to show the relative merits of following recognized, low-noise design strategies. Every circuit is unique, some perhaps not lending themselves to certain design techniques. However, many of the methods employed during this demonstration could easily be adapted for a wide array of circuits. Adopting strategies like these that control return current flow and minimize cross-contamination between circuits can significantly reduce board noise, leading to lower radiated emissions.

# VII. REFERENCES

- Tim Williams, EMC for Product Designers, 4<sup>th</sup> ed., Elsevier Ltd., Massachusetts, 2007.

- [2] Mark I. Montrose, EMC and the Printed Circuit Board, Wiley Interscience, New York, 1999.

- [3] Bruce R. Archambeault, PCB Design for Real-World EMI Control, Kluwer Academic Publishers, Boston, 2002.

- [4] C.R. Paul, Introduction to Electromagnetic Compatibility, 2<sup>nd</sup> ed., Wiley Interscience, New Jersey, 2006.

- [5] H.W. Ott, Noise Reduction Techniques in Electronic Systems, 2<sup>nd</sup> ed., Wiley Interscience, New York, 1988.