## Large Format Transition Edge Sensor Microcalorimeter Arrays

J. A. Chervenak<sup>a</sup>, J. A. Adams<sup>b</sup>, S. B. Bandler<sup>c</sup>, S. E. Busch<sup>a</sup>, M. E. Eckart<sup>b</sup>, A. E. Ewin<sup>a</sup>, F. M. Finkbeiner<sup>e</sup>, C. A. Kilbourne<sup>a</sup>, R. L. Kelley<sup>a</sup>, J. P. Porst<sup>a</sup>, F. S. Porter<sup>a</sup>, C. Ray<sup>f</sup>, J. E. Sadleir<sup>a</sup>, S. J. Smith<sup>b</sup>, E. J. Wassell<sup>f</sup>

\*NASA Goddard Space Flight Center, Greenbelt, MD 20771, USA. \*CRESST and University of Maryland, Baltimore County, MD 21250, USA. \*CRESST and University of Maryland, College Park, MD 20742, USA. \*Northrop Grumman Corporation, Lanham, MD 20706, USA. \*Wyle Information Systems, McLean, VA 22102 USA. \*MEI TEchnoogies, Inc., Lanham, MD 27606-6228 U.S.A

## Next Generation X-ray Focal Planes

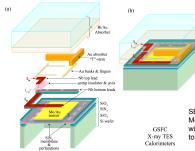

We have produced a variety of superconducting transition edge sensor array designs for microcalorimetric detection of x-rays. Designs include kilopixel scale arrays of relatively small sensors (~75 micron pitch) atop a thick metal heatsinking layer as well as arrays of membrane-isolated devices on 250 micron and up to 600 micron pitch. We discuss fabrication and performance of microstripline wiring at the small scales achieved to date. We also address fabrication issues with reduction of absorber contact area in small devices.

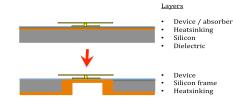

Exploded view of microcalorimeter process with microstripline wiring

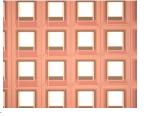

SEM image showing 75 micron pitch array on Cu with MoN groundplane. Kilopixel scale arrays produced with all pixels wired to edge of array. (To wire all pixels to pads requires a much larger chip! ~ 90 mm in dim.)

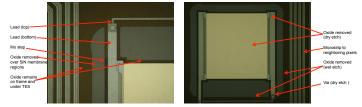

> SEM detail – 1.5 micron wide top con running under cantilevered Au absort

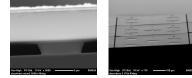

Micrographs of TES devices after microstrip process is complete

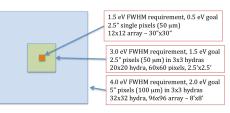

Design variations:

Rerouted wiring and via locations for compactness, symmetry, and magnitude / distribution of "self" field Normal metal features (edge banks, stripes, stem) varied Absorber thickness / material (dominant source of heat capacity in these devices)

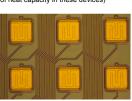

TES with microstrip surround wiring. Top conductor creates a loop around the entire device

Microstrip wiring enables new geometries to tune self fielding effects. Designs with a superconducting loop around each detector (center) show a different Ic(B) periodicity than asymmetric wiring (as in the left hand side) which applies a larger, less uniform field. (Right hand side SEM) Microstrip with 4 micron pitch (2.5 micron bottom conductor) achieved greater than 1 mA critical current and low crosstalk to neighboring pixels.

array format on 75-micron pitch (developed for solar physics). (Center) Sector of solar substrate pixel (0.87 eV at 1.5 keV). (Right) "Hydra" microcalorimeter with 2.2 eV at 6 keV in the TES in all nine absorbers.

Focal planes with multiple pixel varieties will require: Optimization of lead routing for bias uniformity Simultaneous detector specifications under same operating conditions

Heatsinking for variable bias power and high x-ray flux at array center

Proposal for fabrication reordering in solid substrate TES microcalorimeter devices

Replace initial heatsink layer deposition with deep etch under each device and subsequent thick metal deposition OPTIMIZE HEATSINK FOR ARRAYS WITH MULTIPLE DEVICE TYPE: Through shadowmasking, common devices will have a mutual heatsink while different types of devices could have some isolation among metallic heatsinking re For the back heatsink can be achieved with dee other through valer us outside of devices reation of the array and the source of the array of the source of the array of the source of the array of the source of the array of the source of the array of the source of the source of the source of the source of the array of the source of the source of the source of the source of the array of the source of the source of the source of the array of the source of the source of the source of the array of the source of the source of the array of the source of the source of the source of the array of the source of the source of the array of the source of the source of the source of the array of the source of the source of the source of the source of the array of the source of the sour

Fort to back heatsinking can be achieved with deep etched through-water vias outside of device region of the array Advantages: Fabrication is simplified by removing heatsinking layer (which has a higher surface roughness) Enables co-existence of 'solid substrate' and 'menharma' devices in same focal plane, as needed. Allows examination of possible changes to thermal crostalk channel in solid substrate. For example frontside cuts to suppress crossible through the detection.

Possible issues: Achieving equivalent film quality (RRR) on DRIE sidewall and around corner. Geometry more complex if superconducting ground plane is used / needed

Absorber Integration in Small TES or Small Absorber Stem Devices

Reduction in TES device size requires reduction in stem feature size. Further, the fraction of total absorber area must remain Small to avoid hot phonon loss.

Photoresist sacrificial layer is reflowed to promote sidewall coverage of metal seed layer for subsequent electroplating of thick absorber films

Reflow of resist into narrow stems and around comers can cause pile up that results in poor step coverage of the metal seed layer. (left hand side). Solvents can penetrate underneath the seed layer and wrinkle the absorber surface. Wrinkles emanate from regions of poor resist reflow (right hand side)

ick Au absorber, left hand side, (~3 micron) yielded without care in reflow / seed layer deposition

Thinner Au (0.8 micron, right hand side), required care in reflow, multiangle seed layer deposition to achieve flat film Film stress in thin Au can still cause delamination from photoresist sacrificial layer when cycled to high temperatures