# Commercial Parts Technology Qualification Processes

Mark S. Cooper Jet Propulsion Laboratory Pasadena, California

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

JPL Publication 13-6 2/13

# Commercial Parts Technology Qualification Processes

NASA Electronic Parts and Packaging (NEPP) Program Office of Safety and Mission Assurance

> Mark S. Cooper Jet Propulsion Laboratory Pasadena, California

> > NASA WBS: 724297 JPL Project Number: 104593 Task Number: 40.49.01.13

Jet Propulsion Laboratory 4800 Oak Grove Drive Pasadena, CA 91109

http://nepp.nasa.gov

This research was carried out at the Jet Propulsion Laboratory, California Institute of Technology, and was sponsored by the National Aeronautics and Space Administration Electronic Parts and Packaging (NEPP) Program.

Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States Government or the Jet Propulsion Laboratory, California Institute of Technology.

©2013. California Institute of Technology. Government sponsorship acknowledged.

# TABLE OF CONTENTS

| Introduction                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 EEE-INST-002                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.2 JPL Approach                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Qualification Approaches at Major NASA Contractors                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3 Northrop Grumman Space Technology (NGST, Redondo Beach)                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.4 Space Exploration Technologies (SpaceX) Qualification Processes for Flight Termination System | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4.1 Moisture Effects and Corrosion                                                              | <i>6</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4.2 Tin Whisker Growth from Pure Tin Plated Leads                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.4.3 Short Description of the Pinsky Algorithm                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.4.4 SpaceX Solder Replacement Stance                                                            | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Medical Electronics Parts Qualification Processes                                                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1 Medtronic's Electronics Parts Qualification Processes                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2 Texas Instruments (TI) Proposed Application-Based Qualification Methodology for Medical ICs   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3 Automotive Parts Qualification Processes                                                      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4 Definition of a Qualification Family                                                          | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NEPP2012 Commercial Parts Technology Qualification Processes—Conclusions                          | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| References                                                                                        | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                   | <ul> <li>1.1 EEE-INST-002</li> <li>1.2 JPL Approach</li> <li>2.1 The John Hopkins University Applied Physics Laboratory (APL)</li> <li>2.2 Southwest Research Institute (SWRI)</li> <li>2.3 Northrop Grumman Space Technology (NGST, Redondo Beach)</li> <li>2.4 Space Exploration Technologies (SpaceX) Qualification Processes for Flight Termination Syster</li> <li>2.4.1 Moisture Effects and Corrosion</li> <li>2.4.2 Tin Whisker Growth from Pure Tin Plated Leads</li> <li>2.4.3 Short Description of the Pinsky Algorithm</li> <li>2.4.4 SpaceX Solder Replacement Stance</li> <li>Medical Electronics Parts Qualification Processes</li> <li>3.1 Medtronic's Electronics Parts Qualification Processes</li> <li>3.2 Texas Instruments (TI) Proposed Application-Based Qualification Methodology for Medical ICs</li> <li>3.3 Automotive Parts Qualification Processes</li> <li>3.4 Definition of a Qualification Family</li> <li>NEPP2012 Commercial Parts Technology Qualification Processes—Conclusions</li> </ul> |

### 1.0 INTRODUCTION

Many high-reliability systems, including space systems, use selected commercial parts (including Plastic Encapsulated Microelectronics or PEMs) for unique functionality, small size, low weight, high mechanical shock resistance, and other factors. Predominantly this usage is subjected to certain 100% tests (typically called screens) and certain destructive tests usually (but not always) performed on the flight lot (typically called qualification tests). Frequently used approaches include those documented in EEE-INST-002 and JPL DocID62212 (which are sometimes modified by the particular aerospace space systems manufacturer). In this study, approaches from these documents and several space systems manufacturers are compared to approaches from a launch systems manufacturer (SpaceX), an implantable medical electronics manufacturer (Medtronics), and a high-reliability transport system process (automotive systems).

In the conclusions section, these processes are outlined for all of these cases and presented in tabular form. Then some simple comparisons are made.

In this introduction section, the PEM technology qualification process is described, as documented in EEE-INST-002 (written by the Goddard Space Flight Center, GSFC), as well as the somewhat modified approach employed at the Jet Propulsion Laboratory (JPL). Approaches used at several major NASA contractors are also described.

#### 1.1 EEE-INST-002

In this approach, screening and qualification are performed exclusively on the flight lot. Little data is requested from the part manufacturer.

The following test sequence applies to 100% screening tests:

- 1. External visual inspection and serialization

- 2. Temperature cycling (MIL-STD-883, Method 1010, Condition B (or to the manufacturer's maximum storage temperature range, whichever is less) (typically 20 cycles)

- 3. Radiography (topside for wire sweep)

- 4. CSAM (C-Mode Scanning Acoustic Microscopy) inspection (reject for any topside delamination between mold and die or more than 2/3 delamination of internal wires)

- 5. Initial (pre-burn-in) electrical measurements (per device specification, at 25°C and min. and max. rated operational temperatures)

- 6. Engineering review

- 7. Static (steady-state) burn-in (BI) test at 125°C or at max. operating temperature, per MIL-STD-883, Method 1015, Condition A or B (240 hr at 125°C, 445 hr at 105°C, 885 hr at 85°C, 1,560 hr at 70°C)

- 8. Post-static BI electrical measurements at 25°C per device specification. Calculate Delta when applicable

- 9. Dynamic burn-in test at 125°C or at max. operating temperature—MIL-STD-883, Method 1015, Condition D. Hours are the same as step 7

- 10. Final parametric and functional tests per device specification (at 25°C, max. and min. rated operating temperatures)

- 11. Calculate percent defective (steps 7–10). Maximum acceptable PDA is 5% for most space systems (lower risk posture) and 10% for higher risk posture

- 12. External visual/packing inspection

The following test sequence applies to qualification testing performed on the flight lot:

1. Visual inspection and serialization

- 2. Radiation analysis TID (Total Ionizing Dose) and SEE (Single Event Effects) (usually done by test)

- 3. Baseline C-SAM (small sample used for popcorn resistance evaluation in step 4, e.g., for variations before and after pre-conditioning)

- 4. Preconditioning (per JESD22-A113) (simulated solder reflow temperature with 3 passes at board assembly solder temperature) (SMT devices only)

- 5. Electrical measurements per device specification. Measure at 25°C, min. and max. vendor-specified operating temperatures

- 6. Life testing (HTOL, High Temperature Operating Life) 125°C per MIL-STD-883, Method 1005, Condition D. Minimum hours: 22 devices for 1,500 hours (low risk space mission) or 1,000 hours (medium risk mission)

- 7. Electrical measurement (per specification). Measure at 25°C, min. and max. vendor-specified operating temperatures

- 8. Temperature cycling per MIL-STD-883 Method 1010, Condition B (–55°C to +125°C). Minimum cycles: 22 devices for 500 cycles (low risk space mission) or 200 cycles (medium risk mission)

- 9. Electrical measurement (per specification). Measure at 25°C, min. and max. rated temperatures

- 10. C-SAM on 22 pieces

- 11. Destructive physical analysis (DPA) (MIL-STD-1580) (5 pieces)

- 12. Biased highly accelerated stress test (HAST) per JESD22 A110, with continuous bias (96 hr at  $+130^{\circ}$ C and 85% relative humidity, RH)

- 13. Unbiased HAST per JESD22-A118, Condition A (96 hr at +130°C and 85% RH)

EEE-INST-002 cautions that burn-in (and life test) design should not stress the IC junction beyond its rated capability unless supporting data is obtained from the manufacturer. In addition, the space application should be restricted to the "advertised" (datasheet) temperature range of operation.

# 1.2 JPL Approach

The JPL processes to qualify PEMs for space missions are similar to EEE-INST-002. Significant differences are described below.

JPL does not believe the temperature cycling test as a screen is effective because temperature cycling stresses package failure mechanisms that increase with number of cycles (e.g., wearout characteristic); therefore, a small number of temperature cycles does not increase the reliability of space parts. Note: JPL has test data showing no failures in early temperature cycles (less than 100 cycles).

JPL has copious data proving that X-rays (radiographic examination) of topside for wire sweep (movement of wires during the molding process) never shows a failure, or even a concern. This is not surprising in that significant wire sweep would cause wires to touch on at least a small fraction of commercial products and thus decrease yield unacceptably.

JPL uses manufacturer data to establish soldering characteristics for attachment of PEMs to the board or assembly. This precludes concern with CSAM changes before/after pre-conditioning or other stress. JPL has assessed life test data and found little correlation with CSAM results.

JPL does not perform either unbiased or biased HAST, believing that the conditions in these tests are very far from the part-level stresses found during board assembly, system assembly, or space missions. Failures in tests performed under conditions of temperature, current, or voltage very different than space mission operation conditions invalidates their significance to a situation where parts are handled properly (as they are in space systems).

JPL performs a more significant Engineering Review of burn-in test data, life test data, and extended temperature cycling data. Key electrical characteristics are plotted on probability paper (actually done by specialized software). Results show that electrical characteristics frequently follow standard distributions (typically normal distribution). Examining characteristics in this manner easily identifies statistical outliers. These outliers are culled from burn-in parts (and consequently eliminated from consideration for flight). Further, assessment of changes in electrical characteristics before/after burn-in and life test may be done without reliance on part manufacturer datasheet limits. These limits are often chosen to be wide in order to enhance yield. Changes in electrical characteristics during these stress tests may therefore be missed or underestimated and the reliability of the flight lot may be compromised.

### 2.0 QUALIFICATION APPROACHES AT MAJOR NASA CONTRACTORS

# 2.1 The John Hopkins University Applied Physics Laboratory (APL)<sup>1</sup>

Typically APL follows EEE-INST-002 closely since most space projects use it as a standard. Where contracts allow flexibility, APL prefers to perform 5 piece DPA first to identify issues with construction (similar to a construction analysis). APL prefers not to perform 100% CSAM since this does seem to correlate with reliability or system failures. However, engineering judgment is used so that APL may perform more CSAM with new PEM suppliers.

APL has found various problems with qualifying RF PEMs, typically related to test equipment and its programming. Often, RF parts do not have a complete set of specified electrical parameters over temperature. Therefore the CogE and parts engineer often must guess what these should be. In situations like this, after burn-in "failures" could become a matter of opinion.

Typically DPA failures are with bonds.

# 2.2 Southwest Research Institute (SWRI)<sup>2</sup>

SWRI has no internal standard for PEM upscreening. They develop a specification or drawing to meet customer requirements. SWRI does most upscreening for NASA projects.

SWRI follows EE-INST-002 and prefers to use initial (5 piece) DPA/Construction Analysis to identify issues. They typically perform radiation testing before—or early in—the parts qualification process.

SWRI follows EEE-INST-002 essentially.

SWRI also does radiation before or early in the parts qualification process.

SWRI prefers to not perform 100% CSAM due to difficulties in both determining failures and the lack of correlation to later failures. They note that on NASA projects, some PEM screening/qualification requirements are dropped during Parts Control Board meetings, particularly when the test lab has difficulty performing measurements or correlating with either the manufacturer or SWRI.

SWRI prefers to have PEM manufacturers upscreen to SWRI drawing due to the PEM manufacturer greater capability and lower cost, but must use an independent test lab if they are not willing, which is often the case. SWRI tries to avoid PEMs due to the high cost of complete qualification.

# 2.3 Northrop Grumman Space Technology (NGST, Redondo Beach)<sup>3</sup>

NGST does not have an internal PEM qualification approach or preference. They create a process to match customer requirements for each space project.

# 2.4 Space Exploration Technologies (SpaceX) Qualification Processes for Flight Termination Systems<sup>4</sup>

SpaceX primary Flight Termination Systems (FTS) [1] products are launch vehicles for heavy payloads to near-Earth orbits. SpaceX uses PEMs. Selection of parts for FTS is driven by mission environmental and application conditions. FTS is a harsh dynamic environment, with significant levels of mechanical shock, acceleration, and vibration.

<sup>1.</sup> Andrew Moor – Private Communication

<sup>2.</sup> Jessica Tumlinson and John Stone – Private Communication

<sup>3.</sup> Henry Law - Private Communication

<sup>4.</sup> V8017 Electronic Piece Parts Selection for Flight Termination Systems, Brian Julius and Andrew Ellsberry, August 30, 2011

Typical FTS mission durations vary from 8 to 10 minutes. Therefore long life or slow degradation of parts used within FTS are not issues. Both traditional military grade and PEM devices are designed to operate for many years, which is much greater (by orders of magnitude) than the FTS environment. On the other hand, mechanical and thermal robustness are very significant issues. PEMs are actually much more tolerant of this environment than traditional ceramic encapsulated microelectronics. Furthermore, PEMs typically do not have cavities, so particulate contamination is not an issue for most PEMs. The most important issues and risk factors for PEM usage in FTS are:

- Flight criticality of component

- Termination circuit vs. telemetry monitoring mass

- Thermal operating range and transition time

- PEM operational temperature range specified may be less than for traditional military parts, but is well within the application envelope

- PEM packages characterized for many thermal shock cycles, from 0°C to +100°CC (liquid to liquid)

- Shock levels

- PEMs tested under mechanical shock were greater than an order of magnitude more tolerant than traditional brittle ceramic packages

- Random vibration levels

- Acceleration

- Atmosphere vs. vacuum

- Humidity exposure

- Falcon avionics bays are environmentally controlled

- Corrosive environments

- Chemicals used in assembly process

- Salt fog

- Avionics bays are environmentally controlled

- Assembly and rework methods

- Special controls and soldering methods may be required for PEMs (popcorning and solder flux issues)

- Acceptance testing durations

- Derating

- Packaging

- Internal cavities of traditional military grade ceramic packages are prone to intermittent electrical outputs if conductive particles are inside the cavity

- Size of device

- Lead vs. 100% tin

- For space missions, PEMs with lead plating of pure tin, which must be covered via solder dipping to preclude tin whisker growth, are becoming the only available lead plating

- Tin whisker growth is very slow, mostly occurs at low or no gravity, and is substantially mitigated by solder dip

- Several companies offer robotic solder dip processes

- Radiation

- Historically not an issue for FTS applications

- Storage conditions

- Selected PEMs should either be stored in dry nitrogen, packaged with desiccant, or baked out prior to soldering (popcorning issue)

- Obsolescence

- Military-grade parts are more subject to obsolescence issues due to their much smaller market share

- Availability/lead times

- PEMs are typically available immediately or with a short lead time

In addition to these considerations PEMs are often of lower mass (typically 1/3) and smaller footprint than traditional military hermetic packages (particularly in small surface outline or SOIC packages). High production volumes drive the part manufacturers to tighter statistical process controls, which results in more uniformity of production lots.

SpaceX identifies traditional concerns with the usage of PEMs in high-reliability applications by quoting from PEM-INST-001:

- "1. Due to the major differences in design and construction, the standard test practices used to ensure that military devices are robust and have high reliability often cannot be applied to PEMs that have a smaller operating temperature range and are typically more frail and susceptible to moisture absorption. In contrast, high-reliability military microcircuits usually utilize large, robust, high-temperature packages that are hermetically sealed.

- 2. Unlike the military high-reliability system, users of PEMs have little visibility into commercial manufacturers' proprietary design, materials, die traceability, and production processes and procedures. There is no central authority that monitors PEM commercial product for quality, and there are no controls in place that can be imposed across all commercial manufacturers to provide confidence to high-reliability users that a common acceptable level of quality exists for all PEMs manufacturers. Consequently, there is no guaranteed control over the type of reliability that is built into commercial product, and there is no guarantee that different lots from the same manufacturer are equally acceptable. And regarding application, there is no guarantee that commercial products intended for use in benign environments will provide acceptable performance and reliability in harsh space environments."

These concerns may be summarized as:

- 1. Narrower operational temperature range guaranteed by part manufacturer

- 2. Less insight/knowledge of part manufacturer's internal designs, materials, and production processes and controls

- 3. No die traceability

- 4. No centralized agency to monitor or assess part reliability or quality controls

SpaceX asserts that they will mitigate these concerns by selecting appropriate parts for the application and through dedicated lot purchases. They assert that high-reliability PEMs that are qualified to either the Aerospace Qualified Electronic Component (AQEC) standard ANSI/GEIA-STD-0002-1 or Automotive Electronics Council (AEC) standard AEC-Q100 are qualified to similar standards as MIL-PRF-38535. Regarding harsh vs. benign environments, PEMs in general are better suited for shock and vibration environments due to their lower mass.

SpaceX mitigates against negative impacts of limited operational temperature range by selecting parts with a worst case specified operating temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. Hardware temperature range is  $-34^{\circ}$ C to  $71^{\circ}$ C (AFSPC Manual 91-710), which has been verified by measurements in launch systems.

### 2.4.1 Moisture Effects and Corrosion

Both long- and short-term storage controls are used to mitigate against moisture degradation effects. The primary failure mode due to moisture intrusion is the popcorning effect, which occurs during the assembly process and bond pad interconnect galvanic corrosion (long-term effect).

Popcorning is caused by moisture that is vaporized due to the application of heat and occurs most often during soldering. This can result in delamination, internal and external cracks, and bond damage. This

effect can be easily mitigated by thoroughly baking the parts out prior to assembly. Industry standards for bake out have been established and are defined based on the device's Moisture Susceptibility Level (MSL). SpaceX will use J-STD-033B.1, Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices, as their guide.

Long-term moisture degradation requires additional factors:

"For galvanic corrosion to occur in PEMs, the following elements are necessary: a bimetallic couple (most often gold—aluminum, present in the gold bond wire to the aluminum metallization pad), free (mobile) ionic contamination (usually chlorine, potassium, bromine, and/or sodium), and moisture (diffused from the atmosphere), to form an electrolyte. All elements listed, except ionic contamination, are present in most PEMs." [2]

This failure mode has essentially been eliminated in modern PEMs through the reduction of ionic contaminants and cleaner semiconductor processing [3]. Today's PEMs are designed to function in spite of moisture absorption, compared to hermetic devices that focus on preventing moisture. Numerous studies have been conducted on the long-term effects of moisture intrusion on PEMs. These studies suggest that using a controlled temperature and humidity environment, along with proper packaging and periodic replacement of desiccants, result in a shelf life of more than 15 years. Below is a summary of the referenced studies:

- Component Reliability After Long Term Storage [4]

- 20 component types (reel or tube of each) were tested to determine the effects of long-term storage on the original manufacturer's packaging in a warehouse environment for a duration of 2–17 years

- Packaging maintained its critical properties including tribocharging (ESD properties), but moisture barrier bags may allow moisture to enter after extended periods of time (greater than their 32-month life)

- The results of the solderability, microscopic visual inspection (SEM and optical), spectral analysis, MSL performance, and DPA demonstrate that device life is greater than 15 years

- Reliability Assessment of Electronic Components Exposed to Long-Term Non-Operating Conditions

- Study of several hundred microcircuits and assemblies stored in uncontrolled environments (sometimes outdoor, with temperature ranges as great as -40°C- to 55°C and 100% RH)

- The PCBs in the assemblies investigated showed a higher propensity for corrosion (on traces) than the PEM components installed on them

- "It is ... clear that the automotive environment is at least as harsh as the field storage environment and thus the automotive data is relevant to long-term storage"

- Commercial Plastic Encapsulated Microcircuits for Naval Aviation Applications (see footnote 5)

- Analysis of 92 commercial- grade PEMS between 2 and 28 years old through visual inspection (MIL-STD-883), solderability, electrical specifications, radiographic inspection, CSAM, and DPA

- Significant external and cosmetic anomalies were identified (the storage conditions were uncontrolled and often unknown)

- DPA resulted in no rejections of parts newer than 18 years, corrosion only evident in 2 components that were 28 years old. These failures may have had as much to do with the contemporary manufacturing processes than the storage duration

- "[CSAM] revealed delaminated areas in most parts, suggesting that this technique might not be a good method for PEM screening"

While all studies show that there is significant margin in modern PEM designs and they can be used in a wide range of conditions for extended durations, the most relevant study to how SpaceX proposes to store components is Component Reliability After Long Term Storage [4]. The one significant negative finding in

this study was that the original packaging was not sufficient to keep the components dry over extended periods, as the standard packaging is only designed for 32 months without repacking. While the components were all within specifications after a bake-out per J-STD-033, the preferable storage solution is one that completely eliminates moisture and corrosive contaminants, potentially extending the storage life to the several decades enjoyed by their hermetic counterparts. In order to deal with the stockpile related issues for PEMs, representatives of the U.S. Department of Defense and the major defense contractors created GEIA-STD-0003, Long Term Storage of Electronic Components, specifically for the long term preservation of piece parts for military and high- reliability applications. This standard goes beyond J-STD-033 and looks to preclude moisture intrusion, reduce corrosive contaminates, and regulate storage temperature to allow for long term storage rather than just protecting the devices until they are used.

SpaceX proposes all components will be handled and stored in accordance components will be stored in vapor barrier antistatic packaging that meets or exceeds the requirements.

- A low-contaminant desiccant will be used to reduce the introduction of corrosive elements

- Moisture Barrier Bags (MBBs) and desiccant will be replaced every 2 years or their rated lifespan, whichever is less

- Temperature will be controlled at  $25^{\circ}\text{C} \pm 10^{\circ}$  to reduce temperature cycling

SpaceX proposes a 3-year storage limit from the piece parts manufacturing date, lot date code, to board level assembly. The assembly service life will then be limited to 5 years from date of assembly or as defined in the assembly specification.

## 2.4.2 Tin Whisker Growth from Pure Tin Plated Leads

Unalloyed tin coatings have been shown to have an elevated propensity for producing metallic whiskers when compared to traditional tin/lead plating. These whiskers can grow between adjacent contacts or surfaces and cause short circuits and other electrical failures. Many PEMS are only available with pure tin coated leads.

With unalloyed tin finishes becoming more difficult to avoid, the aerospace industry along with government representatives, have produced GEIA-STD-0005-2, Standard for Mitigating the Effects of Tin Whiskers in Aerospace and High Performance Electronic Systems. This standard lays out a framework for using lead-free finishes based on the allowable risk.

The NASA Parts Policy, NPD8730.2C, allows for lead-free components with a mitigation plan that meets Level 2C of the GEIA standard. This is the most stringent category of regulation that allows any use of tin plating. When a Sn/Pb finish is not available, Level 2C of GEIA-STD-0005-2 requires the following for pure tin platings:

- A component-level mitigation plan and approval for each tin plated component (no blanket exceptions)

- 2 mitigations from different mitigation categories defined as follows:

- Design to reduce risk (spacing, encapsulation, redundancy)

- Use of lower risk finishes (annealed/fused, nickel underplate)

- Partial tin finish replacement (dipping component in or soldering with SnPb)

- Conformal coating

In addition to the mitigation requirements, the standard also supports the use of analytical methods to calculate the overall risk of a tin whisker failure. The Pinsky Method, developed by David Pinsky at Raytheon, is the current analysis tool of choice across much of the aerospace industry. The calculations produce an output based on the risk of different physical properties of the device, including metallurgy and lead spacing, and mitigation techniques employed. The results are based on a number of factors, including the predicted whisker density, whisker length, and effectiveness of mitigation techniques, and are shown on a logarithmic scale. Known failures due to whiskers were used as a calibration for the

results, with none of the whisker failures scoring below an 8.99; the accepted threshold for Level 2C is a score of 7 or lower.

SpaceX proposes to comply with this methodology by submitting, for Range approval, a mitigation report for each tin plated component that includes the part information, the two or greater risk mitigation strategies employed, and a risk calculation per the Pinsky Method.

# 2.4.3 Short Description of the Pinsky Algorithm

The intent of the algorithm [5] is to assess the risk that for a given application of a PEM with pure tin plated leads, that tin whiskers will bridge between conductors. The term "overall mechanical risk" is used to describe this risk of whisker bridging. Experience indicates that for many applications, the risk of a whisker bridging is so negligible that further assessment of the consequences is unnecessary. Experience has also shown that in a sizable fraction of the assessments where the mechanical risk is high, the consequences of a bridge are so evident that no further risk assessment is needed.

The concept behind the algorithm is that the mechanical risk is a product of the probability that whiskers will form, and the probability of these whiskers bridging between conductors. The factors that affect whisker growth relate to the properties of both the plating and the substrate onto which it is plated. The factors that affect the bridging risk relate to the geometry of the assembly and the presence or absence of insulating coatings on the conductors.

Note: This algorithm is based upon the premise that failure only occurs if a whisker bridges the entire gap between conductors. This premise applies to most applications, but not to high voltage applications where arcing across gaps is a common failure mode.

The output of the algorithm is a numerical index of the relative risk of whisker bridging, and as the levels of risk are anticipated to range over several orders of magnitude, the numerical index will be reported on a log-10 scale. Scaling factors have been selected so that the range of the numerical factor falls between zero and ten. Higher output numbers indicate higher degrees of risk.

There are 13 inputs used for the algorithm, which represent risk and mitigation factors that affect the probability of the formation of a whisker bridging between adjacent conductors. These factors are defined below.

```

\begin{split} r_1 &= f_1 (\text{conductor spacing}) \\ r_2 &= f_2 (\text{Pb content in plating}) \\ r_3 &= f_3 (\text{Sn deposition process}) \\ r_4 &= f_4 (\text{Sn deposit thickness}) \\ r_5 &= f_5 (\text{composition of material directly beneath Sn deposit}) \\ r_6 &= f_6 (\text{substrate controlling the CTE imposed on Sn deposit}) \\ r_7 &= f_7 (\text{reflow of Sn deposit}) \\ r_{8a} &= f_{8a} (\text{type of conformal coating applied directly over Sn deposit}) \\ r_{8b} &= f_{8b} (\text{type of conformal coating applied on the surface of adjacent conductors}) \\ r_9 &= f_9 (\text{use of mechanical hardware that applies stress to the surface of the Sn deposit}) \\ r_{10} &= f_{10} (\text{vulnerability of the assembly to contamination related failure, as indicated by imposed environmental controls during assembly}) \end{split}

```

$r_{11} = f_{11}$  (use of conformal coating on conductors throughout assembly)

$r_{12} = f_{12}$  (airflow within assembly)

The functions  $f_x$  are as defined by the table below, and the values have been adjusted during the calibration process for the algorithm.

The scale factor has been set to K = 8.9, based upon the maximum and minimum values produced by the functions defined below, to set the range of the numerical output to range from zero to ten.

These factors are combined in accordance with the following:

Overall Mechanical risk =  $R_{total}$

Total susceptibility risk factor =  $R_{susceptibility}$

(The effects of geometry on the ability of a whisker to create a bridge.)

Overall whisker growth risk factor =  $R_{formation}$

(The risk of forming a whisker of sufficient length to create a bridge.)

Scaling constant = K

Equation 1

$$R_{total} = K + log_{10} (R_{susceptibility} \cdot R_{formation})$$

The susceptibility of the application to whisker induced failures is broken into two parts: primary shorts and secondary shorts. Primary shorts occur when a whisker bridges directly from its origin to an adjacent conductor. Secondary shorts occur when whiskers become dislodged and migrate through the system to a remote site with a bridge between the two other conductors. The formation factor is also broken in two parts: the density of the whisker growth and the lengths of the whiskers.

Equation 2

$$R_{total} = K + log_{10} [(R_{primary} + R_{secondary}) (R_{density} \cdot R_{length})]$$

A simplification is made to formulate the risk that whiskers will grow by assuming that there are four independent driving mechanisms of concern:

- 1. Stress induced during initial tin deposition

- 2. Stress developed in the tin as a result of inter-diffusion with the material below during time/temperature exposure

- 3. Stress developed over time due to differential CTE between the tin and the controlling substrate

- 4. Stress induced as a result of externally applied forces

Initial stress risk factor =  $R_i$

Diffusion stress risk factor =  $R_d$

CTE stress risk factor =  $R_{cte}$

External risk factor =  $R_{ex}$

The growth of whiskers across the gap will be diminished by the presence of conformal coating directly on the tin surface. Therefore, the four factors identifying sources of stress, combined with a conformal coat factor, defined the overall

Equation 3

$$R_{density} = r8a (R_i + R_d + R_{cte} + R_{ex})$$

Investigations into the distribution of whisker lengths that grow from various deposits of tin indicate that some mitigation techniques are effective, not because they necessarily decrease the density of whisker growths, but because they seem to restrict the lengths of the whiskers that do form. Therefore, the length factor is defined as a function of the individual factors representing plating process, substrate composition, and post plate heat treatment as follows:

Equation 4

$$R_{length} = (r_3 r_5 r_7)$$

Combining equations 1-4,

Equation 5

$$R_{total} = K + log_{10} ((R_{primary} \bullet R_{secondary}) \{(r_3 r_5 r_7) [r_{8a} (R_i + R_d + R_{cte} + R_{ex})]\})$$

Each of the six  $R_x$  remaining values in Equation 5 are calculated based upon attributes of the application.

$$\begin{split} R_{primary} &= f \; \{r_1, \, r_{8b}\} \\ R_{secondary} &= g \; (R_{length}, \, r_{10}, \, r_{11}, \, r_{12}) \\ R_i &= h \; \{r_2, \, r_3, \, r_4, \, r_5, \, r_7\} \\ R_d &= l \; \{r_2, \, r_5, \, r_7\} \\ R_{cte} &= m \; \{r_2, \, r_6\} \\ R_{ex} &= n \; \{r_2, \, r_9\} \end{split}$$

Functions are f, g, h, l, m, and n. These functions are simple products and could be redefined later if data indicates a different type of relationship applies.

The net result of the calibration process is that all of the documented failures yield a score of 8.99 or higher, while applications where the SMEs generally agreed that tin was suitable for use score below the range of 7.0–7.5.

These scores are typically compared against the threshold value that is agreed upon as appropriate for the reliability requirements of the system in question. In the context of system-level controls in accordance with GEIA-STD-0005-2, a threshold value of 7.5 is recommended for use with Tin Control Level 2B, and a threshold value of 7.0 is recommended for use with Tin Control Level 2C.

# 2.4.4 SpaceX Solder Replacement Stance

The most effective tin whisker mitigation strategy is to replace all the lead finish on a component with a Sn/Pb finish. This is done through dipping the component in molten solder with a sufficient Pb content. With coverage validation, many standards, including GEIA-STD-0005-02, consider the part to be a lead-free part susceptible to whisker growth. This is a commonly used process for hermetic components and passives that are tolerant to the solder dipping, such as ceramic capacitors. The problem with plastic encapsulated microcircuits is that the potting material will crack or melt when exposed to molten solder. For this reason, hand dipping PEMs in a solder bath is not recommended.

SpaceX considers the solder dipping of PEM components to be an unnecessary risk for FTS and other critical components as it is trading a known risk that is understood and which can be mitigated with one that is unknown and highly variable.

## 2.4.4.1 Conformal Coating

Conformal coating provides board-level defense against tin whiskers. The coating reduces the risk of whisker failures in the following ways:

- Reduces whisker quantity

- Whiskers must break through the conformal coating at the source

- Whiskers must penetrate the conformal coating on the destination contact (effective if entire board is coated)

- Reduces the risk of detached whiskers (FOD) causing a short between contacts

SpaceX currently uses thick conformal coating as its primary whisker mitigation on all assemblies. The circuit assemblies are coated with a 2 mil ( $\pm 1$  mil) Urethane conformal coat. This mitigation strategy is based on the work of Panashchenko at GSFC where they have conducted a long-term (11 years) study of the effect of very thick conformal coatings on whisker growth. A 2 mil ( $\pm 1$  mil) urethane conformal

coating was applied to test samples comprised of tin plated brass (known to be a high whisker risk material). The control areas without conformal coating produced whiskers with a density of approximately 50 whiskers/mm² while the coated areas showed no whiskers had penetrated the conformal coating after 11 years. The thick coating is effective because the whiskers that do grow lift a small amount of the conformal coat, but reach their Euler buckling point before they can break out of the coating. The thick coatings, as well as much thinner applications, protect the destination lead from a short, because the depth any whisker can penetrate before bucking is proportional to the inverse square of the whisker length.

For the NASA COTS/CRS programs, such as the Falcon 9 launch vehicle and the Dragon spacecraft, SpaceX is utilizing thick conformal coating as the tin whisker mitigation approach.

## 2.4.4.2 Proposed Lead-Free Mitigation Plan

SpaceX proposes the following lead finish piece parts plan:

- When available, SpaceX will procure components that are produced with an approved low whisker risk finish. The following are proposed as low risk finishes that are appropriate for use in an FTS:

- Tin with greater than 3% lead

- Nickel palladium

- Nickel palladium with a gold flash

- Gold

- Other finishes with specific approval

- All non-DSCC approved components, or those procured from non-DSCC approved distributors, having a Sn/Pb-based lead plating will be tested as part of lot acceptance DPA to insure that the finish contains >3% Pb

- All components that do not utilize a low-risk finish as described above, as well as any Sn/Pb finished component containing <3% Pb, will be handled in accordance with GEIA-STD-0005-2, Level 2C through the following:

- A risk and mitigation report will be generated for each component

- At least two mitigation techniques from two different categories will be implemented, as identified in GEIA-STD-0005-2

- An analytical assessment of the overall risk shall be conducted by using the Pinsky Method

calculation to ensure that the overall risk is less than or equal to a 7.00 on the Rev. D

calibrated scale

- At the board level, the following steps will be taken for all components to reduce the risk of whisker growth as well as the risks of a whisker-induced failure:

- Sn63Pb37 solder will be used for all components

- Entire board will be conformal coated with a 2 mil conformal

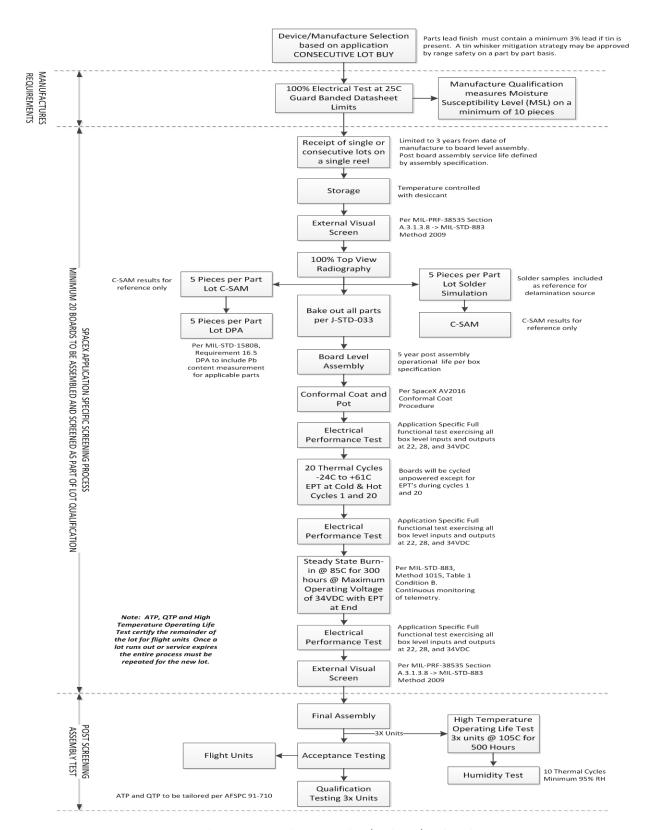

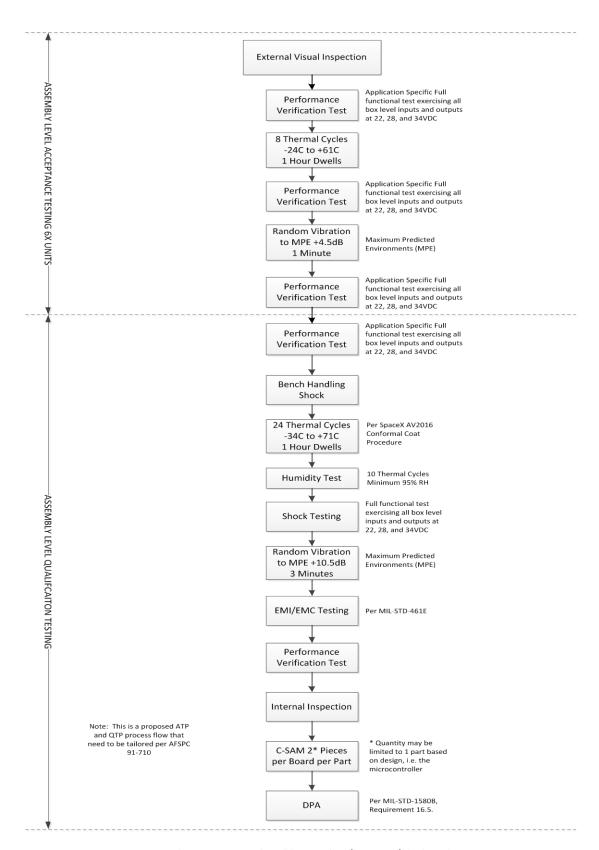

SpaceX proposes the following screening (100% test) and qualification (lot testing) flows for launch systems (Figures 2.4.4-1 and 2.4.4-2).

Figure 2.4.4-1. SpaceX proposed screening flow (100% test) for launch systems.

Figure 2.4.4-2. SpaceX proposed qualification flow (lot testing) for launch systems.

### 3.0 MEDICAL ELECTRONICS PARTS QUALIFICATION PROCESSES

# 3.1 Medtronic's Electronics Parts Qualification Processes [6,7,8]

Medtronic's major product base is implantable medical devices. As seen in many devices discussed in this report, the qualification approach is driven by the application market and its concerns.

Among the implantable electronics devices made by Medtronic are:

- Pacemakers (Implantable Pulse Generators-IPG)

- Implantable Cardiac Defibrillators (ICD)

- Neurological stimulators for pain and functional disorders

- Implantable drug pumps (insulin)

- Implantable pulse monitors

Among the external electronic devices made by Medtronic are:

- Automated External Defibrillators (AED)

- Glucose meters and insulin pumps

- Cardiac surgery devices

Medtronic also makes non-electronic products including:

- Coronary stents

- Heart valves

- Spinal products

- Ear, nose, and throat surgical equipment

Medical electronics infrequently use standard off the shelf electronics due to constraints such as ultra-low power, very small size, and unusual/unique functionality. Therefore the device manufacturer must often qualify internal electronic parts.

Medical devices are highly regulated according to three FDA classes:

- Class I: Devices that interact minimally with patients (tongue depressor, bandage, hearing-aid)

- Class II: Devices that have moderate interaction with patients and have a low probability of harm (X-ray machines, spinal hardware)

- Class III: Devices that interact with patients in a chronic setting or have the possibility of serious injury or death if they malfunction (pacemaker, automated external defibrillator)

Classes II and III device manufacturers must inform the regulatory agencies (e.g., the FDA) of significant changes or data (such as returns or field anomalies). Regulatory agency involvement in product qualification activities is significant.

Global regulatory requirements vary:

- U.S.A. (FDA)

- Japan (MHLW)

- Europe (TUV)

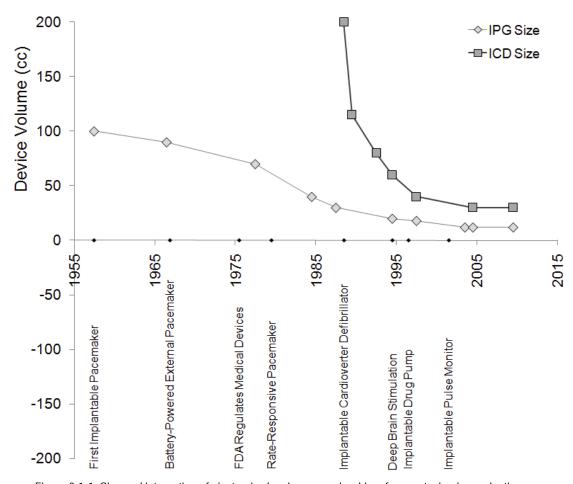

Figure 3.1-1. Size and integration of electronics has been a major driver for new technology adaption.

Medical electronics must make aggressive use of high levels of integration and CMOS scaling since greater intervention to extend useful human life and productivity is being necessitated by aging First world populations and a smaller ratio of client populations to populations "paying" for medical care [9]. More choices of medical care are being influenced by the payer (insurance) and not just the doctor. These considerations drive medical electronics that increasingly provide a wealth of internal sensor data, which must be analyzed and categorized before being made available to the medical professional for assessment. This immediately drives medical electronics into the microwatt and nanowatt power dissipation regimes. This lower power requirement also lengthens the time between procedures to implant the devices or replenish them. For these reasons, implantable medical devices frequently work in the sub-threshold CMOS regime. Furthermore, this means that reliability evaluation and qualification of such devices is qualitatively different, in that small increases in power supply current may actually be functional failures. This means that IDDQ tests/measurements/statistical evaluations have greater significance and must be more closely monitored during qualification and reliability characterization, including at the wafer and wafer foundry level.

Medtronic uses a variety of approaches to cope with the rapidly changing technology landscape:

- Integration of supplier design systems with Medtronic expertise is essential

- Internally developed requirements supplemented or modified with industry standards

- Dialog with external experts shortens learning cycles

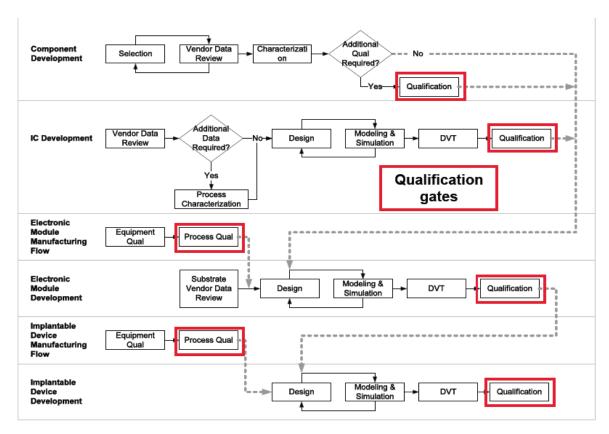

Figure 3.1-2. Qualification of manufacturing processes and components serve as gates before each successively more complex system is qualified.

Table 3.1-1. Qualification test protocols are based upon failure mechanisms of concern.

| Failure Mechanism                                                             | Accelerating Stresses                     | Qualification Test                                                                       | Applicable To                              |

|-------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------|

| Cautery/Defib Damage                                                          | Voltage                                   | Saline tank high-voltage pulse testing                                                   | Final device                               |

| Ceramic Capacitor Cracking                                                    | Mechanical stress                         | Vibration testing, 4-point bend, drop testing                                            | Electronic module                          |

| CMOS Failure Mechanisms (SILC, NBTI, TDDB)                                    | Temperature, voltage                      | HTOL                                                                                     | CMOS-integrated circuits                   |

| Component Fracture Inside Final Device                                        | Pressure                                  | Barometric pressure testing                                                              | Final device                               |

| Corrosion                                                                     | Temperature, RH,<br>contaminants          | Hermetic environment of implantable device makes this an insignificant failure mechanism | N/A                                        |

| Creep                                                                         | Mechanical stress,<br>temperature         | HTOL                                                                                     | Electronic module, final device            |

| Current Leakage Increase Due to Component Degradation                         | Temperature, voltage, ambient environment | HTOL, bias/environmental testing                                                         | Component, electronic<br>module            |

| Delamination  Humidity, contamination  temperature cycling, mechanical stress |                                           | HTOL, temperature cycling,<br>85/85, vibration testing,<br>4-point bend                  | Component, electronic module, final device |

| Failure Mechanism                                                                | Accelerating Stresses                              | Qualification Test                                                                                                                                                                                      | Applicable To                              |

|----------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Dendritic Growth                                                                 | Temperature, voltage,<br>differential              | Hermetic environment of implantable device makes this an insignificant failure mechanism                                                                                                                | N/A                                        |

| Electromigration                                                                 | Current density, temperature, temperature gradient | IC level conducted by foundry. This is generally not a failure mechanism of concern in implantable cardiac devices due to low current densities. Neuromodulation devices may require additional testing | Component, electronic module, final device |

| ESD Damage                                                                       | Voltage                                            | ESD testing                                                                                                                                                                                             | CMOS electronics, electronic module        |

| Fatigue Cracking                                                                 | Mechanical stress, strain range                    | Vibration testing, 4-point bend,<br>drop testing, low frequency/low<br>amplitude repetitive cycling                                                                                                     | Electronic module, final device            |

| High-voltage Component Failure                                                   | Temperature                                        | Repetitive defibrillator charge/discharge cycling                                                                                                                                                       | Electronic module, final device            |

| Intermetallic Formation (e.g., purple plague)                                    | Temperature                                        | HTOL                                                                                                                                                                                                    | Electronic module                          |

| Popcorning Due to Moisture<br>Absorption (plastic packages<br>or epoxy overmold) | Temperature                                        | MSL testing                                                                                                                                                                                             | Component, electronic<br>module            |

| Radiation Degradation                                                            | Radiation intensity                                | X-Ray radiation testing, MRI susceptibility, CT testing                                                                                                                                                 | Component, electronic module, final device |

| Soft Error Upset Particle impingemen                                             |                                                    | Alpha foil, neutron beam, proton beam, heavy ion testing                                                                                                                                                | Component, electronic module               |

Electrical characteristics that are important to commercial devices may or may not be significant to implantable medical devices. For example, standby current for SRAMs increases significantly at temperatures lower than about 10°C. At first one might think that standby current would therefore not be a problem in an implantable medical device. However, a battery operated pacemaker turned out to have a large fallout after shipment. This was caused by sub-zero conditions in airplane transit, which depleted the batteries inside the medical device. A counter-example would be 'popcorn' noise in precision analog electronics where commercial applications demand low noise. Medical applications also demand low noise, since popcorn noise may be on the same order of magnitude as some physiological signals. Bias currents in some low power circuits may not provide enough noise margins. These considerations emphasize that electrical testing during qualification must be more comprehensively tailored to the medical device application.

Failure mechanisms have a different significance for most medical applications, so tailoring the qualification tests used is required. The various failure mechanisms of concern and their significance for medical applications are listed here:

- Electro-migration: exponential dependence on temperature (i.e., worse at higher temperatures) and inverse square dependence on current density—lower power applications will reduce any electro-migration risk and designs are optimized for minimal junction temperature.

- Hot carrier injection: gate and substrate currents increase failure rate by power laws; temperature increases degrade time to failure by the usual Arrhenius equation—drain engineering across all technologies has made this a non-issue.

- Bias temperature instability: impacts both n- and p-channel devices; several models, including reaction-diffusion and charge trapping/detrapping; is not significant for medical devices since this effect is decreased at low power and voltage.

- Mechanical failure mechanisms: stress migration mitigated by reliability design rules, low temperature; temperature cycling concerns for large temperature swings in automotive and highperformance desktop computing are non-issues for medical electronics (Coffin–Manson model frequently used), hot spots mitigated during design process.

- Intrinsic oxide reliability (Time- Dependent Dielectric Breakdown): not a concern for medical electronics since wear-out under ultra-low power is mitigated by low voltage and low electric field.

- Ultra-thin oxide reliability: soft breakdown may be present due to current drain increase; Stress-Induced Leakage Current (SILC) may be a concern.

Since wear-out failure mechanisms are of much less concern for ultra-low powered implantable medical devices, screening and infant mortality considerations correspondingly become more important. At the wafer level, IDDQ testing—including statistical analysis of this parameter for outlier chips—becomes an important strategy. The medical electronics industry is cautious about allowing application usage of good die in bad neighborhoods. Over-voltage stress (that is, above the circuit application voltage, which will be low) may be used before IDDQ evaluation to screen out marginal chips. Components or modules (above chip level) typically use high temperature reverse bias burn-in as a screen and multiple temperature cycling screening to accelerate infant mortal defects. Repeated therapy delivery cycles is an application-related method to reduce infant mortality risks.

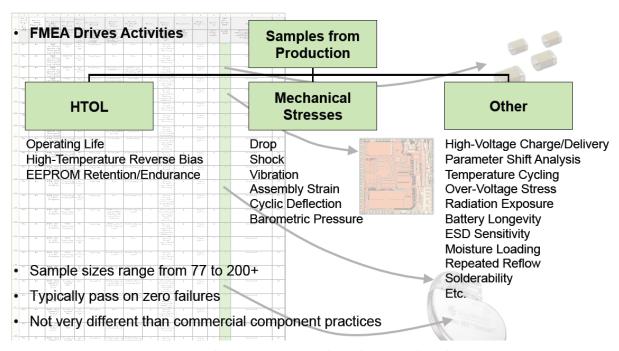

Figure 3.1-3. Qualification sequences and sample size are driven by FMEA.

Outlier IDDQ die signatures behave differently than good die signatures. Outlier value distribution may be indicative of latent defects. Intel has reported that they had order-of-magnitude higher burn-in failure rates from risky die population compared to the remainder of die.

# 3.2 Texas Instruments (TI) Proposed Application-Based Qualification Methodology for Medical ICs [10]

Traditional stress-driven qualification test programs (MIL-STD-883, Test Methods and Procedures for Microelectronics, and JEDEC JESD47, Stress-Test-Driven Qualification of Integrated Circuits) are not optimized for economical design and rapid product qualification for medical electronics. The application conditions of medical devices vary significantly and are, in general, radically different than conditions found in traditional aerospace high-reliability markets. For example, some medical applications are short duration, while chronic disease treatment monitoring systems are long duration. Few medical applications have the extremes of temperature, vibration, and mechanical shock that are typical of aerospace applications. To appropriately tailor the qualification for medical applications, a detailed analysis of the usage conditions is required early in the process. Often these usage conditions consist of a series of different environments of voltage, temperature, and frequency. TI models these conditions in the generalized form:

$$1 = \int \frac{dt}{t_{life}(V_{stress}, Temp)}$$

This equation is rewritten in a discrete form and the equivalent lifetime (teqlife) after a series of voltage and temperature stresses is expressed as

$$t_{eqlife} = \sum_{i=1}^{N} t_i = \frac{1}{\sum_{i=1}^{N} \frac{t_i}{\sum_{i=1}^{N} t_i} * \frac{1}{t_{life}(V_i, T_i)}}$$

where  $t_i$  is the time duration under each stress condition and  $t_{life}$  is the lifetime at the stress level of Vi and Ti (voltage and temperature stresses).

This equation can be used to tailor the various test times during a qualification process provided the functional relationship of lifetime and voltage or temperature is known (for example, the familiar Arrhenius equation). In an obvious way the traditional test results of high temperature operating life test or voltage stress ramp tests may be used to qualify a medical application where the temperature, durations, and voltage stresses can be measured.

# 3.3 Automotive Parts Qualification Processes<sup>5,6</sup>