# Single-Event Effect Performance of a Commercial ReRAM

Dakai Chen<sup>1</sup>, Hak Kim<sup>2</sup>, Anthony Phan<sup>2</sup>, Edward Wilcox<sup>2</sup>, Kenneth LaBel<sup>1</sup>, Stephen Buchner<sup>3</sup>, Ani Khachatrian<sup>4</sup>, and Nicolas Roche<sup>5</sup>

- 3. Naval Research Laboratory, Washington, DC 29375

- 4. Sotera Defense c.o. Naval Research Laboratory, Washington, DC 29375

- 5. George Washington University c.o. Naval Research Laboratory, Washington, DC 29375

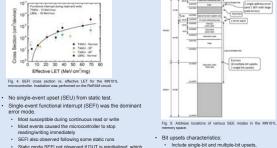

Abstract: We show heavy ion test results of a commercial production-level ReRAM. The memory array is robust to bit upsets. However, the ReRAM system is vulnerable to SEFI.

#### INTRODUCTION

Non-volatile memories are widely used in space systems for data and code storage However options for radiation-tolerant memories are limited. The storage. However, options for radiatori-tolerant memories are limited. The commercial demand for high-density mass-storage electronic devices has driven the rapid development of floating-gate flash memories to its scaling limits. The International Technology Roadmap for Semiconductors named Reduction-Oxidation Random Access Memory (ReRAM) as a promising candidate to replace flash [1]. The ReRAM structure consists of a metal-oxide insulator (TaO<sub>x</sub>, HfO<sub>x</sub>, TiO<sub>x</sub>, etc.) between a top and bottom electrode. In TaO systems, an applied electric field creates an electrochemical reaction which dissociates anions  $(O^2)$  at the top or bottom electrode. The oxygen vacancies can migrate across the insulator to form a conductive link between the electrodes. An electric field of opposite polarity breaks the conductive link.

The ReRAM is naturally hardened against ionizing radiation, since it does not store charge. Previous studies have shown that the ReRAM structure can be hardened up to several Megarad(Si) of total ionizing dose (TID) and up to 10<sup>14</sup> ions/cm² of proton fluence [2]–[4]. However, there is currently no knowledge on the single-event effect (SEE) performance of ReRAM, Furthermore, the existing published data have only evaluated test structures or memory arrays.

The circuit level response can include unique error modes with significant impact to device operation [5]-[7]. In this study, we investigate the SEE performance of a commercial production-level ReRAM

#### **DEVICE DETAILS**

10 years at 85°C

Data Retention

Seabrook, MD 20706

# Acid etched TOEP080-P-1212F plastic case and

exposed the entire die surface

Collimator exposed only the ReRAM

1. NASA Goddard Space Flight Center, code 561, Greenbelt, MD 20771

2. ASRC Space and Defense c. o. NASA Goddard Space Flight Center.

**EXPERIMENTAL DETAILS**

- Created a "window" in a kovar lid using an Ultra-Tech ASAP-1® surface preparation machine. Kovar collimator approximately 10 mils (254 µm), which stops the majority of the test facility heavy

- ion energy spectrum.

The collimator shields other components of the microcontroller aside from the ReRAM, such as the static random access memory (SRAM), logi

#### Irradiation Facilities

- 15 MeV/amu heavy ions at Texas A&M University (TAMU), in air . Used Panasonic's evaluation board as test vehicle 16 MeV/amu heavy ions at Lawrence Berkeley National

- 590 nm pulsed-laser at the Naval Research Laboratory

- Total Energy (MeV) LET (MeV·cm²/mg) Range in Si (μm) Kr (TAMID 21.2

### **Test Conditions**

- · Vcc = 3.3 V, Frequency = 8 MHz or DC

- · Test modes:

- Static

Continuous read

- Continuous read/compare/write Continuous write

- · Data patterns: 00. FF. 55, and AA

- Actively monitored the light emitting diode (LED) indicator that is connected to the I/O address registers via current probes. The indicator signals the functionality of the

## **RESULTS**

- · Static mode SEFI not observed if DUT is reinitialized, which clears address buffers

- No column, page, or block errors as commonly observed in

- · Similar cross sections for read and write test mode.

- Angular effects due to beam shadowing from the kovar collimator. Degraded beam produced cross section >5× relative to angular beam at same effective LET.

- · Error address locations distributed throughout the rocontroller memory bank, and

- krad(Si)).

#### 8 SEUs in the ROM. 1 locked mode event possibly due to SEU triggering device security function, 1 part failed functionally (5

# **RESULTS**

- Probed the ReRAM array and surrounding peripheral circuits with a 20× lens with a beam diameter of 1.7 µm to identify the sensitive regions.

- Different sensitive regions are shown on the left with respective upset energy thresholds. No errors were found from the ReRAM array.

- Most sensitive region, which consists of sense amplifier circuit, was investigated further with a 100× lens, with a beam diameter of 0.9 µm, and the energy was fine-tuned to determine the upset energy threshold (Fig. 7).

- Energy threshold at Location 1 (Fig. 7) was comparable to heavy ion results.

- Read mode: 5.5 pJ (17 MeV·cm²/mg): Write mode: 8.6 pJ (26.5 MeV·cm²/mg) SEFI memory addresses and error characteristics from laser test are similar to those from heavy ion test.

- . Continuously reading out errors from the ROM.

- . Stuck reading at end of Bank0 (FFFF), and

# DISCUSSION

Bit errors are an important part of the SEE response for floating-gate non-votatile flash memories, particularly for multiple-level cell devices, where multiple-bit upsets make up a significant portion of the overall radiation-induced bit upset fare [6]. The scaling potential of RRGMA raises additional questions about its multiple-bit upset enastively, which worsens with diminishing device idmensions. The results presented here show that the ReRAMI array in the MNTOIL microcorroller is externely robust against heavy ion irradiation. We did not observe any ion-induced bit upsets during either the statio or dynamic test modes. The access translation in the TIRI architecture are susceptible to SEUs. However, the lest results showed that the memory array is hardered against errors due to access translation upsets, kelly owing to the bipotal organity and the off the ReRAMI are set affects experienced against errors due to access translation upsets, kelly owing to the bipotal organity and upset of the ReRAMI are Set and reset states require polar proposels potentials. for operation. The access transistor controls the voltage potential at one electrode, while the bit line controls the potential at the other electrode. Switching between states requires a change in the voltage potential at both terminals. Therefore, a SEU from the access transistor alone is insufficient to cause an incorrect write/read to the RePAM provided that the signal on the bit line remains

SEFI dominated the SEE response. Pulsed-laser testing identified the sense amplifier circuit as a sensitive region for SEFs. SEU in the sense amplifier circuit caused some of the microcontroller hangups. The SEFI error ross sections are similar for the read and write mode. The response differs from SEFs occurring in flash memories, where the cross sections from program or researe the pically different than that from the read mode [5]. [7]. This is partly due to the similar voltage levels required for a read or write operation in ReRAM technology. The lower voltage level required to perform erase or write eliminates the need for charge pumps and reduces the circuit complexity. The elimination of charge pumps is particularly beneficial for the part's radiation tolerance. Charge pumps are especially susceptible to total ionizing dose and destructive single-event effects.

Many factors aside from radiation would need to be considered for actual space flight applications. Here, we evaluate the on-orbit event rate of the SEFIs. We used a maximum likelinds on the best if are: LET $_{\rm i} = 2$  MeV crafting, saturating cross section of normal incident irradiation as shown in Figure 2 [I]. The Webbull ift parameters for the best ift are: LET $_{\rm i} = 2$  MeV crafting, saturating cross section - 68  $\times$  10<sup>-4</sup> cm². W = 370, and S = 2. The corresponding heavy ion event rate for an orbit similar to the international space station is approximately 1.6  $\times$  10<sup>-4</sup> cupset per discussion. The section of the RePAMI area is minumate to upsets makes the RePAMI area is similar to the international space station is approximately 1.6  $\times$  10<sup>-4</sup> cupset per discussion. The suitability of RePAMI area is prapare flight will be partly determined by the application tolerance to the SEFI enter rate, which depends on the SEE sensitivity of the CMOS peripheral crusts.

# CONCLUSION

We have investigated the single-event effect performance of the embedded ReRAM in the MN101L microcontroller. We observed a total of 15 SEUs from the heavy ion test, which included single-bit and multiple-bit upsets. A pulsed-laser test confirmed that the SEUs did not originate from the ReRAM array. Therefore, the ReRAM array is immune to ion-induced upsets up to LETs as high as 70 MeV·cm²/mg. We also found that the CMOS access transistors, although theoretically susceptible to SEUs, do not necessarily lead to upsets in the array. We believe that this is due to the operating principal of the ReRAM cell, where polar opposite potentials are required to set or reset the memory.

Single-event functional interrupt dominated the SEE response of the MN101L. Pulsed-laser testing showed that the sense amplifier contained vulnerable circuits sensitive to SEU, which can lead to functional interrupt of the microcontroller. However, the pulsed-laser may be limited by penetration range. So there are likely other CMOS structures in the peripheral circuits that are susceptible to heavy ions.

Nevertheless, the SEFI error rate for this device is relatively low However, the consequence is significant, since each SEFI requires a reset or power cycle for recovery. The ReRAM cells appear to be intrinsically hardened against heavy ion-induced ionization effects. The effects of scaling on the radiation hardness are yet to be seen; the progression of this technology depends on its scaling potential.

Regardless, the performance of the ReRAM technology in the space environment will be largely determined by the SEE susceptibility of the peripheral control circuits. The lack of charge pump circuits serves to reduce power and minimize size, while also enhancing the device's radiation tolerance to TID and destructive SEE.

# **ACKNOWLEDGEMENT**

This work was supported in part by the NASA Electronic Parts and Packaging (NEPP) Program and the Defense Threat Reduction Agency (DTRA) under IACRO DTRA10027-8002 to NASA. The authors would like to thank Panasonic for technical exchanges

# REFERENCE

- 1. ITRS, "International Technology Roadmap for Semiconductors," 2001 and 2011 Editions: Imply with an Intelligence of the Control of the Con

- p. 2300-2372, Dec. 2003. R. Oldham, M.R. Friendlich, A. B. Sanders, C. M. Seidleck, H. S. Kim, M. D. Berg, and N. Olinami, N.K. Pinematon, A. B. Sarioes, C. M. Sedieck, P. S. Nim, D. Berg, and K. A. Läßel, "TID and SEE response of advanced Samsung and Micron 46 NAMD flash memories for the NASA MMS mission," IEEE Radiation Effects Data Workshop Record, pp. 114-122, Jul. 2009. http://www.semicon.panasonic.co.jp/en/products/microcomputers/mn1011

- ntp://www.semicon.panasonic.co.jpeniproducts/microcomputers/min to tr R. Ladbury, "Statistical properties of SEE rate calculations in the limits of large and small event counts," *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 2113 2119, Dec. 2007.

To be presented by Dakai Chen at 2014 Institute of Electrical and Electronics Engineers (IEEE) Nuclear and Space Radiation Effects Conference (NSREC) Paris, France, July 14-18, 2014.