National Aeronautics and **Space Administration**

# Software Graphics **Processing Unit (sGPU)** for Deep Space Applications

**PROJECT MANAGEMENT** Mary McCabe 281.483.5720 or mary.e.mccabe@nasa.gov George Salazar 281.483.0162 or <u>george.a.salazar@nasa.gov</u>

HAT: 4.5.a, 4.7.c, 6.3.b TA: 04 Onboard Computing; 06 EVA, Environmental Monitoring TRL: start 2 / current 5

## **OVERVIEW**

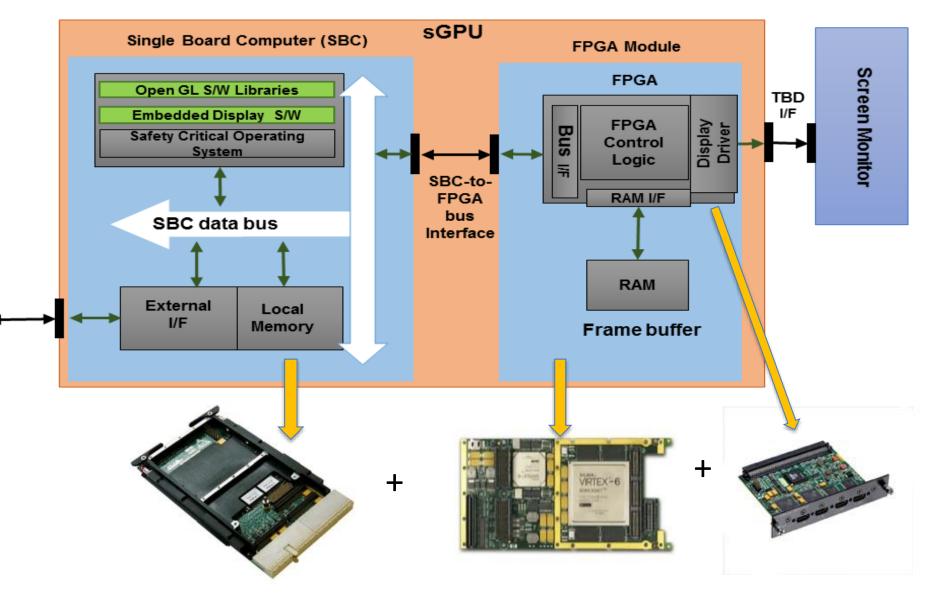

A graphics processing capability will be required for deep space missions and must include a range of applications, from safety-critical vehicle health status to telemedicine for crew health. However, preliminary radiation testing of commercial graphics processing cards suggest they cannot operate in the deep space radiation environment. Investigation into an sGPU comprised of commercial-equivalent radiation hardened/tolerant single board computers, field programmable gate arrays, and safety critical display software shows promising results. Preliminary performance of approximately 30 frames per second (FPS) has been achieved. Use of multi-core processors may provide a significant increase in performance.

## **INNOVATION**

This technology would provide graphics processing capability for the deep space environment.

## **OUTCOME**

To date, approximate performance of 30 FPS has been achieved.

## **INFUSION SPACE**

This technology can be used for both safety-critical and non-critical applications.

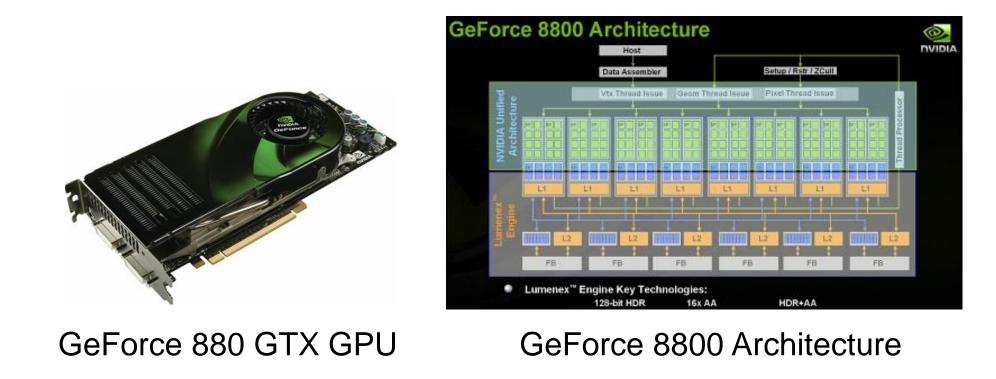

#### **Commercial GPU Architecture Example**

**Display screen before GPU** exposed to radiation beam

Display screen after GPU exposed to radiation beam

### **Commercial GPU Radiation Test**

## **PARTNERSHIPS / COLLABORATIONS**

Partnering with Center for High-Performance & Reconfigurable Computing (CHREC) using a promising multi-core processer designed for the space environment, support from EA, and potential support from STMD.

## **FUTURE WORK**

Explore a customizable multi-core architecture.

- -Investigate and procure a multi-core processor with a path to a High Performance Space Computer (HPSC).

- CHREC Space Processor (CSP)

- -Utilize open source graphics software to keep display graphics development cost low.

#### **Current sGPU Architecture**

2015 IR&D Poster – EISD Technology Showcase

- -Design an FPGA architecture for a multi-core implementation.

- -Test using various graphical display types.

- -Explore use as image processor.