## 2015 Material Science & Technology

8:00 AM October 8, 2015

# Packaging Technologies For 500°C SiC Electronics and Sensors

Challenges in Material Science and Technology

Liang-Yu Chen<sup>1</sup>, Philip G. Neudeck<sup>2</sup>, Glenn M. Beheim<sup>2</sup>, David J. Spry<sup>2</sup>, Roger D. Meredith<sup>2</sup>, and Gary W. Hunter<sup>2</sup>

- 1. Ohio Aerospace Institute/NASA Glenn Research Center, Cleveland, OH 44142

- 2. NASA Glenn Research Center, Cleveland, OH 44135

- Challenges in MS&T

8:00 AM October 08, 2015

### **Outline**

- Background

- 500°C SiC electronics and sensors

- 96% alumina and thick-film metallization based packaging system for 500°C applications

- Quick review of Au thick-film/alumina packaging systems

- Challenges of thick-film/alumina systems

- Co-fired alumina 32-I/O prototype packaging system and test results

- Dielectric performance of selected alumina substrates and HTCC alumina material at high temperatures

- Impurity effects on alumina dielectric performance and material requirements for packaging performance

- Summary and Challenges

- Challenges in MS&T

8:00 AM October 08, 2015

## **Background**

500°C SiC electronics and MEMS sensors have been demonstrated

- JFETs and JFETs based circuits demonstrated at NASA GRC

- MEMS based pressure sensors and Schottky diode based gas chemical sensors developed at NASA GRC

- Applications include aerospace engine control and long term Venus probes

- Packaging material issues

96% alumina and thick-film metallization based prototype packaging system for 500°C SiC electronics and sensors

- 96% alumina provides acceptable electric/dielectric properties at high temperatures up to 550°C

- The system composed of chip-level package, printed circuit board (PCB), and edge-connector

### Co-fired Pt/alumina material system

- 32-I/O package and printed circuit board (PCB)

- Initial test results with SiC circuits at 500°C

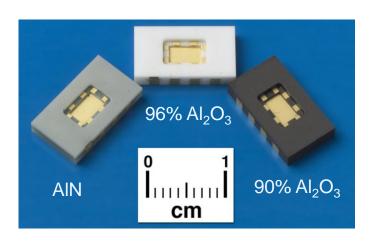

### **Ceramic Chip-level Packages and PCBs**

- Three types of ceramics and Au thick-film metallization based chip-level packages and printed circuit boards (PCBs)

- Chip-level packages characterized between room temperature and 500°C

- An edge connector in development for PCB PCB (subsystem-level) interconnection

- 96% alumina provides best electrical performance at high temperatures

Chen and Hunter, 2005 HiTEN

# Au thick-film and 96% alumina packaging system

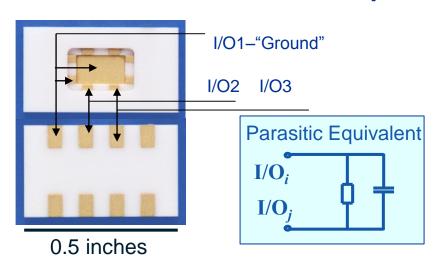

## 96% Alumina Chip-level Packages

Chen and Hunter, 2005 HiTEN

#### Parasitic Capacitance and Conductance of Neighboring I/Os

| T (°C)<br>f (Hz) | $T_R$  | 100    | 150    | 200    | 250    | 300    | 350    | 400    | 450    | 500   | 550    |

|------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|

| 100              | 0.00nF | < 5   | 5      |

|                  | 0.00   | 0.00   | 0.00   | 0.00   | 0.00   | 0.00   | 0.00   | 0.00   | 0.005  | 0.00  | 0.00   |

| 120              | 0.5    | 0.5    | 0.5    | 1      | 1      | 1      | 1.5    | 1.5    | 1.5    | 1.5   | 2      |

|                  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.0005 | 0.001 | 0.001  |

| 1K               | 0.5    | 0.5    | 0.5    | 0.5    | 0.5    | 0.5    | 0.6    | 0.7    | 0.7    | 0.8   | 0.95   |

|                  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.000  | 0.001  | 0.001  | 0.002 | 0.0025 |

| 10K              | 0.49   | 0.50   | 0.50   | 0.490  | 0.49   | 0.52   | 0.53   | 0.58   | 0.59   | 0.65  | 0.69   |

|                  | 0.001  | 0.000  | 0.000  | 0.000  | 0.000  | 0.001  | 0.002  | 0.003  | 0.004  | 0.006 | 0.008  |

| 100K             | 0.492  | 0.486  | 0.497  | 0.493  | 0.487  | 0.517  | 0.539  | 0.535  | 0.563  | 0.585 | 0.57   |

|                  | 0.005  | 0.006  | 0.0015 | 0.002  | 0.003  | 0.005  | 0.007  | 0.011  | 0.015  | 0.022 | 0.030  |

| 1M               | 0.501  | 0.497  | 0.485  | 0.506  | 0.499  | 0.529  | 0.533  | 0.55   | 0.556  | 0.544 | 0.55   |

|                  | -      | -      | -      | -      | -      | -      | -      | -      | -      | -     | -      |

Usable for packaging of many envisioned low power 500°C devices/ circuits

> > 50°C margin above 500°C

| pF |

|----|

| μS |

# NASA

# Au thick-film and 96% alumina packaging system

#### **Static Thermal Test**

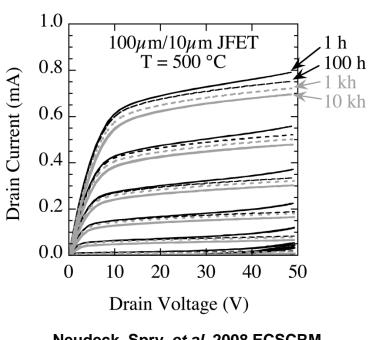

Neudeck, Spry, et al, 2008 ECSCRM

- 96% alumina packaging system chip-level packages and PCB

- less than 7% change in the JFET characteristics in first 6000 hours

- Tested at 500°C for over 10,000 hrs

- Demonstrated for long term operation at 500°C for the first time

# Au thick-film/96% alumina system for pressure sensor packaging

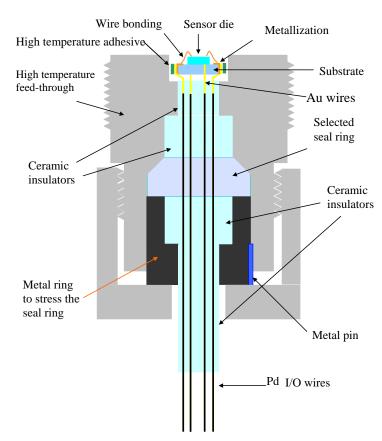

## **Spark - Plug Type Package for High Temperature Capacitive Pressure Sensors**

- 96% alumina substrate with Au thickfilm metallization

- Four 10 mil diameter Au wires (I/Os) attached

- Au wires extended by four Pd wires

- Pd wires sealed in a commercial SS high temperature gland

- The gland operable up to 8000 psi

- Electrically characterized between RT and 500°C

- Low parasitic effects

- May apply to other micro-fabricated solid sensors

Chen, Beheim, Meredith, 2010 HiTEC

# Au thick-film/96% alumina system for pressure sensor packaging

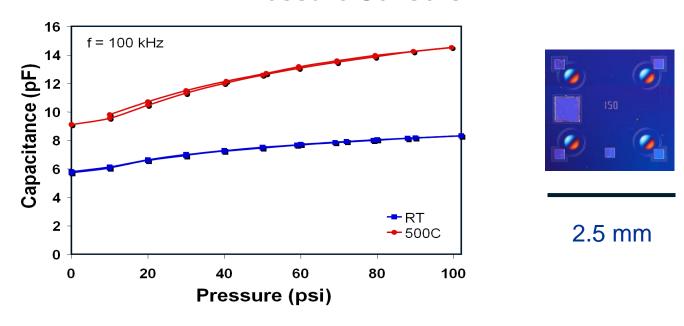

# Spark-plug Type Package for High Temperature Capacitive Pressure Sensors

- Capacitive SiC pressure sensor with four polycrystalline SiC diaphragms electrically connected in parallel

- Measured at 100 kHz

- Packaging parasitic effects subtracted

- Parasitic conductance to be further reduced for packaging other sensors

# **HTCC Pt/Alumina for High Temperature Packaging**

# HTCC Pt/Alumina for High Temperature Packaging

- Au thick-film/96% alumina based packaging system

- Prototype package and PCB long-term tested at 500°C with SiC circuits

- Packages assembled in a research lab a non-mass-production step

- Thermal dynamic stability issue of Au thick-film materials at elevated temperatures

- High temperature co-fired (HTCC) alumina

- Co-fired at T >1500°C

- A few percent of glass used in co-fired alumina systems

- Dielectric performance at high temperatures tested

- Pt metallization

- Chemically stable at high temperatures

- Low CTE (8.8x10<sup>-6</sup>/C°)

- Aluminum oxide for binder Thermal dynamically stable

- Alloy with Au, Au is always surface rich at elevated temperatures

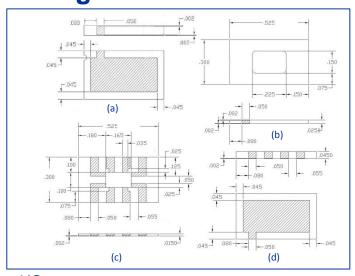

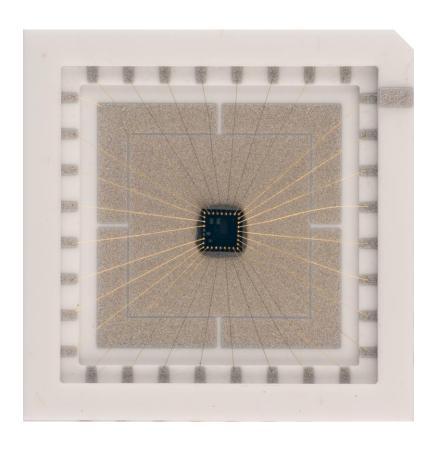

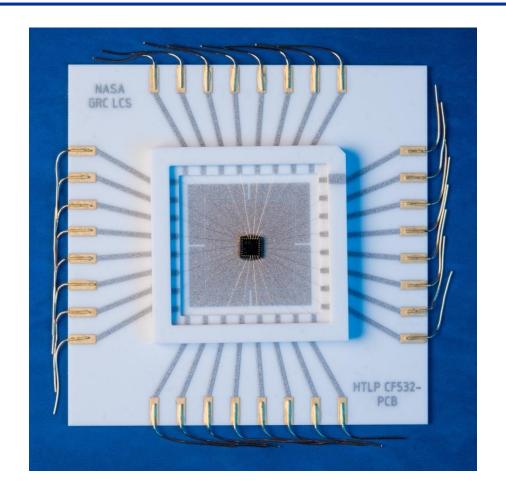

## **Pt/HTCC Alumina Prototype Package**

0 5 | | | | | | | | mm

- Pt/HTCC alumina

- 32-IOs

- For low power circuits

- Via connecting pads

- 1 inch x 1 inch package

- Surface mount

- Preliminarily tested with SiC high temperature ICs

- In characterization/ testing process

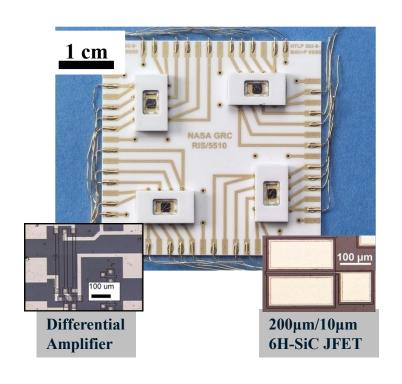

# Pt/HTCC Alumina Prototype Package and PCB

Pt/HTCC alumina PCBs, 2 inch x 2 inch, preliminarily tested with SiC circuits

# Pt/HTCC Alumina Prototype Package and PCB

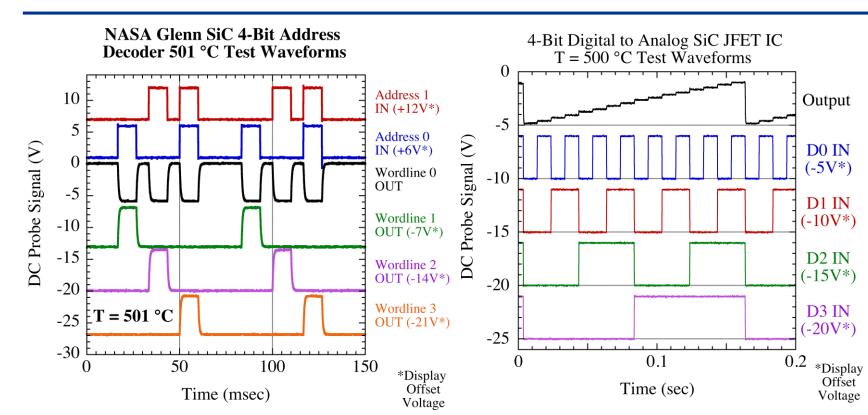

- SiC RAM decoder waveforms

- With 32-IOs HTCC package and PCB

- Initial test data recorded at 501°C

- SiC D/A convertor

- With 32-IOs HTCC package and PCB

- Initial test data recorded at 500°C

G.W. Hunter, P.G. Neudeck, D.J. Spry, G.E. Ponchak, G.M. Beheim et al, Venus Science Priorities for Laboratory Measurements Workshop, April, 2015, Hampton, VA.

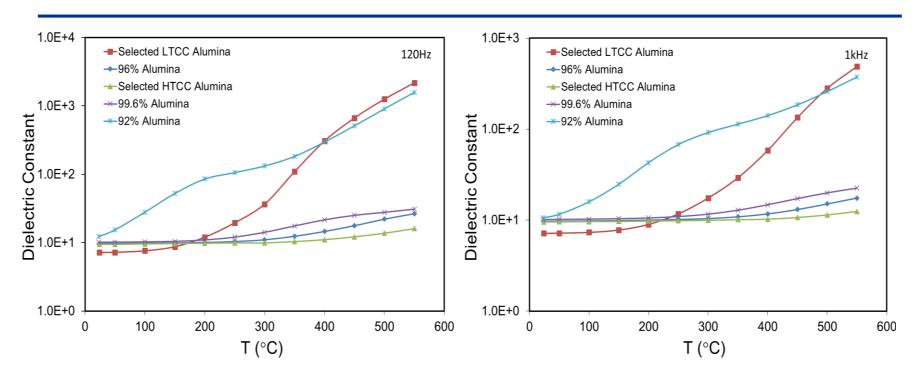

# Dielectric properties of different alumina materials

## Dielectric properties of packaging dielectric at elevated temperatures is critical to parasitic packaging effects

- Low dielectric constant

- Low parallel conductivity

- Low dissipation factor / high quality factor

- Stability with temperature increase

# Dielectric properties of alumina materials

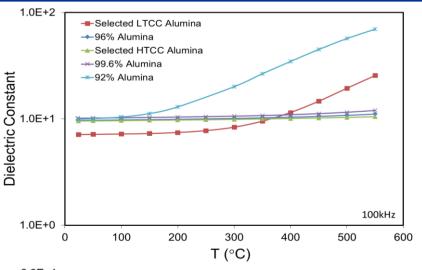

### Compared with 96% alumina:

- Dielectric constants of 92% and 99.6% alumina are higher and increases more at 120Hz and 1kHz

- Dielectric constant of HTCC alumina is lower and increases less at 120Hz and 1kHz

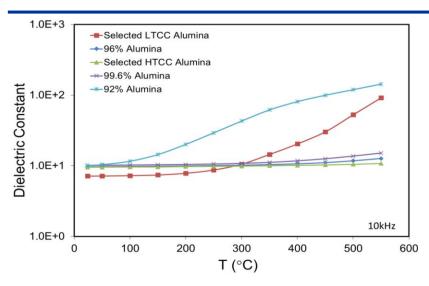

## Dielectric properties of alumina materials

### Compared with 96% alumina:

- Dielectric constants of 92% and 99.6% alumina are higher and increase more at 10kHz, 100kHz, and 1 MHz

- Dielectric constant of HTCC alumina is lower and increases less at 10kHz. 100kHz, and 1MHz

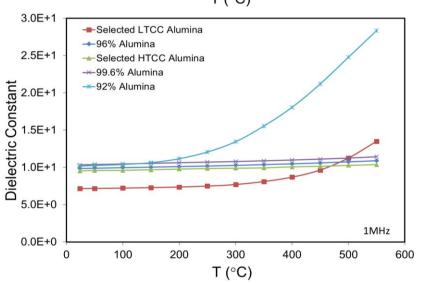

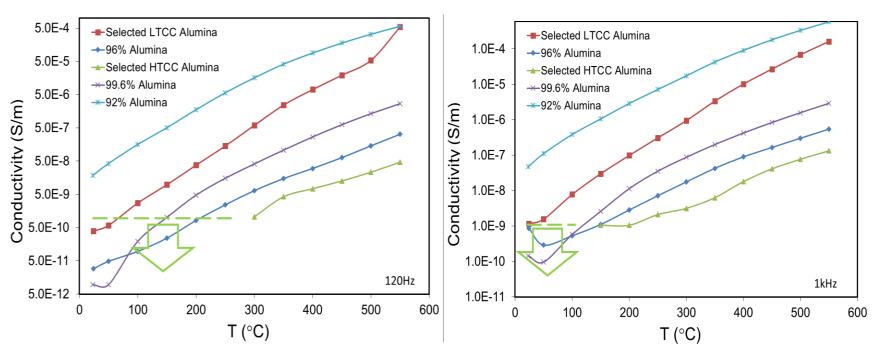

#### Compared with 96% alumina:

- Conductivities of 92% and 99.6% alumina are higher at temperatures above 100°C at the frequencies of 120Hz and 1kHz

- Conductivity of HTCC alumina is ~ an order of magnitude lower at temperatures above 300°C at the frequencies of 120Hz and 1kHz

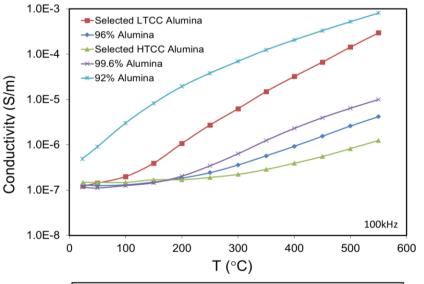

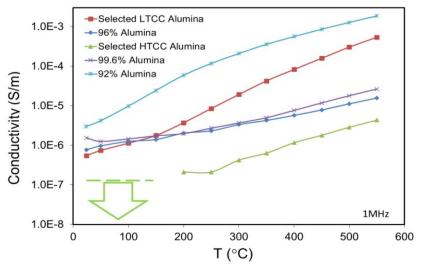

# Dielectric properties of alumina materials

#### Compared with 96% alumina:

- Conductivities of 92% and 99.6% alumina are higher at temperatures above 200°C at the frequencies of 10kHz, 100kHz, 1MHz

- AC conductivity of HTCC alumina is always lower and increases less with T at 10kHz, 100kHz, and 1 MHz at T > 200°C

- Challenges in MS&T

8:00 AM October 08, 2015

## **Summary**

96% alumina substrate and thick-film metallization based packaging systems demonstrated at 500°C

- Au thick-film/alumina chip-level packages and PCBs

- Static thermal test of packaged SiC JFET circuits successfully at 500°C for over 10,000 hours

- ◆ Thermal dynamic stability issue of thick-film binders at elevated temperatures

- Laboratory step involved on package assemble

- Chip level packages not fully commercially fabricated

### Pt/HTCC alumina system

- ♦ Co-fire process more suitable for large scale commercialization

- Alumina binder for Pt metallization more stable at high temperatures

- Dielectric performance of 32-IOs co-fired packages in evaluation

- Prototype package initially tested with SiC circuits at 500°C

- Further development needed

- Challenges in MS&T

8:00 AM October 08, 2015

# **Challenges**

Dielectric properties of alumina materials at elevated temperatures

- Overall 92% HTCC alumina the best

- AC conductivity still increases with temperature

- 96% conventional alumina better than 92% and 99.6% alumina

- Firing agents / impurities, and grain size

- Chemical/electronic states of impurities at grain boundaries

#### Better packaging material systems at high temperatures

- ◆ For higher packaging density, higher operation frequency and temperature

- Understand impurity, grain size, process effects

- Design of new ceramic material with stable dielectric constant and lower dielectric loss at high temperatures

- Co-fired process

- CTE compatible to SiC bigger die

- Metallization scheme for operation at 500°C and above

## Thank You Very Much for Your Attention!

# **Acknowledgements**

Authors thank Lawrence G. Matus, Mary V. Zeller, and Dawn C. Emerson for their contributions. The high temperature packaging research is currently supported by Vehicle Systems Safety Technologies (VSST) project of NASA Aviation Safety program, Convergent Aeronautics Solutions (CAS) Project of Transformative Aeronautics Concepts Projects, and Distributed Engine Control task of the Subsonic Fixed Wing project within the Fundamental Aeronautics Program.