Integrated Power, Avionics, and Software (iPAS) Space Telecommunications Radio System (STRS) Radio User's Guide—Advanced Exploration Systems (AES)

Rigoberto Roche and Mary Jo Shalkhauser Glenn Research Center, Cleveland, Ohio

## NASA STI Program . . . in Profile

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA Scientific and Technical Information (STI) Program plays a key part in helping NASA maintain this important role.

The NASA STI Program operates under the auspices of the Agency Chief Information Officer. It collects, organizes, provides for archiving, and disseminates NASA's STI. The NASA STI Program provides access to the NASA Technical Report Server—Registered (NTRS Reg) and NASA Technical Report Server— Public (NTRS) thus providing one of the largest collections of aeronautical and space science STI in the world. Results are published in both non-NASA channels and by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counter-part of peer-reviewed formal professional papers, but has less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM. Scientific and technical findings that are preliminary or of specialized interest, e.g., "quick-release" reports, working papers, and bibliographies that contain minimal annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION. Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION. Englishlanguage translations of foreign scientific and technical material pertinent to NASA's mission.

For more information about the NASA STI program, see the following:

- Access the NASA STI program home page at http://www.sti.nasa.gov

- E-mail your question to help@sti.nasa.gov

- Fax your question to the NASA STI Information Desk at 757-864-6500

- Telephone the NASA STI Information Desk at 757-864-9658

- Write to: NASA STI Program Mail Stop 148 NASA Langley Research Center Hampton, VA 23681-2199

Integrated Power, Avionics, and Software (iPAS) Space Telecommunications Radio System (STRS) Radio User's Guide—Advanced Exploration Systems (AES)

Rigoberto Roche and Mary Jo Shalkhauser Glenn Research Center, Cleveland, Ohio

National Aeronautics and Space Administration

Glenn Research Center Cleveland, Ohio 44135

Trade names and trademarks are used in this report for identification only. Their usage does not constitute an official endorsement, either expressed or implied, by the National Aeronautics and Space Administration.

Level of Review: This material has been technically reviewed by technical management.

Available from

NASA STI Program Mail Stop 148 NASA Langley Research Center Hampton, VA 23681-2199 National Technical Information Service 5285 Port Royal Road Springfield, VA 22161 703-605-6000

This report is available in electronic form at http://www.sti.nasa.gov/ and http://ntrs.nasa.gov/

| Sum  | mary   |                                                                                            | 1  |

|------|--------|--------------------------------------------------------------------------------------------|----|

| 1.0  | Intro  | duction                                                                                    | 1  |

|      | 1.1    | System Overview                                                                            | 1  |

|      | 1.2    | Document Overview                                                                          | 1  |

| 2.0  | Desi   | gn Overview                                                                                | 1  |

|      | 2.1    | General Purpose Module (GPM)                                                               | 2  |

|      | 2.2    | Signal Processing Module (SPM)                                                             | 3  |

|      | 2.3    | Radiofrequency Module (RFM)                                                                | 3  |

|      | 2.4    | Top-Level Design Description                                                               | 3  |

|      | 2.5    | Concept of Operation                                                                       | 3  |

| 3.0  | Gen    | eral Purpose Module (GPM)                                                                  | 4  |

|      | 3.1    | Software Control Description                                                               | 4  |

|      | 3.2    | Verifying Correct Interface Configuration                                                  | 7  |

|      | 3.3    | Operating the General Purpose Module (GPM) To Control the Software Defined Radio           |    |

|      |        | (SDR)                                                                                      | 7  |

|      | 3.4    | Examples                                                                                   | 8  |

|      | 3.5    | IPASDataIO Internal to the General Purpose Module (GPM)                                    | 10 |

| 4.0  | Exte   | rnal Interfaces                                                                            | 11 |

|      | 4.1    | Command and Control Graphical User Interface (GUI)                                         | 11 |

|      | 4.2    | IPASDataIO External to the General Purpose Module (GPM)                                    | 17 |

|      | 4.3    | Plotting a Captured Sine Wave                                                              |    |

| 5.0  | Sign   | al Processing Module (SPM)                                                                 | 19 |

|      | 5.1    | Hardware Identification                                                                    | 19 |

|      | 5.2    | Development Tools                                                                          | 19 |

|      | 5.3    | Xilinx <sup>®</sup> ML605 Field-Programmable Gate Array (FPGA) Board Configuration—Jumpers |    |

|      |        | and Dual In-Line Package (DIP) Switch Settings                                             | 19 |

|      | 5.4    | CompactFlash (CF)                                                                          |    |

|      | 5.5    | Joint Test Action Group (JTAG) Programming                                                 |    |

|      | 5.6    | Archiver Compression File (ACE) File                                                       |    |

|      | 5.7    | Field-Programmable Gate Array (FPGA) Mezzanine Card (FMC) Connector Interface to           |    |

|      |        | Radiofrequency (RF) Board                                                                  | 20 |

|      | 5.8    | Power Supply                                                                               | 21 |

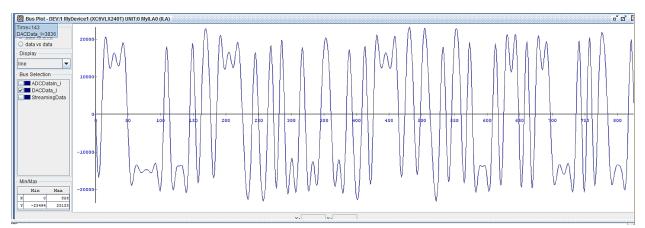

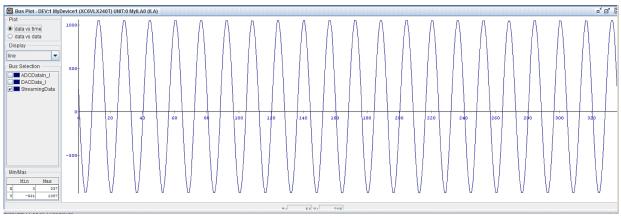

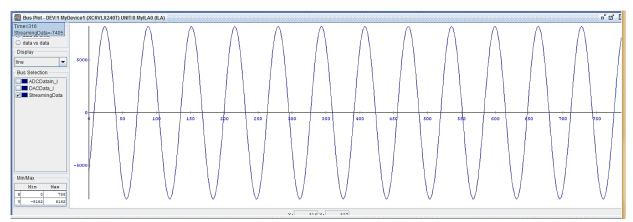

|      | 5.9    | Viewing the Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC)        |    |

|      |        | Signals Using the Xilinx <sup>®</sup> ChipScope <sup>™</sup> Pro Tool                      | 21 |

|      | 5.10   | Non-Return-to-Zero-Mark (NRZ-M) Data Format Option                                         | 24 |

|      | 5.11   | Optional Lower Data Rate Design                                                            | 24 |

| 6.0  |        | ofrequency Module (RFM)                                                                    |    |

|      | 6.1    | Hardware Identification                                                                    | 25 |

|      | 6.2    | Using the Radiofrequency (RF) Board                                                        | 25 |

|      | 6.3    | Interfaces                                                                                 |    |

| 7.0  | Harc   | lware Initialization Procedure                                                             | 26 |

| 8.0  | Con    | clusions                                                                                   | 28 |

| App  | endix  | -Abbreviations and Acronyms                                                                | 29 |

| Refe | erence | 25                                                                                         | 31 |

# Contents

# Integrated Power, Avionics, and Software (iPAS) Space Telecommunications Radio System (STRS) Radio User's Guide—Advanced Exploration Systems (AES)

Rigoberto Roche and Mary Jo Shalkhauser National Aeronautics and Space Administration Glenn Research Center Cleveland, Ohio 44135

#### **Summary**

The Space Telecommunications Radio System (STRS) provides a common, consistent framework for software defined radios (SDRs) to abstract the application software from the radio platform hardware. The STRS standard aims to reduce the cost and risk of using complex, configurable, and reprogrammable radio systems across NASA missions. To promote the use of the STRS architecture for future NASA advanced exploration missions, NASA Glenn Research Center developed an STRS-compliant SDR on a radio platform used by the Advanced Exploration System program at NASA Johnson Space Center in their Integrated Power, Avionics, and Software (iPAS) laboratory. This document provides information to program, operate, and configure the iPAS STRS radio on the Reconfigurable, Intelligently-Adaptive Communication System (RIACS) platform.

## 1.0 Introduction

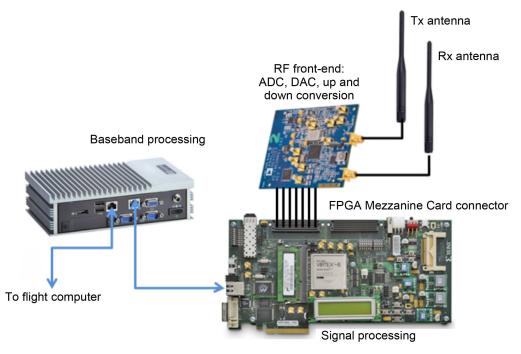

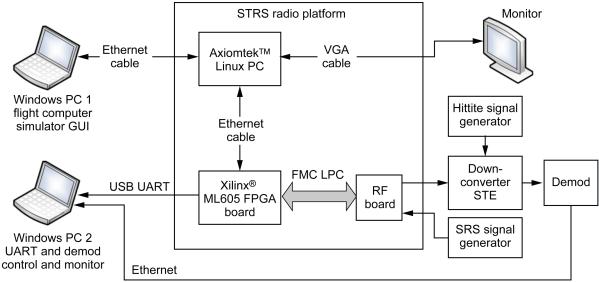

The Integrated Power, Avionics, and Software (iPAS) Space and Telecommunications Radio System (STRS) radio is being implemented on the Reconfigurable, Intelligently-Adaptive Communication System (RIACS) platform, currently being used for radio development at NASA Johnson Space Center. The platform consists of a Xilinx<sup>®</sup> Virtex<sup>®</sup>-6 ML605 Evaluation Kit, an Analog Devices AD–FMCOMMS1–EBZ radiofrequency (RF) front-end board, and an Axiomtek<sup>™</sup> eBOX620–110–FL embedded personal computer (PC) running the Ubuntu<sup>®</sup> 12.04 LTS operating system (OS). Figure 1 shows the RIACS platform hardware.

#### 1.1 System Overview

The goal of this development is to implement the STRS standard for software defined radios (SDRs) on the RIACS platform at Johnson. At the conclusion of the development, the software and hardware description language (HDL) code will be delivered to Johnson for their use in their iPAS testbed and for development of their own STRS waveforms on the RIACS platform.

#### **1.2 Document Overview**

The purpose of this document is to describe how to configure and operate the iPAS STRS radio platform with its delivered test waveform. Throughout this document, commands are always shown in *italics*.

# 2.0 Design Overview

This section presents a design overview of the iPAS STRS radio components.

Figure 1.—Reconfigurable, Intelligently-Adaptive Communication System (RIACS) platform. ADC, analog-to-digital converter; DAC, digital-to-analog converter; FPGA, field-programmable gate array; RF, radiofrequency; Rx, receive; Tx, transmit; UDP, User Datagram Protocol.

#### 2.1 General Purpose Module (GPM)

The GPM is the implementation of the STRS command infrastructure on the iPAS radio. It houses the operating environment (OE) and presents a communication conduit for commands and data to and from the signal processing module (SPM). The GPM is where the general purpose processor (GPP) hardware is contained and accessed by the OS running the STRS project files.

The GPP hardware (eBOX620–110–FL) is used under the STRS architecture. This architecture can perform transmit-side (Tx-side) streaming to the SPM, receive-side (Rx-side) streaming from the SPM, command generation, command transmission to the SPM, and command processing of responses from the SPM, all simultaneously. The GPP also controls the Ethernet communication protocol (configured in Transmission Control Protocol (TCP)/Internet Protocol (IP)v4), scheduler and dynamic memory allocation of the hardware, and systemic pointing for STRS command and control interfaces.

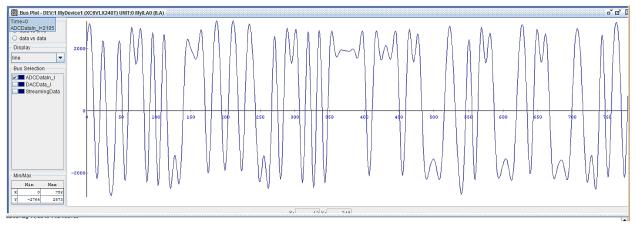

This architecture handles the use of specific waveform characteristics that are commanded in the iPAS test waveform. These parameters include a pseudorandom bit sequence (PRBS) generator in the Tx side for parallel streaming to the SPM, an in-phase (I) and quadrature (Q) channel data source for parallel streaming to the SPM, an Rx-side streaming bit error rate tester (BERT), and a plotting tool for a graphical representation of the incoming data. Additional features include commands to display the bit error rate (BER) from SPM BERT and GPM BERT. Debugging tools included in this software architecture allow the user to query status bits and display any issues indicated by such bits. Additional queries are possible to obtain the status of the first in first out (FIFO) buffer during Tx-side streaming and observation of automatic speed adjustments of Tx-side packet streaming.

### 2.2 Signal Processing Module (SPM)

The purpose of the field-programmable gate array (FPGA) design is the implementation of the SPM functions of the STRS radio architecture in the iPAS RIACS platform. The FPGA design consists of two parts: the FPGA wrapper and the test waveform. The FPGA wrapper implements each platform interface as follows:

- (1) Ethernet communication to the embedded processor for commanding and data streaming

- (2) Digital-to-analog converter (DAC) and analog-to-digital converter (ADC) interface to the RF front-end board (AD–FMCOMMS1–EBZ)

- (3) RF front-end board (AD-FMCOMMS1-EBZ) control and configuration

- (4) FPGA clocking

The test waveform does not fully implement all the signal processing functionality for a radio, but it exercises and demonstrates each interface in the FPGA wrapper. A future user of the platform for an STRS radio would use the FPGA wrapper and replace the test waveform with their own radio signal processing functions.

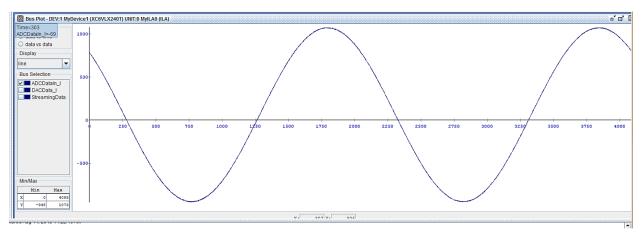

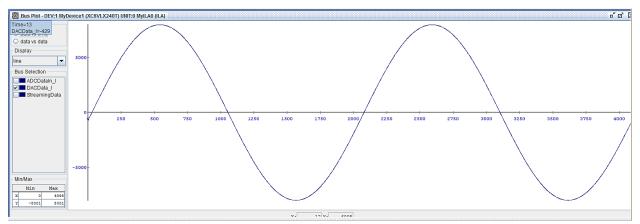

The FPGA design is required to receive and process commands and provide command control and data to the test waveform. It must also receive and transmit streaming data from and to the embedded processor. The test waveform demonstrates each FPGA wrapper interface. To test Tx-side streaming, it can perform BER testing on Tx-side PRBS streaming data. It can also generate PRBS streaming data packets for an Rx-side streaming data source. The test waveform generates sine and cosine waves for the I and Q inputs to the RF transceiver. Captured I and Q outputs of the RF transceiver can be streamed to the embedded processor where it can be plotted to demonstrate proper functionality of the RF board and its interfaces.

#### 2.3 Radiofrequency Module (RFM)

The RF front-end board (AD–FMCOMMS1–EBZ) provides the analog and RF signal processing for the iPAS STRS radio. On the Tx side, the RF front-end board (AD–FMCOMMS1–EBZ) takes complex I and Q inputs (16 bits) into a high-speed DAC to create an analog signal. The DAC output signal is upconverted to the desired RF by a Q modulator. On the Rx side, the received RF signal is demodulated using direct conversion to create I and Q analog signals. The analog signals are converted to digital data using a 14-bit ADC.

#### 2.4 Top-Level Design Description

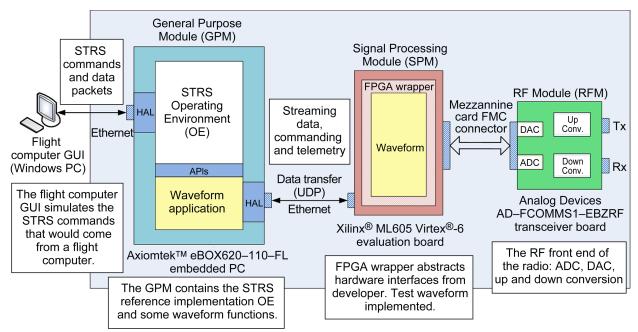

Figure 2 shows how the STRS standard is implemented on the RIACS platform. The SPM encompasses the FPGA design, which consists of the following:

- The FPGA wrapper that implements all the interfaces to the FPGA and abstracts them from the waveform.

- The waveform that is the FPGA implementation of the radio signal processing functions.

#### 2.5 Concept of Operation

The flight computer (FC) graphical user interface (GUI) simulates the STRS commands that would originate from a typical FC. The GPM is implemented on the embedded PC (eBOX620–110–FL) and includes the STRS OE and waveform application software. The STRS OE communicates with the waveform application through standard STRS application programming interfaces (APIs) to control and configure the waveform.

Figure 2.—Space Telecommunications Radio System (STRS) implementation on Reconfigurable, Intelligently-Adaptive Communication System (RIACS) platform. ADC, analog-to-digital converter; APIs, application programming interfaces; DAC, digital-to-analog converter; FPGA, field-programmable gate array; GUI, graphical user interface; HAL, hardware abstraction layer; PC, personal computer; RF, radiofrequency; Rx, receive; Tx, transmit; UDP, User Datagram Protocol.

The SPM is implemented in the Xilinx<sup>®</sup> ML605 FPGA board. The FPGA consists of two parts: an FPGA wrapper and a test waveform. The FPGA wrapper abstracts the hardware interfaces from the waveform developer. The test waveform utilizes each of the hardware interfaces within the wrapper to demonstrate that the wrapper is correctly implemented. The GPM sends commands over an Ethernet port to the FPGA to control and configure the waveform. The GPM also streams packetized data to the FPGA and receives packetized streaming data from the FPGA over the same Ethernet port.

The RF front-end board (AD–FMCOMMS1–EBZ) contains a DAC, up-converter, down-converter, and an ADC. The FPGA configures the RF front-end board (AD–FMCOMMS1–EBZ) using the Xilinx<sup>®</sup> Microblaze<sup>™</sup> 32-bit Reduced Instruction Set Computer soft processor and sends I and Q data to the DAC. The FPGA also receives down-converted and sampled I and Q data from the RF front-end board (AD–FMCOMMS1–EBZ).

The test waveform can demonstrate STRS commands for configuration and control of the test waveform, Tx-side streaming data operation, RF front-end board (AD–FMCOMMS1–EBZ) configuration, Rx-side streaming data, and STRS telemetry querying.

#### **3.0** General Purpose Module (GPM)

This section describes the GPM.

#### 3.1 Software Control Description

The GPM houses the STRS reference implementation. This implementation runs the STRS OE. The STRS OE allows for applications to reference the STRS APIs, which are used to standardize the communication protocols on NASA's space SDRs. The software implementation presented in this design is an adaptation of a test implementation written for VxWorks and ported onto a Linux system.

There are two methods for controlling the iPAS STRS radio. Each method is representative of external control from an FC, where the GPM acts only as a passthrough interface that is standardized by the STRS APIs, sending commands, getting responses, and controlling data transfer between the FC and the SPM.

The first method of control is an external computer connected via Ethernet. This computer runs a flight computer simulator (FCS) that can send commands, receive and interpret command responses, and send and receive data. This method is described in Section 4.0. Additionally, an application for simulating data transfer from an FC called IPASDataIO was written. This application also resides in the external control computer and it is described in Section 4.0. A clone of the IPASDataIO application is also present in the STRS\_Architecture\_RI directory of the GPM.

The second method of control is internal to the GPM, where a separate software process is implemented to send commands to the process running the STRS reference implementation commanded via Ethernet. The TCP/IP configuration allows for a software socket to be created and any other process can communicate to that interface via a static IP address. This can be used to control the radio using both internal processes in the GPM and an external FCS connected via Ethernet. The GPM is running the Ubuntu Linux 12.04 LTS OS. This OS allows for the communication interfaces in the different parts of the radio to use the standard protocols implemented in the UNIX environment out of the box.

Both control methods described in this document implement the STRS commands described in Table I. The anatomy of these commands is described in the STRS iPAS Hardware Interface Description document (Ref. 1). The command header specified in Table I is only relevant to control the sample waveform developed for this implementation, "WFIPAS2."

The commands for this radio implementation have the following structure:

#### Source; Destination; Property; Property Name; Property Value

In this implementation the *Source* = FC (*Flight Computer*) and *Destination* = *WFIPAS2* (*Sample Waveform*). This can be changed when other waveforms are developed to run on the platform. However, WFIPAS2 requires two commands to be sent so that the SDR can be configured and controlled through the STRS. These commands are:

- (1) FC;FC;STRS\_InstantiateApp;%STRS\_BASE%/WFIPAS2/WFIPAS2.cfg

- (2) FC;WFIPAS2;STRS\_Initialize

In order to facilitate the automation of standard control commands for WFIPAS2, several bash script files were created with the ".init" extension. These files will be discussed in more detail in Section 3.4. For now, it is only important to know that these files can be run and modified to automatically configure the SDR for a particular task. This way the user is not required to enter command after command and explicitly write out each of the properties. The user may simply edit one of these ".init" files and either copy and paste commands onto the terminal or run the scripts as a whole to achieve a specific configuration.

Other commands are implemented in WFIPAS2. However, the relevant commands for control and interface testing of the SDR are listed in Table I. These are the only commands necessary to exercise all the interfaces and demonstrate the capabilities of WFIPAS2.

One important aspect to note is that some commands can only be executed while the waveform is not running. The SOURCETX and SOURCERX property values can only be set while the waveform is stopped. All the other commands should be used after the waveform is running (after executing STRS\_Start).

| Command<br>source and<br>destination | Command<br>property     | Property name                           | Property value    | D LIST AND DESCRIPTION Description                                  |

|--------------------------------------|-------------------------|-----------------------------------------|-------------------|---------------------------------------------------------------------|

| FC <sup>a</sup> ; FC;                | STRS_<br>InstantiateApp | %STRS_BASE%<br>/WFIPAS2<br>/WFIPAS2.cfg | NA                | Instantiate base object for waveform configuration                  |

| FC;<br>WFIPAS2 <sup>b</sup> ;        | STRS_Initialize;        | NA                                      | NA                | Initialize environment control interface                            |

| FC;<br>WFIPAS2;                      | STRS_Start;             | NA                                      | NA                | Start waveform                                                      |

| FC;<br>WFIPAS2;                      | STRS_Stop;              | NA                                      | NA                | Stop waveform                                                       |

| FC;<br>WFIPAS2;                      | STRS_Configure;         | SOURCETX                                | STREAMING_PRBS    | Set data source to external PRBS <sup>c</sup> generator             |

|                                      |                         |                                         | STREAMING_SINE    | Set data source to external sine wave generator                     |

|                                      |                         |                                         | PRBS              | Set data source to internal (from SPM <sup>d</sup> ) PRBS generator |

|                                      |                         |                                         | SINEWAVE          | Set data source to internal (from SPM) sine wave generator          |

|                                      |                         | SOURCERX                                | NORMAL            | Set data sink to forward data to RF <sup>e</sup> module             |

|                                      |                         |                                         | LOOPBACK          | Set data sink to return data to SPM bypassing the RFM <sup>f</sup>  |

|                                      |                         | STREAMTX                                | ENABLE            | Enable Tx-side streaming                                            |

|                                      |                         |                                         | DISABLE           | Disable Tx-side streaming                                           |

|                                      |                         | STREAMRX                                | ENABLE            | Enable Rx-side streaming                                            |

|                                      |                         |                                         | DISABLE           | Disable Rx-side streaming                                           |

|                                      |                         | PRBS                                    | ENABLE            | Enable internal (from SPM) PRBS generator                           |

|                                      |                         |                                         | DISABLE           | Disable internal (from SPM) PRBS generator                          |

|                                      |                         | BERT <sup>g</sup>                       | ENABLE            | Enable internal (from SPM) BER <sup>h</sup> tester                  |

|                                      |                         |                                         | DISABLE           | Disable internal (from SPM) BER<br>tester                           |

|                                      |                         | INSERTERROR                             | 1, 2, any integer | Insert errors in internal (from SPM)<br>PRBS generator              |

| FC;<br>WFIPAS2;                      | STRS_Query;             | BERDATA                                 | NA                | Queries internal (from SPM) BER<br>tester                           |

TABLE I.—SPACE TELECOMMUNICATIONS RADIO SYSTEM (STRS) INTEGRATED POWER, AVIONICS, AND SOFTWARE (IPAS) GENERAL PURPOSE MODULE (GPM) COMMAND LIST AND DESCRIPTION

<sup>a</sup>Flight computer. <sup>b</sup>iPAS sample waveform. <sup>c</sup>Psuedorandom bit sequence. <sup>d</sup>Signal processing module. <sup>c</sup>Radiofrequency. <sup>f</sup>Radiofrequency module. <sup>g</sup>Bit error rate tester. <sup>BDit</sup> computer.

<sup>h</sup>Bit error rate.

|       | 1-desktop:~/Desktop\$ ifconfig                               |

|-------|--------------------------------------------------------------|

| eth0  |                                                              |

| c cho | inet addr:192.168.0.1 Bcast:192.168.0.255 Mask:255.255.255.0 |

|       | UP BROADCAST MULTICAST MTU:1500 Metric:1                     |

|       | RX packets:0 errors:0 dropped:0 overruns:0 frame:0           |

|       | TX packets:0 errors:0 dropped:0 overruns:0 carrier:0         |

|       | collisions:0 txqueuelen:1000                                 |

|       | RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)                        |

|       |                                                              |

| eth1  | Link encap:Ethernet HWaddr 00:60:e0:54:16:f0                 |

|       | inet addr:192.168.1.5 Bcast:192.168.1.255 Mask:255.255.255.0 |

|       | UP BROADCAST MULTICAST MTU:1500 Metric:1                     |

|       | RX packets:0 errors:0 dropped:0 overruns:0 frame:0           |

|       | TX packets:0 errors:0 dropped:0 overruns:0 carrier:0         |

|       | collisions:0 txqueuelen:1000                                 |

|       | RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)                        |

|       |                                                              |

| lo    | Link encap:Local Loopback                                    |

|       | inet addr:127.0.0.1 Mask:255.0.0.0                           |

|       | inet6 addr: ::1/128 Scope:Host                               |

|       | UP LOOPBACK RUNNING MTU:65536 Metric:1                       |

|       | RX packets:24 errors:0 dropped:0 overruns:0 frame:0          |

|       | TX packets:24 errors:0 dropped:0 overruns:0 carrier:0        |

|       | collisions:0 txqueuelen:0                                    |

|       | RX bytes:1824 (1.8 KB) TX bytes:1824 (1.8 KB)                |

Figure 3.—Typical output from *iconfig* in the general purpose module (GPM).

## **3.2** Verifying Correct Interface Configuration

The GPM's Ethernet interfaces should automatically configure at login. However, it is good practice to make sure the interfaces are configured correctly before starting operations. To verify the configuration, perform the following actions:

- (1) Log in to the jsc1 user.

- (2) Open a terminal window.

- (3) Type the command *ifconfig*.

- (4) If the output from *ifconfig* is not the same as illustrated in Figure 3, restart the GPM.

# **3.3** Operating the General Purpose Module (GPM) To Control the Software Defined Radio (SDR)

The STRS reference implementation source code is housed in the GPM in the directory path: /home/jsc1/code/strs/STRS\_Architecture\_RI. In this directory, an executable shell script has been created to run the Ethernet control protocol for the STRS OE to run WFIPAS2. This shell script is called runGUI.sh.

The following procedure describes how to initialize the control interface in the GPM.

- Connect the power converter to the embedded PC (eBOX620-110-FL) and to the Xilinx<sup>®</sup> ML605 FPGA board, respectively. Make sure that the power supplies are not live (not connected to the grid socket).

- (2) Connect the included Ethernet cable from the slot on the embedded PC (eBOX620–110–FL), labeled "FPGA," to the Ethernet connector on the Xilinx<sup>®</sup> ML605 FPGA board.

- (3) Connect a Universal Serial Bus (USB) mouse (not included) and USB keyboard (not included) to the embedded PC (eBOX620–110–FL).

- (4) Connect a Video Graphics Array (VGA) input display (not included) to the embedded PC (eBOX620–110–FL).

- (5) If using an external control computer, connect an Ethernet cable (not included) from the remaining open slot of the embedded PC (eBOX620–110–FL) to the Ethernet connector in the control computer.

- (6) Connect the power converters to the grid socket.

- (7) Turn on the Xilinx<sup>®</sup> ML605 FPGA board by operating power On/Off slide switch 2 (SW2) to the On position. The DS25 light-emitting diode (LED) will illuminate green to indicate that the board is powered on.

- (8) Turn on the embedded PC (eBOX620–110–FL) by depressing the power switch in the back and releasing it after 3 s.

- (9) Once steps (1) to (8) are complete, log in to Linux. The password to log in to the Linux desktop is "strs" (without quotes).

- (10) Open a terminal window after login.

- (11) Type the following commands into the terminal:  $\int dt = \int dt dt = \int dt$

cd /home/jsc1/code/strs/STRS\_Architecture\_RI ./runGUI.sh

Once the control script executes, the GPM is ready to receive commands.

In order to send commands internally, use the *nc* command. The *nc* (or netcat) utility is used for controlling actions involving TCP or User Datagram Protocol (UDP). It can open TCP connections, send UDP packets, listen on arbitrary TCP and UDP ports, perform port scanning, and process both IPv4 and IPv6. In the case of the STRS iPAS Radio, the IPv4 standard is used.

With the runGUI.sh script running, static IP address 192.168.1.5 is open with a socket created in the GPM. This socket communicates through port 1120 and listens for inputs from external, connected devices (via Ethernet) or any other process that communicates to that static IP/port combination. For internal control, use the *echo* command and pipe /, the output of *echo* to *nc*. Using Table I, a command that has the following structure can be constructed to be executed under runGUI.sh:

echo "FC;WFIPAS2;STRS\_Start" | nc 192.168.1.5 1120

To send internal commands, follow these steps:

- (1) Open a second terminal window (different from the one running runGUI.sh).

- (2) Type a command in the way specified above and press Enter.

- (3) Look at the runGUI.sh terminal window for output related to the command.

#### 3.4 Examples

Several examples were written to facilitate the use of internal control in the GPM. These examples are files with the extension ".init" and they are located in the following directory path:

/home/jsc1/code/strs/STRS\_Architecture\_RI/WFIPAS2

This section focuses on understanding what is happening in each of the lines of one of the examples provided so that the user can have a clear picture of the command structures and procedures used to control the SDR. The example files located in the previously mentioned path are

- WFIPAS.init-normal.sh

- WFIPAS.init-tx.sh

- WFIPAS.init.txt

- WFIPAS.init+loopback.sh

- WFIPAS.init+rxprbs.sh

- WFIPAS.init+test.sh

- WFIPAS.init+txprbs.sh

- WFIPAS.stop.sh

This section explores WFIPAS.init+loopback.sh. The contents of this file are shown below:

```

0 #!/bin/bash

1

2 NC="nc 192.168.1.5 1120"

3 set -x

4

5 echo "FC;FC;STRS_InstantiateApp;%STRS_BASE%/WFIPAS2/WFIPAS2.cfg" | $NC

6 sleep 1

7 echo "FC;WFIPAS2;STRS_Initialize" | $NC

8 sleep 1

9 echo "FC;WFIPAS2;STRS_Configure;SOURCETX;STREAMING_PRBS;SOURCERX;LOOPBACK" | $NC

10 sleep 1

11 echo "FC;WFIPAS2;STRS_Start" | $NC

12 sleep 1

13 echo "FC;WFIPAS2;STRS_Configure;STREAMTX;ENABLE;STREAMRX;ENABLE" | $NC

```

This file configures the SDR to receive PRBS23 data from an external source, pipe the data through the GPM, send the data over to the SPM, and then loopback the data in the SPM back to the GPM, bypassing the RFM. Then the GPM is configured to forward that same data out to an external sink. The external source/sink being used is IPASDataIO (see Sec. 3.1).

Line 0 is a convention, so the \*nix shell knows what type of interpreter is necessary in order to run this script. This is not relevant to SDR control; it is simply a convention. Line 2 sets up a variable with the static IP address and port to communicate with the process initiated by runGUI.sh. Line 3 handles environment variable setting in the instance of the shell script. This is not relevant to SDR control; it is only needed for the script to work well if run simultaneously. Line 5 and Line 7 are the initial commands needed to instantiate the base object representative of the waveform and then to initialize the control environment.

The SDR configuration commends are in Lines 9, 11, and 13. Line 9 is a combination of two commands: *FC;WFIPAS2;STRS\_Configure;SOURCETX; STREAMING\_PRBS* and *FC;WFIPAS2;STRS\_Configure;SOURCERX;LOOPBACK*. Since properties with different names and value pairs are being configured under the same parameter control (STRS\_Configure), the command can be combined into one STRS\_Configure parameter control with the two name and value pairs and it will function the same as sending two independent commands.

The waveform is started using the STRS\_Start command. Now, bidirectional streaming can be enabled. Similar to the commands in line 9, the commands in line 13 are combined into one parameter control with two sets of name and value pairs.

The user is encouraged to look through these example files to gain a thorough understanding of the internal operation of the SDR and how these files can be used to configure and command the platform with ease.

#### **3.5** IPASDataIO Internal to the General Purpose Module (GPM)

To exercise the external data path to the STRS iPAS Radio, an application called IPASDataIO was written. This is a very simple application. Its main function is to read two files, one PRBS24.bin file, containing a PRBS of 10<sup>23</sup>–1 unique bits repeated eight times, and a cos.bin file containing a sampled sine wave.

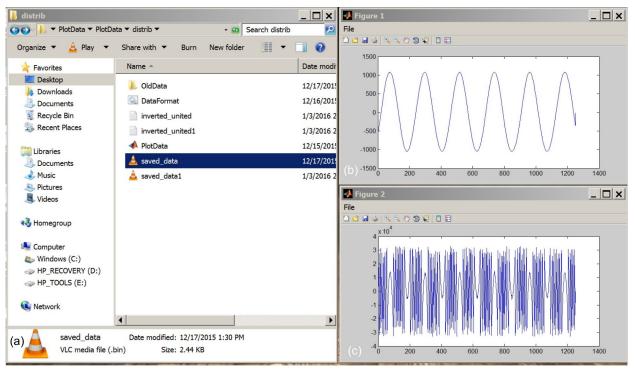

This application takes two inputs: input one is the file to be read and input two is the mode of operation. As previously stated, the files to be read are either PRBS23.bin or cos.bin and the modes of operation are tx (transmit only), rx (receive only), and txrx (transmit and receive). Additionally, this application provides a BERT when receiving PRBS23 data and there are three user commands available while the application is running. These commands are *e* to enter an error into the PRBS23 sequence, *z* to clear the status display of the BERT, and *s* to save a file of sample data containing 2 MB of the Rx stream.

In order to run IPASDataIO follow these steps:

- (1) Once logged in to the GPM and running runGUI.sh, configure the SDR to use external data sources using the example files in Section 3.4.

- (2) Open a second terminal window (other than the one running runGUI.sh) and navigate to the IPASDataIO directory:

cd /home/jsc1/code/strs/STRS\_Architecture\_RI/IPASDataIO

- (3) Now the IPASDataIO application can be run in any of these modes:

- (a) Command: /x86\_64-pc-linux-gnu/IPASDataIO.out ./cos.bin tx is used to send sine wave data to the GPM, but also to receive sine wave data. An example of executing this command is shown in Figure 4.

- (b) Command: ./x86\_64-pc-linux-gnu/IPASDataIO.out ./PRBS23.bin rx is used to receive PRBS23 data to the GPM and pass it through a BERT.

- (c) Command: ./x86\_64-pc-linux-gnu/IPASDataIO.out ./PRBS23.bin tx is used to send PRBS23 data to the GPM.

- (d) Command: /x86\_64-pc-linux-gnu/IPASDataIO.out ./PRBS23.bin txrx is used to send PRBS23 data to the GPM, receive PRBS23 data from the GPM, and pass that data through a BERT.

Note: The IPASDataIO is an independent process to the SDR control interface. It sends data to a specific IP address and port combination; whether that results in sending data to another process running in the same OS or to a process running on a different machine has no effect on the actions of IPASDataIO.

#### GRNLW2292692+STRS\_LAB@grn1w2292692 ~/code/strs/STRS\_Architecture\_RI/IPASdataIO \$ ./x86\_64-pc-1inux-gnu/IPASdataIO.out ./cos.bin tx|

Figure 4.—Command execution.

- (4) Now that IPASDataIO is running, the terminal window where it is running should be populated with the statistics of the transmitting and receiving of bits, packets, and errors. The user can now enter one of three key strokes to initiate the following actions:

- (a) Press *e* and then Enter to insert an error in the PRBS23 sequence being transmitted.

- (b) Press *z* and then Enter to reset the counters for the statistics being displayed periodically by IPASDataIO.

- (c) Press *s* and then Enter to save a 2 MB sample for the incoming data form an external source to IPASDataIO. The file will be saved under the IPASDataIO directory and it will be called saved\_data.bin.

Note: When IPASDataIO is used in txrx mode there are some initial errors displayed in the BERT statistics, this is due to the asynchronous nature of the external connection to the GPM. Perform step (4)(b) (above) to clear these errors. There should not be any other errors after this initial burst (usually less than 100 errors).

(5) To terminate the application, press the "Ctrl + C" key combination.

# 4.0 External Interfaces

This section describes the system's external interfaces.

## 4.1 Command and Control Graphical User Interface (GUI)

A command and control GUI can be used as an FCS to send commands to the SDR and receive command responses from the SDR via 1 Gbps Ethernet. The purpose of this interface is to demonstrate the capability for an external physical device (another computer, an FC, or another SDR) to control the STRS iPAS SDR.

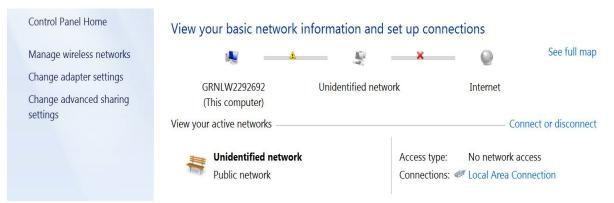

This GUI operates on a Windows 7 64-bit OS PC. The user may choose to install the interface in a similar configuration. However, make sure to follow these steps to configure static IP communication via IPv4 on the OS.

- (1) To configure this interface, navigate to Control Panel $\rightarrow$ Network Settings.

- (2) If the Ethernet cable is not connected from the control PC to the GPM, connect it now. Once this is done, a screen similar to Figure 5 will appear.

Figure 5.—Ethernet configuration for the flight computer simulator (FCS) for the Integrated Power, Avionics, and Software (iPAS) radio on the Windows 7 personal computer (PC).

| eneral                          | Networking Sharing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | General                                                                                                             |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Connection                      | Connect using:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | You can get IP settings assigned automatically if your network                                                      |

| IPv4 Connectivity: No network a | ccess Intel(R) Ethernet Connection I217-LM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | supports this capability. Otherwise, you need to ask your network<br>administrator for the appropriate IP settings. |

| IPv6 Connectivity: No network a | Configure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

|                                 | abled This connection uses the following items:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Obtain an IP address automatically                                                                                  |

| Duration: 00                    | 08:29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Use the following IP address                                                                                        |

| Speed: 1.0                      | Gbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IP address: 192 . 168 . 1 . 2                                                                                       |

| Details                         | 🛛 📕 QoS Packet Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

| Details                         | E File and Printer Sharing for Microsoft Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Subnet mask: 255 . 255 . 255 . 0                                                                                    |

|                                 | Internet Protocol Version 6 (TCP/IPv6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Default gateway: 192 . 168 . 1 . 1                                                                                  |

|                                 | Internet Protocol Version 4 (TCP/IPv4)     Link-Layer Topology Discovery Mapper I/O Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

| Activity                        | Since a property of the second se | Obtain DNS server address automatically                                                                             |

| Sent — 🛄 — Rec                  | eived                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Use the following DNS server addresses                                                                              |

| alter a                         | Install Uninstall Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Preferred DNS server:                                                                                               |

| Packets: 253                    | 0 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

|                                 | Transmission Control Protocol/Internet Protocol. The default<br>wide area network protocol that provides communication acros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Alternate DNS server:                                                                                               |