## SEU Analysis of Complex Circuits Implemented in Actel RTAX-S FPGA Devices

M. Friendlich, C. Perez, H. Kim, C. Seidlick, T. Irwin: MEI Technologies/NASA GSFC K. LaBel: NASA GSFC

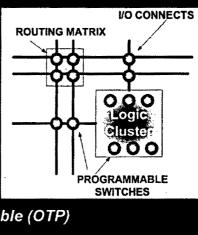

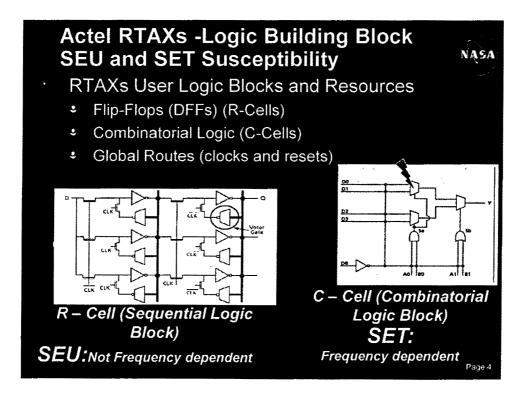

Configuration Defines: Functionality (logic cluster) Connectivity (routes) Placement

and on http://radhome.gsfc.nasa.gov and http://nepp.nasa.gov/.

Page

NASA

Page 2

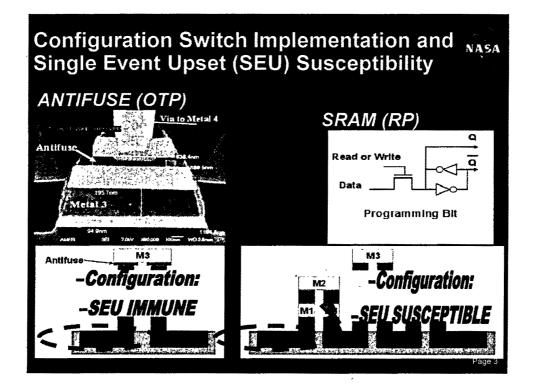

Configuration Switch Types: Antifuse: One time Programmable (OTP) SRAM: Reprogrammable (RP) Flash: Reprogrammable (RP)

To be presented by Melanie Berg at the 11th European Conference on Radiation and its effects on components and systems (RADECS) conference 9/20 to 9/24/2010, Langenfeld, Austria,

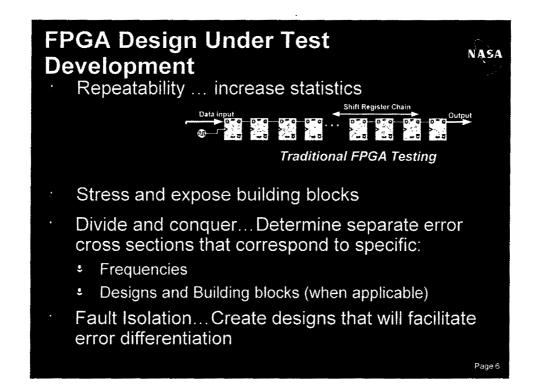

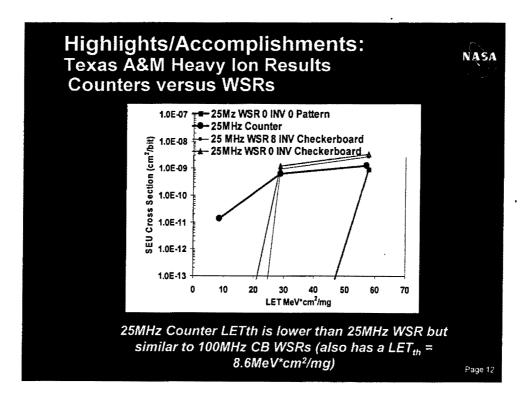

## Highlights/Accomplishments: REAG WSR SEE Results

NASA

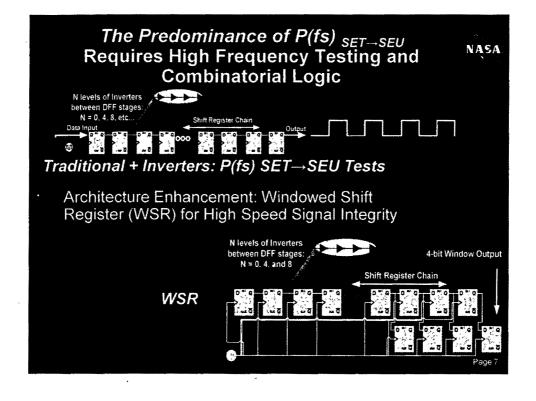

- Error rates are significantly dependent on Threshold LET(LET<sub>th</sub>)

- Choice of design impacted LET<sub>th</sub> ... number of C-Cells between DFFs

- Choice of data pattern and frequency of operation impacted LET<sub>th</sub> (>2 orders of magnitude)

|                                           | Low Frequency                              | Increased Frequency                                               |

|-------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|

| LET <sub>th</sub> MeV*cm <sup>2</sup> /mg | LET <sub>th</sub> >37                      | 8< LET <sub>th</sub> <30                                          |

| Bit Error Rate (errors/bit-day)           | dE <sub>bit</sub> /dt ≈1x10 <sup>-10</sup> | 1x10 <sup>-10&lt;</sup> dE <sub>bit</sub> /dt <5x10 <sup>-8</sup> |

|                                           |                                            |                                                                   |

If Frequency or data pattern were not varied during testing, then an incorrect LET<sub>th</sub> and dE<sub>hit</sub>/dt would had been calculated

6

## Summary

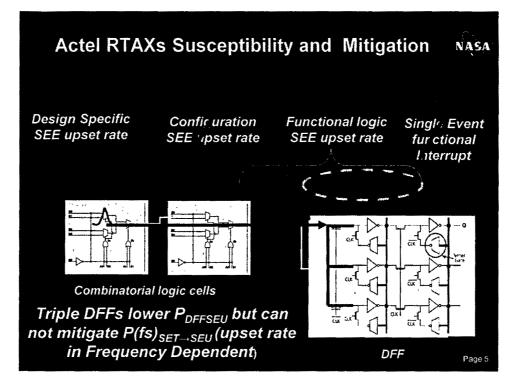

- Because configuration, global routes, and configuration is hardened in the RTAXs device, P<sub>SET→SEU</sub> becomes the most significant source of upsets in radiation environments

- The ratio of combinatorial logic delay to clock frequency within a data path will drive P<sub>SET-SEU</sub>

- Hence, Choice of Architecture and frequency can significantly affect SEE cross section and bit error rate RTAXs characterization

- Counter Arrays were driven near their top speed while containing several combinatorial logic levels. Subsequently they produced the lowest LETth→Highest bit error rate versus the shift register designs

Page 13

NASA