## Acronym List

| AMBA   | ARM Advanced Microcontroller Bus Architecture | DRAM   | Dynamic Random Access memory                              | GPU   | Graphics Processing Unit                     |

|--------|-----------------------------------------------|--------|-----------------------------------------------------------|-------|----------------------------------------------|

| ASIC   | Application Specific Integrated Circuit       | DTRA   | Defense Threat Reduction<br>Agency                        | GSFC  | Goddard Space Flight<br>Center               |

| BSP    | Board Support Package                         | ECC    | Error Correction Coding                                   | HEOMD | Human Exploration and Operations Directorate |

| BW     | Bandwidth                                     | EEPROM | Electrically Erasable<br>Programmable Read-Only<br>Memory | HPPS  | High Performance<br>Procerssing Subsystem    |

| CCN    | Cache Coherent Network                        | FCR    | Fault Containment Region                                  | HPSC  | High Performance<br>Spaceflight Computing    |

| CFS    | Core Flight Software                          | FPGA   | Field Programmable Gate<br>Array                          | I2C   | Inter-Integrated Circuit                     |

| СРИ    | Central Processing Unit                       | FPU    | Floating Point Unit                                       | IDE   | Integrated Development<br>Environment        |

| C&DH   | Command and Data Handling                     | FSW    | Flight Software                                           | ISA   | Instruction Set Architecture                 |

| CDR    | Critical Design Review                        | Gbd    | Gigabaud                                                  | ISI   | Information Sciences<br>Institute            |

| DARPA  | Defense Advanced Research Projects Agency     | Gb/s   | Gigabits Per Second                                       | JPL   | Jet Propulsion Laboratory                    |

| DDR    | Double Data Rate                              | GB/s   | Gigabytes Per Second                                      | JTAG  | Joint Test Action Group                      |

| DECTED | Double Error Correct Triple Error<br>Detect   | GHz    | Gigahertz                                                 | KHz   | Kilohertz                                    |

| DMEA   | Defense Microelectronics<br>Activity          | GNC    | Guidance Navigation and<br>Control                        | Kpps  | Kilo Packets Per Second                      |

| DMIPS  | Dhrystone Million Instructions per Second     | GOPS   | Giga Operations Per Second                                | LET   | Linear Energy Transfer                       |

To be presented at Radiation Hardened Electronics Technology (RHET) Conference, Phoenix, AZ, November 5-8, 2018.

## Acronym List

| Mbps  | Megabits Per Second                              | PERFECT | Power Efficiency Revolution For<br>Embedded Computing<br>Technologies | SpW   | SpaceWire                                      |

|-------|--------------------------------------------------|---------|-----------------------------------------------------------------------|-------|------------------------------------------------|

| МСМ   | Multi Chip Module                                | QoS     | Quality of Service                                                    | SRAM  | Static Random Access<br>memory                 |

| MeV   | Million Electron Volt                            | RHBD    | Radiation Hardened By Design                                          | SRIO  | Serial RapidIO                                 |

| MHz   | Megahertz                                        | RTOS    | Real Time Operating System                                            | SSED  | Solid-State Electronics Development            |

| MRAM  | Magnetoresistive Random Access Memory            | RTPS    | Real Time Processing Subsystem                                        | SSR   | Solid State Recorder                           |

| MT/s  | Million Transfers per Second                     | S/C     | Spacecraft                                                            | STMD  | Space Technology Mission<br>Directorate        |

| mW    | Milli Watt                                       | SCP     | Self Checking Pair                                                    | TID   | Total Ionizing Dose                            |

| NASA  | National Aeronautics and<br>Space Administration | SCS     | Secure Computing Solutions                                            | TTE   | Time Triggered Ethernet                        |

| NGSP  | Next Generation Space<br>Processor               | SEE     | Single Event Effects                                                  | TTGbE | Time Triggered Gigabit<br>Ethernet             |

| nm    | Nanometer                                        | SerDes  | Serializer Deserializer                                               | TMR   | Triple Modular Redundancy                      |

| NVRAM | Nonvolatile Random Access memory                 | SIMD    | Serial Instruction Multiple Data                                      | TRCH  | Timing Reset Configuration and Health          |

| РСВ   | Printed Circuit Board                            | SMD     | Science Mission Directorate                                           | XAUI  | 10 Gigabit Media<br>Independent Interface)     |

| PCle  | Peripheral Component<br>Interconnect Express     | SOI     | Silicon On Insulator                                                  | UART  | Universal Asynchronous<br>Receiver/Transmitter |

| PDR   | Preliminary Design Review                        | SPI     | Serial Peripheral Interface                                           | VMC   | Vehicle Management<br>Computer                 |

### **Outline**

- HPSC Overview

- HPSC Contract

- Key Requirements

- Chiplet Architecture

- HPSC System Software and Middleware

- NASA HPSC Use Cases

- HPSC Ecosystem

# High Performance Spaceflight Computing (HPSC) Overview

- The goal of the HPSC program is to dramatically advance the state of the art for spaceflight computing

- HPSC will provide a nearly two orders-of-magnitude improvement above the current state of the art for spaceflight processors, while also providing an unprecedented flexibility to tailor performance, power consumption, and fault tolerance to meet widely varying mission needs

- These advancements will provide game changing improvements in computing performance, power efficiency, and flexibility, which will significantly improve the onboard processing capabilities of future NASA and Air Force space missions

- HPSC is funded by NASA's Space Technology Mission Directorate (STMD), Science Mission Directorate (SMD), and the United States Air Force

- The HPSC project is managed by Jet Propulsion Laboratory, and the HPSC contract is managed by NASA Goddard Space Flight Center (GSFC)

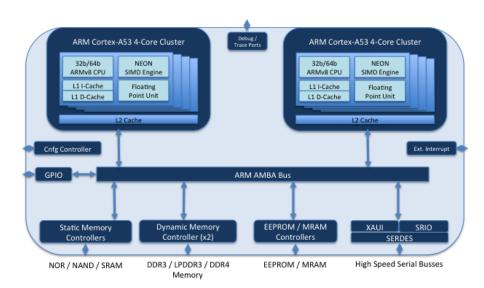

### **HPSC** Reference Architecture

- Initially provided in the Request for Proposal, a reference design features power-efficient ARM 64-bit processor cores (8) and on-chip interconnects scalable and extensible in MCM (Multi-Chip Module) or on PCB (Printed Circuit Board) via XAUI and SRIO (Serial RapidIO) 3.1 high-speed links

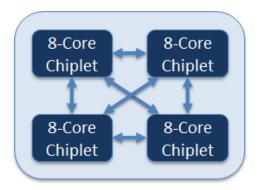

- Multi-Chiplet configurations (tiled or cascaded) provide increased processing throughput and/or increased fault tolerance (e.g. each Chiplet as separate fault containment regions, NMR)

- Chiplets may be connected to other XAUI/SRIO devices

- > e.g. FPGAs, GPUs, or ASIC co-processors

- Supports multiple hardware-based and software-based fault tolerance techniques

**Multi-Chiplet Configuration**

**HPSC "Chiplet" Reference Design**

### **HPSC Contract**

- Following a competitive procurement, the HPSC cost-plus fixed-fee contract was awarded to Boeing

- Under the base contract, Boeing will provide:

- Prototype radiation hardened multi-core computing processors (Chiplets), both as bare die and as packaged parts

- Prototype system software which will operate on the Chiplets

- Evaluation boards to allow Chiplet test and characterization

- Chiplet emulators to enable early software development

- Five contract options have been executed to enhance the capability of the Chiplet

- On-chip Level 3 cache memory

- Dual real-time processors

- Dual Time Triggered Ethernet (TTE) interfaces

- Dual SpaceWire interfaces

- Package amenable to spaceflight qualification

- Contract deliverables are due April 2021

### **Chiplet Architecture**

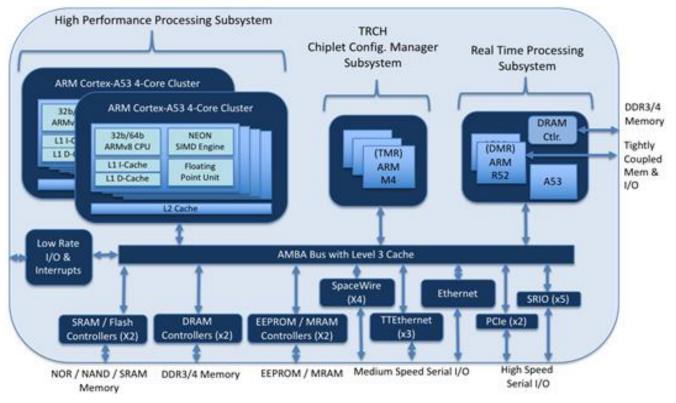

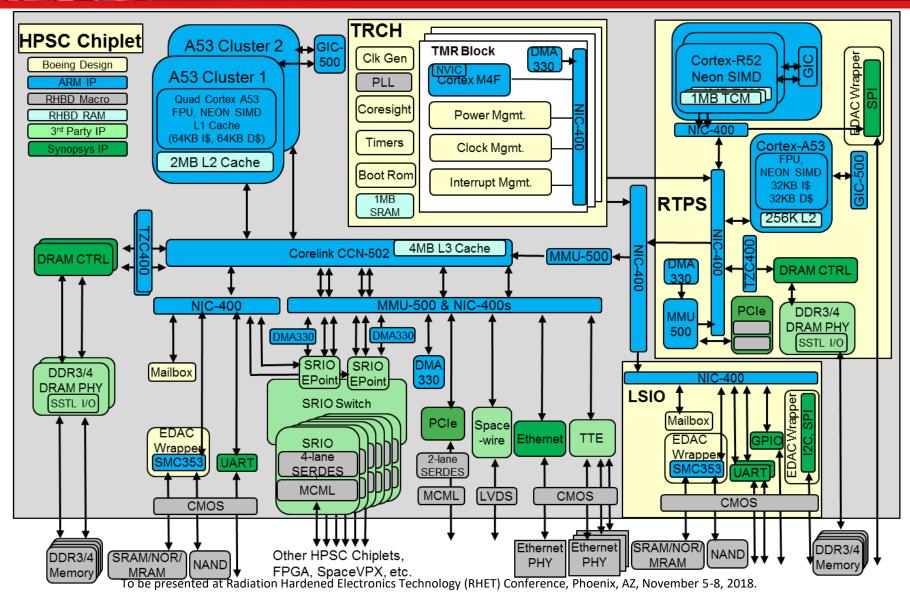

With the contract options awarded and the preliminary design completed, the Chiplet architecture has evolved from the original reference architecture

**HPSC Chiplet Architecture**

# HPSC Chiplet Program Overview Program Structure & Schedule

### Tasks (WBS Level 1)

**1.0** Management **4.0** System Software Development

**2.0** System Engineering **5.0** Evaluation Board Development

**3.0** Chiplet Development **6.0** Test and Characterization

#### Phases

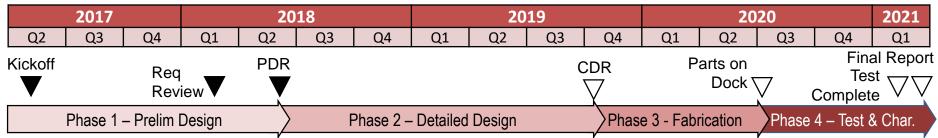

| Phase                      | Duration  | Period of Performance           |

|----------------------------|-----------|---------------------------------|

| 1. Preliminary Design      | 14 months | March 2017 through May 2018     |

| 2. Detailed Design         | 17 months | June 2018 through October 2019  |

| 3. Fabrication             | 9 months  | November 2019 through July 2020 |

| 4. Test & Characterization | 9 months  | August 2020 through April 2021  |

#### Schedule

## **Key Requirements Summary**

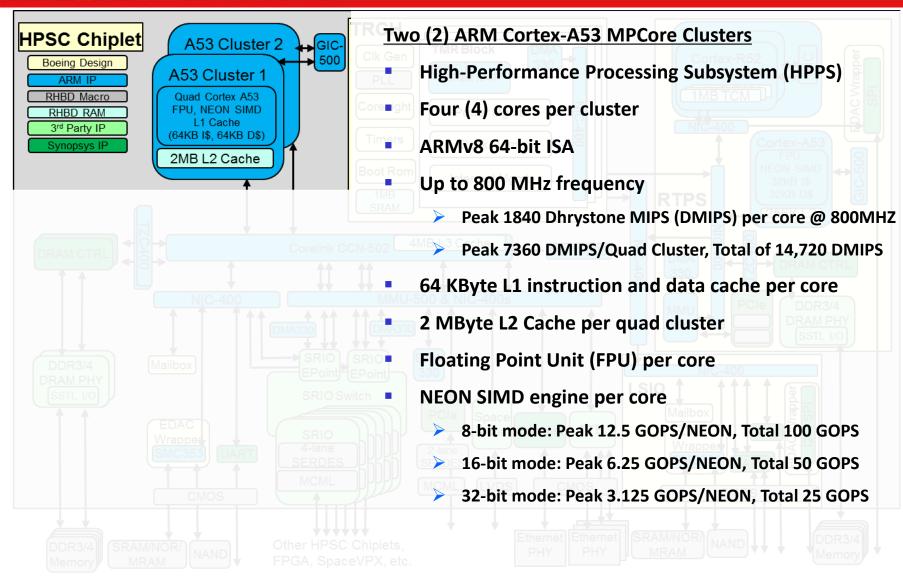

| Processor Cores           | <ul> <li>High Performance Processing Subsystem (HPPS): 8 ARM Cortex-A53 cores with floating point &amp; Single Instruction Multiple Data (SIMD) engine. Performance &amp; power on next slide</li> <li>Real Time Processing Subsystem (RTPS) with single A53 and dual Cortex-R52 cores</li> </ul> |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

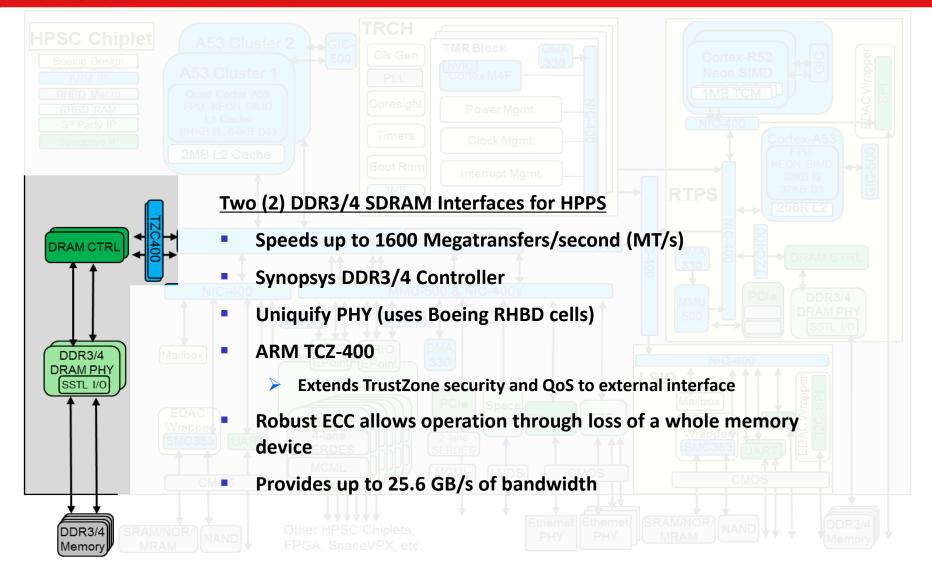

| Memory Interfaces         | <ul> <li>3 DDR3/4: 2 for A53 clusters, 1 for RTPS</li> <li>4 SRAM/NVRAM</li> <li>Enhanced error correction (ECC) to operate through bit upsets and whole memory device failures</li> </ul>                                                                                                        |  |  |

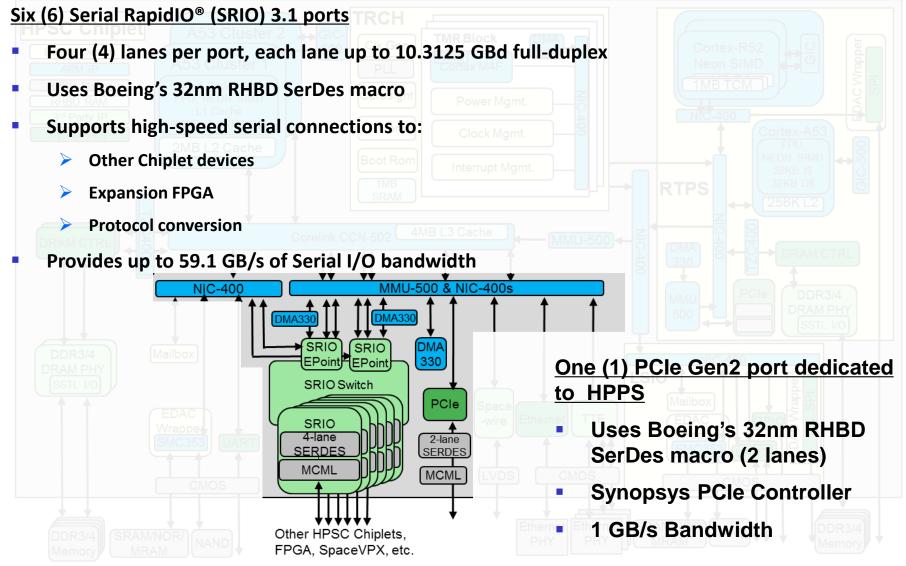

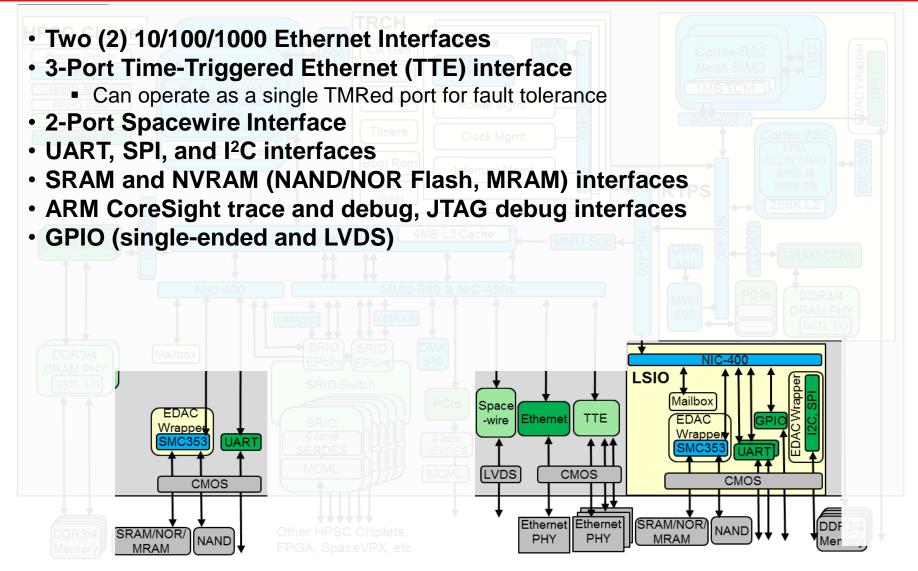

| IO Interfaces             | <ul> <li>6 SRIO 3.1, 2 PCle Gen2 serial IO</li> <li>Ethernet, SpaceWire, Time Triggered Ethernet (TTE), SPI, UART, I<sup>2</sup>C, GPIO</li> </ul>                                                                                                                                                |  |  |

| Power scaling             | Able to dynamically power down/up cores, subsystems, & interfaces via software control                                                                                                                                                                                                            |  |  |

| Fault tolerance           | Able to autonomously detect errors & log errors, prevent propagation past established boundaries, and notify software                                                                                                                                                                             |  |  |

| Trust & Assured Integrity | <ul> <li>DMEA-accredited Trusted supply chain</li> <li>Free of malicious insertions / alterations</li> </ul>                                                                                                                                                                                      |  |  |

| Temperature               | -55C to 125C                                                                                                                                                                                                                                                                                      |  |  |

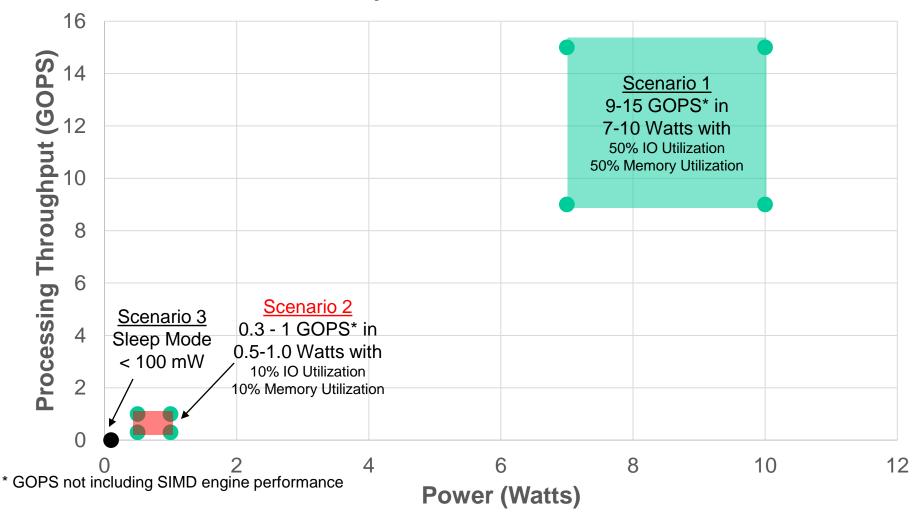

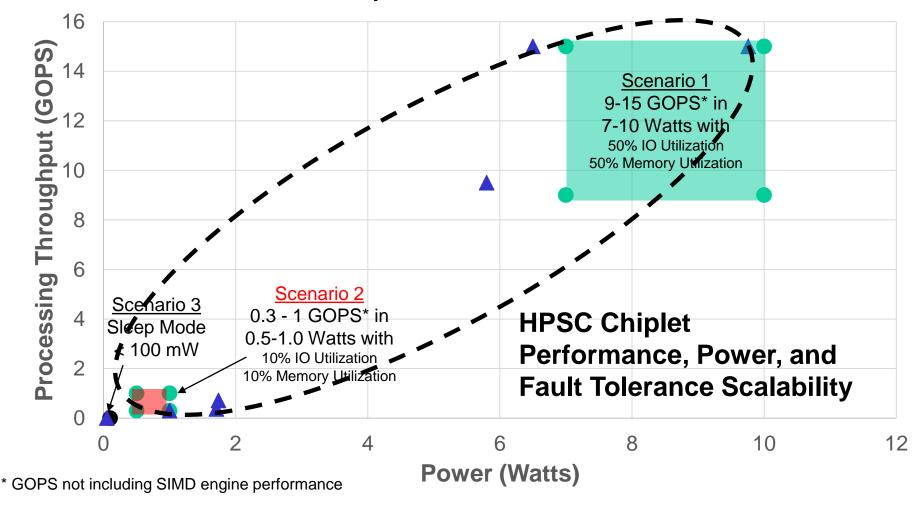

## Performance @ Power Requirements

### **HPSC Chiplet Performance at Power**

## Key Requirements Summary

| Total Ionizing Dose (TID)                      | Strategic radiation                                                                                                                                                                                                  |                                                                                                              |  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Prompt Dose Immunity                           | hardness for Air                                                                                                                                                                                                     |                                                                                                              |  |

| Dose Rate Survivability                        | Force applications                                                                                                                                                                                                   |                                                                                                              |  |

| Latchup Immunity                               | LET ≥ 90 MeV-cm <sup>2</sup> /mg                                                                                                                                                                                     |                                                                                                              |  |

| Single-Event Upset (SEU)<br>(Adams 90% WC GEO) | <ul><li>HPPS (A53 Array):</li><li>RTPS:</li><li>TRCH:</li></ul>                                                                                                                                                      | <ul><li>≤ 1E-3 errors/device-day</li><li>≤ 1E-4 errors/device-day</li><li>≤ 1E-5 errors/device-day</li></ul> |  |

| Single-Event Upset (SEU)<br>(WC Solar Flare)   | <ul><li>HPPS (A53 Array):</li><li>RTPS:</li><li>TRCH:</li></ul>                                                                                                                                                      | ≤ 1E-1 errors/device-min<br>≤ 1E-2 errors/device-min<br>≤ 1E-3 errors/device-min                             |  |

| Reliability                                    | ≥ 100,000 power-on hours                                                                                                                                                                                             |                                                                                                              |  |

| Software                                       | <ul> <li>Multicore operating systems (Linux &amp; RTOS)</li> <li>Development tools (compilers, debuggers, etc)</li> <li>Board Support Packages (BSPs)</li> <li>APIs for fault tolerance, power management</li> </ul> |                                                                                                              |  |

| Emulators Take presented at Rediction Header   | Software-based quick emulator     FPGA-based cycle-accurate emulator  ed Electronics Technology (RHET) Conference, Phoenix, AZ, November 5-8, 2018.                                                                  |                                                                                                              |  |

To be presented at Radiation Hardened Electronics Technology (RHET) Conference, Phoenix, AZ, November 5-8, 2018.

# HPSC Chiplet Program Overview Approach

- Develop Chiplet using Boeing's RHBD 32nm SOI design & fabrication flow, which provides:

- High-performance library and mixed-signal macros

- Strategic radiation hardness

- Single-Event-Effects (SEE) mitigations optimized for power efficiency

- Assured integrity

- Employ core competencies of team comprised:

- Boeing Solid-State Electronics Development (SSED)

- Boeing Secure Computing Solutions (SCS)

- Boeing Space & Launch

- USC Information Sciences Institute (ISI)

- University of Michigan ARM Research Center

- Utilize silicon-proven IP:

- ARM, Globalfoundries, Synopsys, Praesum, and Uniquify

- Leverage tens of millions of dollars of Government and Boeing investments in related technology areas:

- DTRA RHBD3, AFRL/NASA Next NGSP, MAESTRO, DARPA PERFECT, etc.

## **HPSC Chiplet Architecture**

# Chiplet Architecture: High-performance Cores

## Chiplet Architecture: Interconnect

4MB L3 Cache

Advanced Power Management Features

Corelink CCN-502

- 60 GB/s internal interconnect bandwidth @ 1GHz

- Supports ECC, Quality of Service (QoS), QoS Virtual Networks, and ARM TrustZone security

# Chiplet Architecture: DRAM Interfaces

# Chiplet Architecture: Serial I/O Interfaces

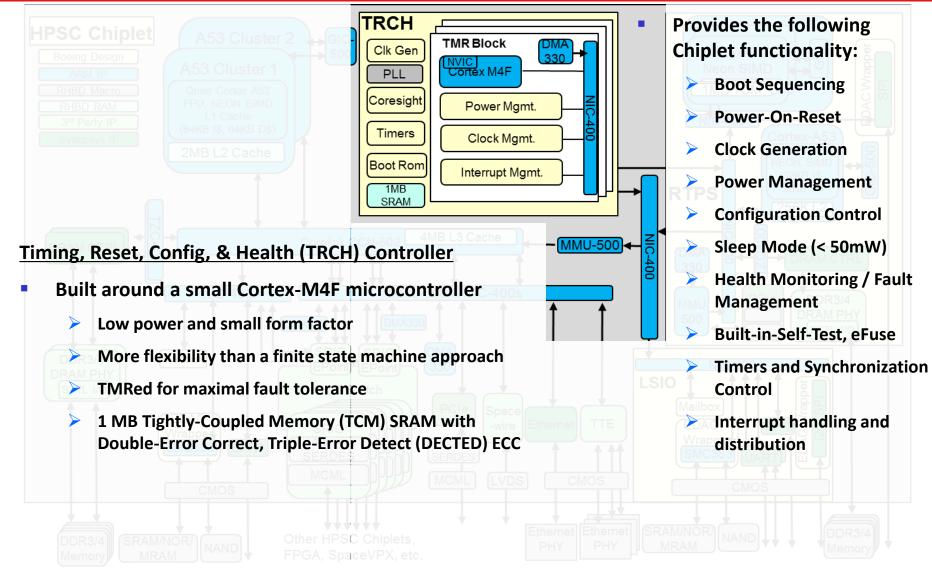

# Chiplet Architecture: TRCH Controller

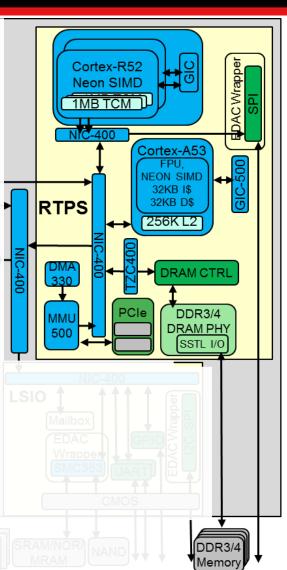

# Chiplet Architecture: Realtime Processing Subsystem

#### **Realtime Processing Subsystem (RTPS)**

- Single Cortex-A53 core managing two (2) Cortex-R52 Realtime cores (ARM v8 64b)

- Supports virtualization and time & space partitioning / ARINC 653, as well as realtime performance needs

- RTPS Dedicated Memory & IO interfaces:

- One (1) DDR3/4 interface

- One (1) PCIe Gen2 interface

- One (1) SPI interface

- R52 cores provide:

- ARM's highest level of safety features, including Dual-Core Lock Step (DCLS) operation

- Up to 600 MHz frequency

- Peak 1296 Dhrystone MIPS (DMIPS) per core @ 600MHZ

- Floating Point Unit (FPU), NEON SIMD engine, and 1 MB Tightly Coupled Memory per core

- A53 core provides:

- Peak 1380 Dhrystone MIPS (DMIPS) @ 800MHZ

- 32 KB L1, 256 KB L2 Caches

# Chiplet Architecture: Other IO Interfaces

### Performance @ Power Predictions

### **HPSC Chiplet Performance at Power**

### **HPSC System Software**

- The HPSC Chiplet inherits a large complement of existing open source software including:

- Libraries, operating systems, compilers, and debuggers.

- We're able to leverage much of this software unmodified.

- The HPSC System Software effort largely encompasses 4 thrusts:

- Board support packages for Linux and RTOS;

- Development tools (e.g., compilers, debuggers, IDEs);

- Software-based fault tolerance; and

- 4. Chiplet emulators.

- Our goal is to build a sustainable software ecosystem to enable full lifecycle software development.

### **HPSC** Middleware

- AFRL is funding JPL and NASA GSFC to develop HPSC Middleware

- Middleware will provide a software layer that provides services to the higher-level application software to achieve:

- Configuration management

- Resource allocation

- Power/performance management

- Fault tolerance capabilities of the HPSC chiplet

- Serving as a bridge between the upper application layer and lower operating system or hypervisor, the middleware will significantly reduce the complexity of developing applications for the HPSC chiplet

#### INTEGRATED STACK CONCEPT

Mission Applications

FSW Product Lines – Core S/C Bus

Functions

GSFC and JPL Core Flight Software (CFS)

HPSC Middleware – Resource Management

Mission-Friendly Interface for

Managing/Allocating Cores for

Performance vs. Power vs. Fault Tolerance

Traditional System Software – RTOS or Hypervisor, FSW Development Environment

Hardware – Multi-core Processor Chips, Evaluation Boards

# HPSC Use Cases – Rovers and Landers

#### Rover

#### **Compute Needs**

- Vision Processing

- Motion/Motor Control

- GNC/C&DH

- Planning

- Science Instruments

- Communication

- Power Management

- Thermal Management

- Fault detection/recovery

- System Metrics

- 2-4 GOPs for mobility(10x RAD750)

- >1Gb/s science instruments

- 5-10GOPs science data processing

- >10KHz control loops

- 5-10GOPS, 1GB/s memory BW for model based reasoning for planning

### Lander

#### **Compute Needs**

- Hard Real time compute

- High rate sensors w/zero data loss

- High level of fault protection/ fail over

#### **System Metrics**

- >10 GOPs compute

- 10Gb/s+ sensor rates

- Microsecond I/O latency

- Control packet rates >1Kpps

- Time tagging to microsecond accuracy

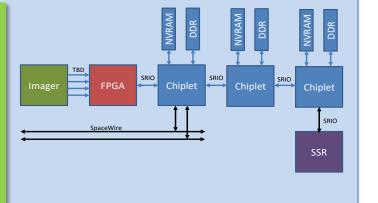

# HPSC Use Cases - High Bandwidth Instruments and SmallSats/Constellations

### **High Bandwidth Instrument**

#### **Compute Needs**

- Soft real time

- Non-mission critical

- High rate sensors

- Large calibration sets in NV memory

- System Metrics

- 10-20 GOPs compute

- >10GB/s memory bandwidth

- >20Gbps sensor IO data rates

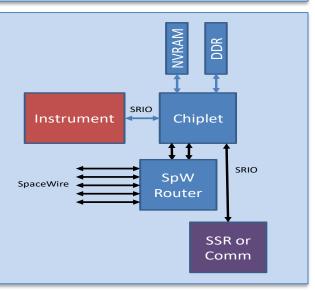

### Smallsat

#### **Compute Needs**

- Hard and Soft real time

- GNC/C&DH

- Autonomy and constellation(cross link comm)

- Sensor data processing

- Autonomous science

- System Metrics

- 2-5Gbps sensor IO

- 1-10GOPs

- 1GB/s memory bandwidth

- 250Mbps cross link bandwidth

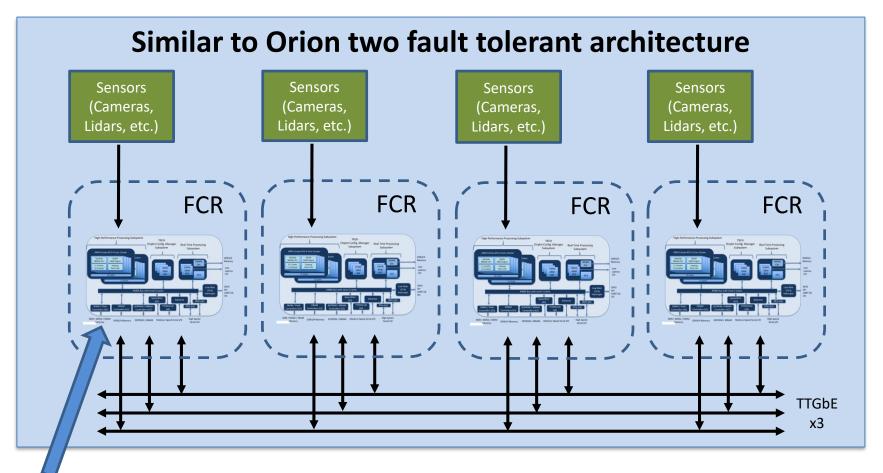

# HPSC Use Cases – HEO Habitat/Gateway

Existing Orion

Vehicle

Management

Computer (VMC)

- A single HPSC exceeds the performance metrics of a Orion Vehicle Management Computer (VMC)

- A VMC contains three Self-Checking Pairs (SCP)

### Broader HPSC Ecosystem

- Beyond the HPSC Chiplet, System Software, and Middleware developments, further investments can implement a robust HPSC avionics ecosystem

- Advanced Spaceflight Memory

- Increased RTOS Support

- Multi-Output Point-Of-Load Converters

- Coprocessors (GPU, Neuromorphic, etc.)

- Special Purpose Chiplets (Security Chiplet, etc.)

- Advanced Packaging (Multiple Chiplets in a Package)

- Single Board Computers

### Conclusion

- As illustrated by the NASA use cases, our future missions demand the capabilities of HPSC

- Improved spaceflight computing means enhanced computational performance, energy efficiency, and fault tolerance

- With the ongoing HPSC development, we are well underway to meeting future spaceflight computing needs

- The NASA-developed Middleware will allow the efficient infusion of the HPSC chiplet into those missions

- Further investments can implement a full HPSC avionics ecosystem

Acknowledgements: Rich Doyle (JPL), Rafi Some (JPL), Jim Butler (JPL), Irene Bibyk (GSFC), Jonathan Wilmot (GSFC), and Jon Ballast (Boeing) for diagrams and use case definitions