# Yearlong 500 °C Operational Demonstration of Up-scaled 4H-SiC JFET Integrated Circuits

Philip G. Neudeck<sup>1</sup>, David J.Spry<sup>1</sup>, Michael J. Krasowski<sup>1</sup>, Norman F. Prokop<sup>1</sup>, Glenn M. Beheim<sup>1</sup>, Liang-Yu Chen<sup>2</sup>, and Carl W. Chang<sup>3</sup>

<sup>1</sup>NASA Glenn Research Center <sup>2</sup>Ohio Aerospace Institute <sup>3</sup>Vantage Partners LLC Cleveland, Ohio, USA

2018 IMAPs International Conference on High Temperature Electronics (HiTEC 2018)

9 May 2018

Albuquerque, New Mexico USA

www.nasa.gov

#### **Acknowledgements**

This work was conducted by The NASA John H. Glenn Research Center in Cleveland, OH USA under joint funding from NASA Science Mission Directorate (High Operating Temperature Technology, Planetary Instrument Concepts for the Advancement of Solar System Observations, and Long-Lived In-Situ Solar System Explorer projects) and NASA Aeronautics Directorate (Transformative Tools and Technologies project).

HX5 Sierra (NASA Glenn)

Kelley Moses

Jose Gonzalez

Michelle Mrdenovich

Arianna Miller

Vantage Partners, LLC (NASA Glenn)

**Dorothy Lukco**

Carl Chang

NASA Glenn Research Center

Gary Hunter

Robert Buttler

George Ponchak

Max Scardelletti

Robert Okojie

Lawrence Green

Félix Miranda

**Lawrence Matus**

## SiC Electronics Benefits to NASA Missions

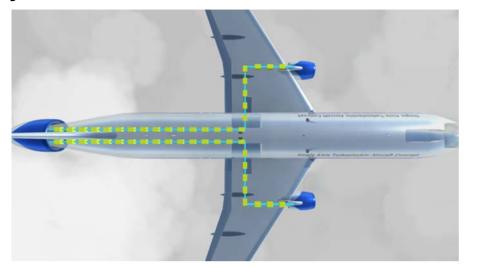

#### **Intelligent Propulsion Systems**

**Hybrid Electric & Turbo Electric Aircraft**

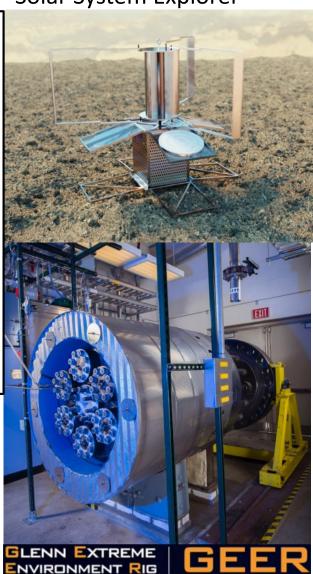

#### **Venus Exploration**

LLISSE = Long-Life In-Situ Solar System Explorer<sup>1</sup>

9.4 Mpa = 92.7 X Earth pressure +  $460 \,^{\circ} \text{C} +$  chemical composition found at the surface of  $\text{Venus} (\text{CO}_2, \text{N}_2, \text{SO}_2, \text{H}_2\text{O}, \text{CO}, \text{OCS}, \text{HCI}, \text{HF, and H}_2\text{S})}$

NASA GRC's internal research effort has been to focused on durable/stable integrated circuit operation at  $500^{\circ}$  C for > 1000 hrs.

<sup>1</sup>T. Kremic, et al., 48<sup>th</sup> Lunar and Planetary Science, 2017, 2986.

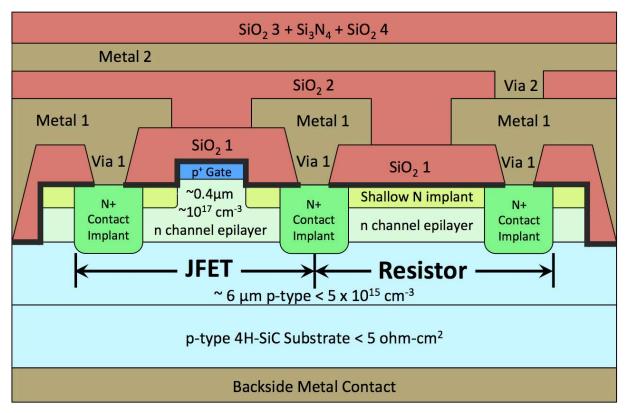

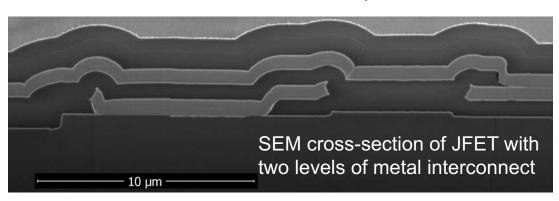

## N-channel JFET design<sup>1,2</sup> "Version 10.1"

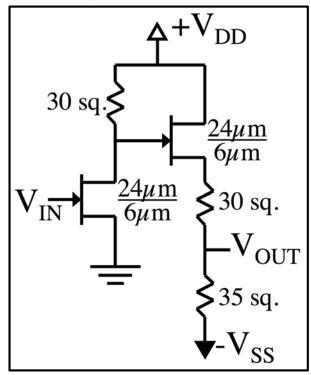

**NOT Logic Gate Schematic**

- Normally-on 4H-SiC JFET (fabricated at NASA Glenn)

- Resistors made with same epi as channel → matched T dependence

- Negative threshold voltage  $V_T \rightarrow$  negative signal voltages (0 to -10V)

- 0 V = Binary 1 (high) -10 V = Binary 0 (low)

- <sup>1</sup>M. J. Krasowski, US Patent 7,688,117 (2010).

- <sup>2</sup>P. G. Neudeck, D. J. Spry, and L. Chen, Proc. IMAPS High Temperature Electronics Conf., 2016, pp. 263-271.

#### **SiC JFET IC Results from HiTEC 2016**

("IC Wafer/Version 9.2")

Normalized Frequency

Primary design goal is extreme environment circuit durability.

# Recent Advances (Since HiTEC 2016)

- Neudeck, et al., AIP Advances 6 (2016) 125119.

- Neudeck, et al., IEEE Electron Device Lett. 38 (2016) 1082-1085.

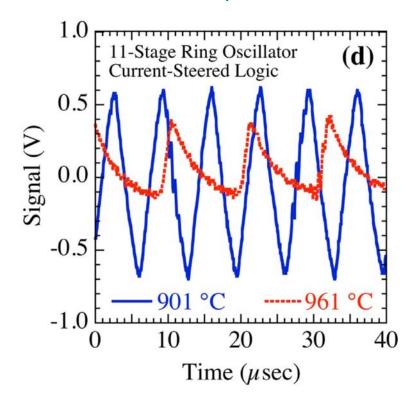

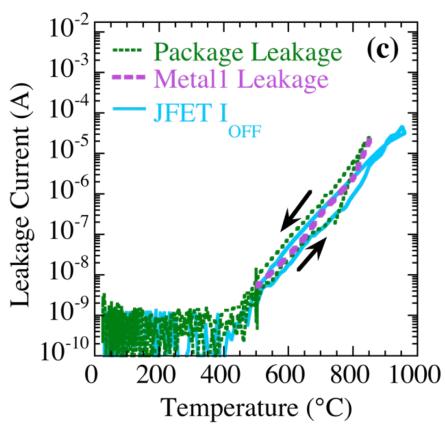

#### NASA SiC JFET IC operation at T > 900 °C

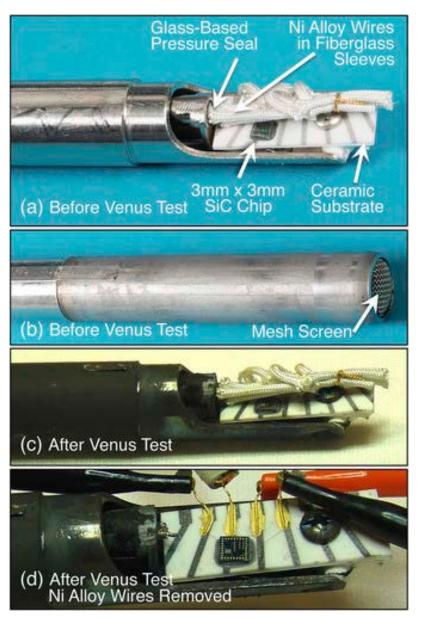

NASA SiC JFET IC operated <u>immersed</u> in Venus surface conditions (460 °C, 9.4 MPa) for 3 weeks, did not fail.

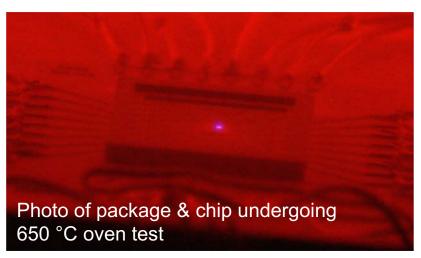

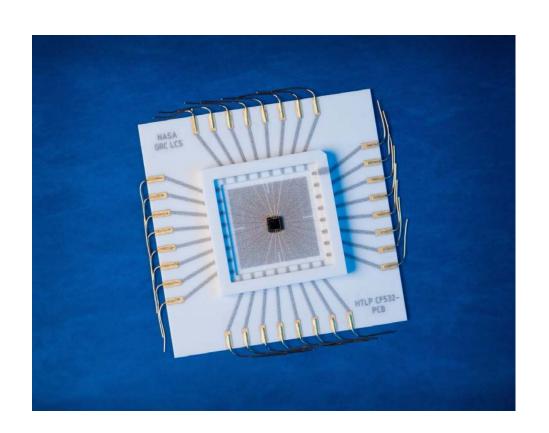

## High-T packaging<sup>1,2</sup> (32 pins, HiTEC 2016)

Package durability and leakage characterized.

<sup>1</sup>L. Chen, et al., Proc. IMAPS High Temperature Electronics Conference, 2016, pp. 66-72. <sup>2</sup>P. G. Neudeck, et al., IEEE Electron Device Lett. 38 (2016) 1082-1085.

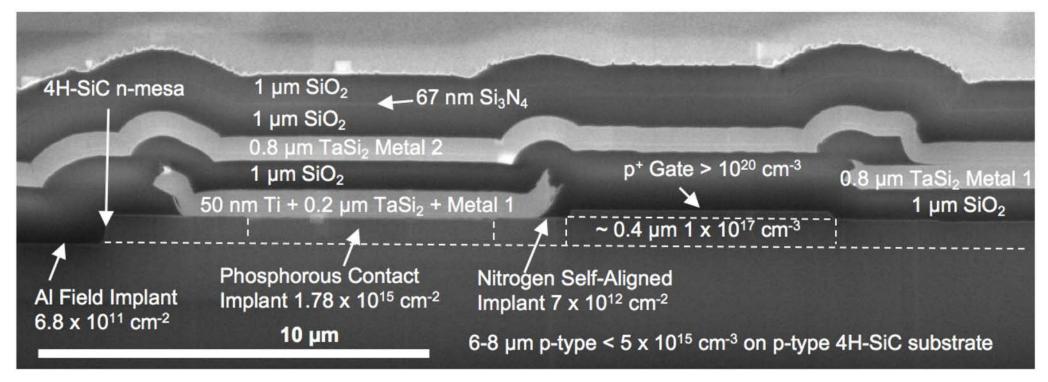

# JFET IC Wafer 10.1 vs past work<sup>1-2</sup>

- Aluminum Field Stop Implant to impede parasitic field MOSFETs.

- Heavily-implanted SiC contact regions were formed using phosphorus implant profile with slightly lower energy & dose.

- Contact was made using 50 nm sputtered titanium layer.

#### Primary design goal is extreme environment durability.

<sup>1</sup>D. J. Spry, et al., Mat. Sci. Forum 828 (2016) 908-912: "IC Wafer/Version 8.1"

<sup>2</sup>D. J. Spry, et al., IEEE Electron Device Lett. 37 (2016) 625-628: "IC Wafer/Version 9.2"

## Wafer 10.1 IC Functional Yield at 25 °C<sup>1</sup>

| Demonstration | IC JFET | # Good/# Tested       | % Yield               |

|---------------|---------|-----------------------|-----------------------|

| IC            | Count   | $r \le 25 \text{ mm}$ | $r \le 25 \text{ mm}$ |

| 16-bit RAM    | 195     | 19/27                 | 70%                   |

| ÷ 2/÷4 Clock  | 175     | 19/26                 | 73%                   |

- JFET threshold voltage V<sub>T</sub> on depends on distance from the center of the wafer r, due to as-purchased wafer epilayer variation (see Ref. 2).

- Table I is for r < 25mm (on 38 mm radius wafer), the wafer region where  $V_T$  falls within circuit design specifications of  $|V_T| < 10 \text{ V}$ .

Despite > 7-fold increase in IC complexity from previous run (Wafer 9.2), functional probe yields in excess of 70% were obtained for Wafer 10.1.

<sup>&</sup>lt;sup>1</sup>D. J. Spry, et al., presented at ICSCRM 2017, to appear in Materials Science Forum, Vol. 924 (2018).

<sup>&</sup>lt;sup>2</sup>P. G. Neudeck, D. J. Spry, and L. Chen, Proc. IMAPS High Temperature Electronics Conf., 2016, pp. 263-271.

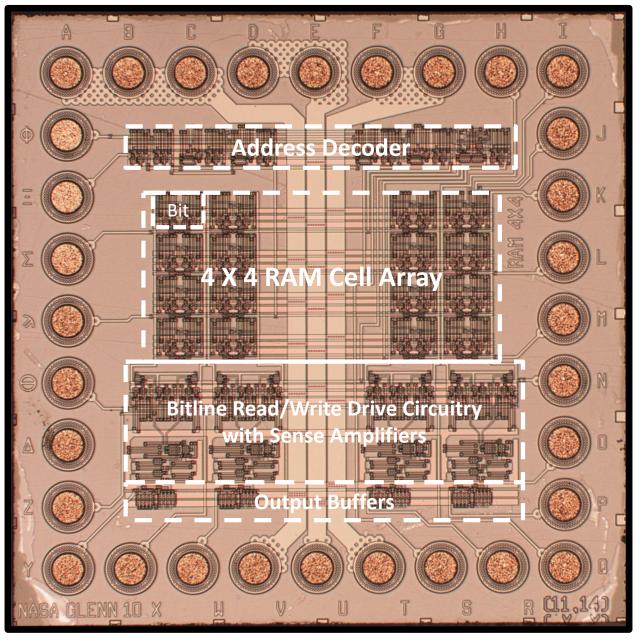

### 4X4 Random Access Memory (RAM) Demonstration Chip<sup>1</sup>

- 3mm x 3mm 4H-SiC

JFET chip shown

prior to packaging.

- 195 JFETs.

- 6-Transistor static RAM cell approach.

- Includes address decoders, read/ write bitline drive with sense amplifiers, output buffers.

<sup>1</sup>D. Spry et al., ICSCRM 2017

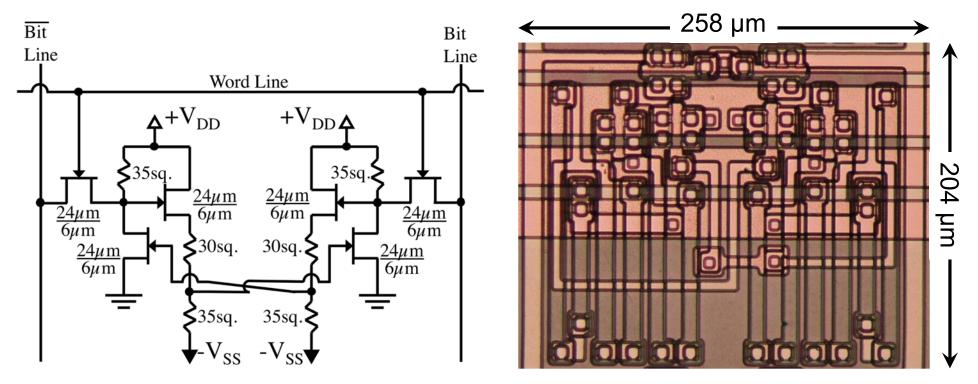

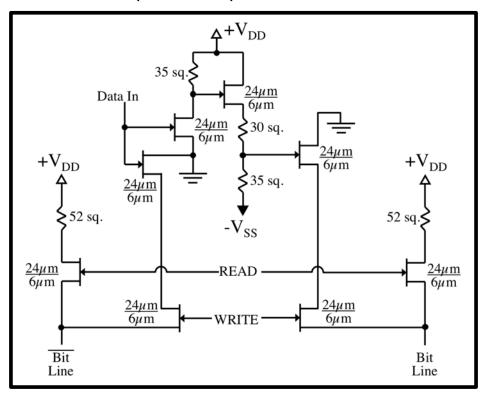

### SiC JFET RAM Chip Circuit Design RAM Cell

6-JFET cell mimics traditional "Static" RAM approach.

- Cross-coupled NOT gate latch connected to bit line pair by access FETs.

To enable "normally on" access JFETs function in "normally off" manner, latch is accessed at inverting amplifier stage and bit lines are internally driven/sensed using positive voltages.

## SiC JFET RAM Chip Circuit Design

RAM Array Support Circuitry

Bit line (Column) Driver Schematic

Internal chip word line (rows) and bit line (column) signals\* at 500 °C

\*Waveforms measured via diagnostic bond pads and oven wiring to 10 M $\Omega$  oscilloscope probes.

- Address decoder and word lines function at negative voltages of logic family.

- Bit lines and sense amplifiers function at positive voltages (per preceding slide).

- Design is "proof of feasibility" for 500 °C operation, not considered "optimized".

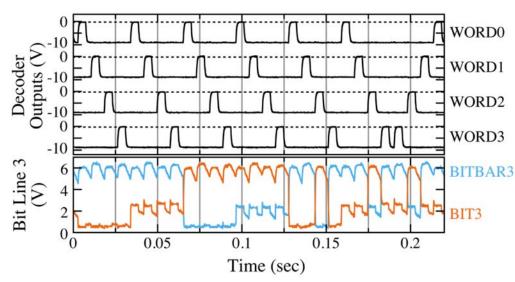

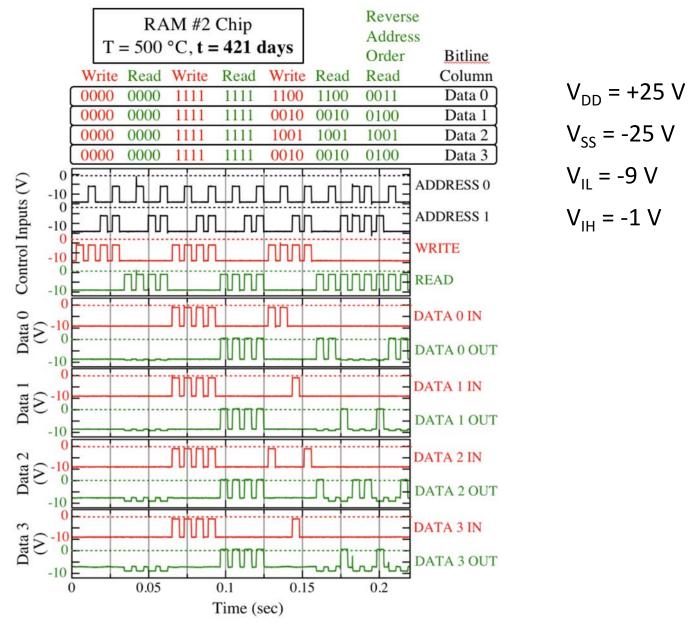

### **RAM #2**

Measured 16-bit RAM waveforms showing read and write functionality of all bits at **421 days** (10,100 hours) of a 500 °C oven test.

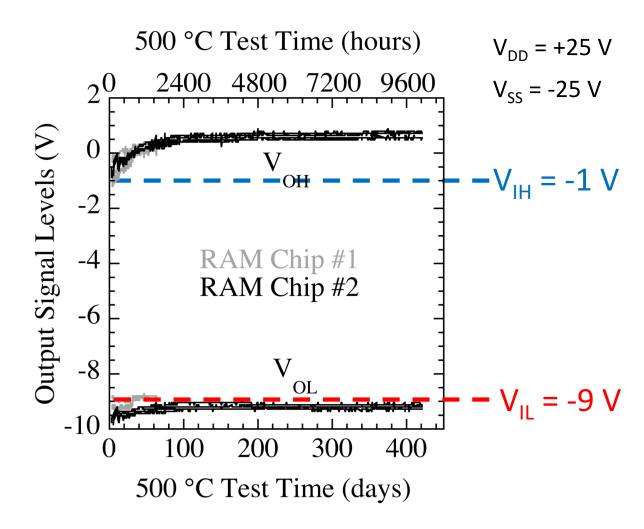

## RAM Chip Output Levels vs 500 °C Test Time

Following modest changes during early burn-in period, output high  $(V_{OH})$  and output low  $(V_{OH})$  voltage levels exhibit negligible change

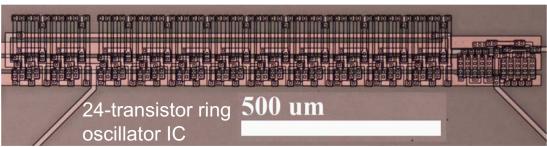

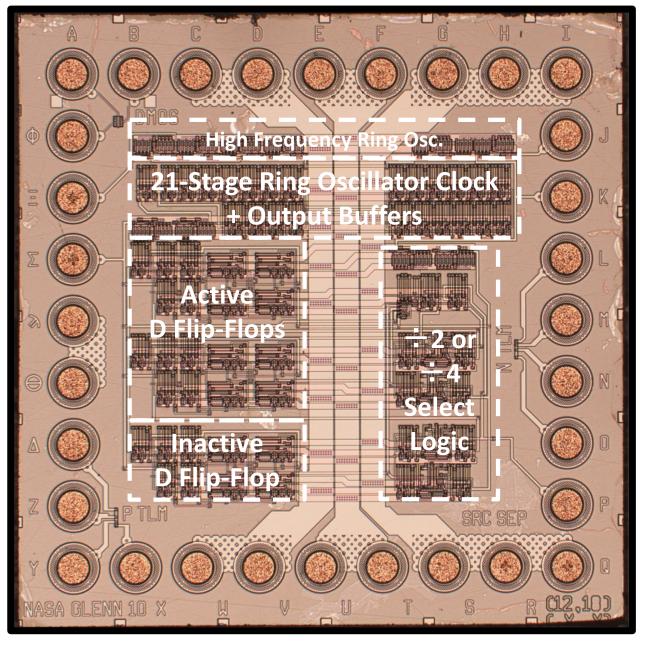

# ÷2/÷4 Clock Demonstration Chip¹

- 3mm x 3mm 4H-SiC JFET chip prior to packaging.

- 175 JFETs

- 21-Stage ring oscillator provides base frequency clock signal

- SELECT data line:

- High  $(0 V) \rightarrow \div 4$  output

- Low (-10 V)  $\rightarrow$  ÷2 output

- Includes two D-type flip flops governed by select logic

- 3rd flip flop is inactive due to layout error.

- Optional modulation of high-f ring oscillator signal

<sup>1</sup>D. Spry et al., ICSCRM 2017

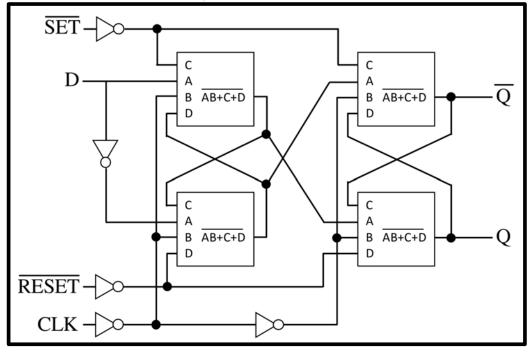

## SiC JFET Flip Flop Circuit Design

**Combination Logic Gate**

A  $+V_{DD}$  35 sq.  $24\mu \text{m}$   $6\mu \text{m}$  30 sq.  $-\overline{AB + C + D}$  35 sq.  $-V_{SS}$

D-Type Flip Flop

- Ring oscillator base clock is frequency divided using Dtype flip-flops.

- Additional logic gates control signal propagation to realize

÷2 vs ÷4 base clock frequency based on SELECT input.

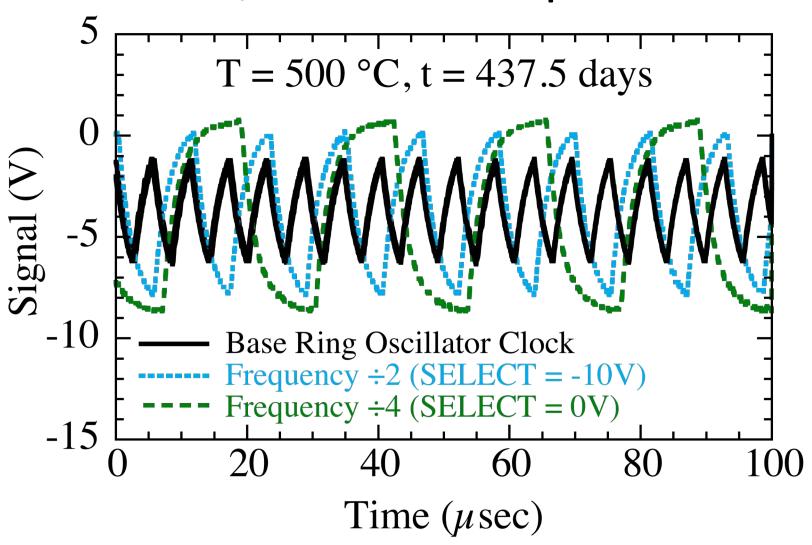

# ÷2/÷4 Clock Chip #2

Measured waveforms showing operation of  $\div 2/\div 4$  clock IC at 437.5 days (10,500 hours) of 500 °C oven testing.

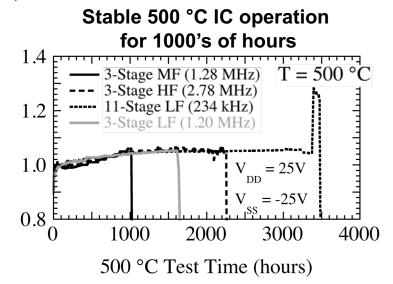

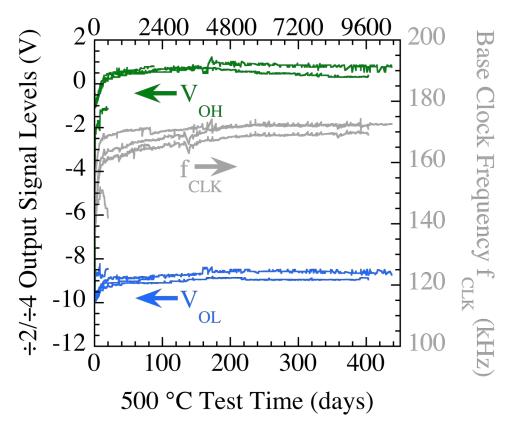

## ÷2/÷4 Clock Signals vs Time at 500 ° C

$$V_{DD} = +25 \text{ V}$$

$$V_{SS} = -25 \text{ V}$$

$$V_{IL} = -10 \text{ V}$$

$$V_{IH} = -0 \text{ V}$$

- Time evolution of ÷2/÷4 clock IC output voltages and frequency for all 5 packaged chips subjected to prolonged 500 °C testing.

- After initial burn-in, output characteristics change < 10%.</li>

- 3 of 5 chips remain functioning under 500 °C test today.

National Aeronautics and Space Administration

## Wafer 10.1 500 °C Durability Results

Table I. 500 °C JFET IC Test Summary

| Packaged  | r    | 500 °C  | Test      |

|-----------|------|---------|-----------|

| IC Sample | (mm) | Time    | Status    |

| RAM #1    | 13.4 | 1525 h  | Suspended |

| RAM #2    | 6.7  | 10100 h | Running   |

| Clock #1  | 24.2 | 470 h   | Failed    |

| Clock #2  | 15.3 | 10500 h | Running   |

| Clock #3A | 12.4 | 9677 h  | Running   |

| Clock #3B | 12.4 | 9677 h  | Running   |

| Clock #3C | 13.4 | 2090 h  | Failed    |

First reported demonstrations of 1+ year (8766+ hours) 500 °C integrated circuit operation (in any semiconductor).

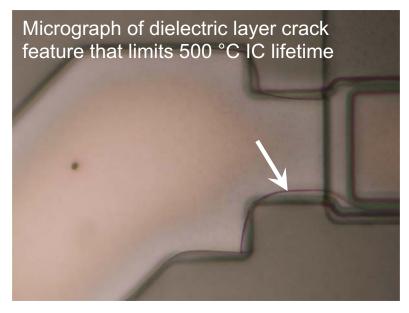

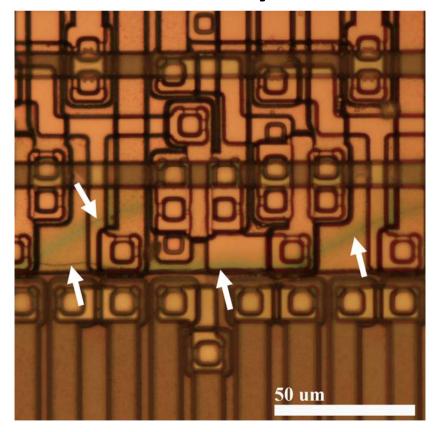

## Clock #1 IC Failure Analysis

Electrical failure mode (at 470 hours): 21-stage ring oscillator ceased functioning.

White arrows denote examples of dielectric cracks and metal trace discoloration observed in the ring oscillator sub-circuit, symptoms of the primary 500 °C IC failure mechanism described previously<sup>1</sup>.

<sup>1</sup>D. J. Spry, et al., Proc. IMAPS High Temperature Electronics Conf., 2016, pp. 249-256.

### **Future Work**

Continue development and demonstrations of increasingly capable 4H-SiC SiC JFET integrated circuits.

- Improve IC durability by reducing or eliminating dielectric crack formation.

- Improve IC capability by upscaling to higher chip complexity.

- Improve IC validation with larger statistical data sets, full flight environment electrical testing.

- Mature technology towards NASA mission insertion and commercialization.

## Summary

# First demonstration of 1+ year of 500 °C ambient temperature integrated circuit operation.

- 4H-SiC JFET ICs up to 195 transistors/circuit.

- First 500 °C durable random access memory (RAM).

## NASA Technology Access

Prototype IC designs meeting 4H-SiC JFET IC guidelines could potentially be fabricated by NASA Glenn, under negotiated collaborative Space Act Agreement:

- Contact: https://technology.grc.nasa.gov, Priscilla.S.Diem@nasa.gov.

- Tech guidelines: https://sic.grc.nasa.gov/files/HiTEC2016-NeudeckV1A.pdf