#### Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits

- D. J. Spry<sup>1</sup>, P. G. Neudeck<sup>1</sup>, and C. W. Chang<sup>2</sup>

- 1 NASA Glenn Research Center, 21000 Brookpark Road, M.S. 77-1, Cleveland, OH 44135 USA

- 2 Vantage Partners LLC, NASA Glenn Research Center, 21000 Brookpark Road, M.S. 77-1, Cleveland, OH 44135 USA

- E-mail: David.J.Spry@nasa.gov

#### SiC Electronics Benefits to NASA Missions

#### **Aeronautics Research** Mission Directorate ARMD

**Intelligent Propulsion Systems**

#### Hybrid Electric & Turbo Electric Aircraft

9.4 Mpa = 92.7 times Earth pressure 460 °C + chemical composition found at the surface of Venus (CO<sub>2</sub>, N<sub>2</sub>, SO<sub>2</sub>, H<sub>2</sub>O, CO, OCS, HCl, HF, and H<sub>2</sub>S)

<sup>1</sup>T. Kremic, et al., 48<sup>th</sup> Lunar and Planetary Science, 2017, 2986.

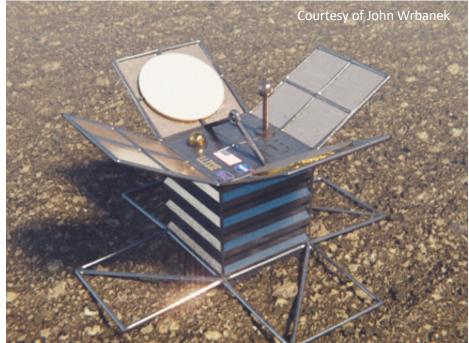

**Space Mission Directorate SMD Venus Surface Exploration**

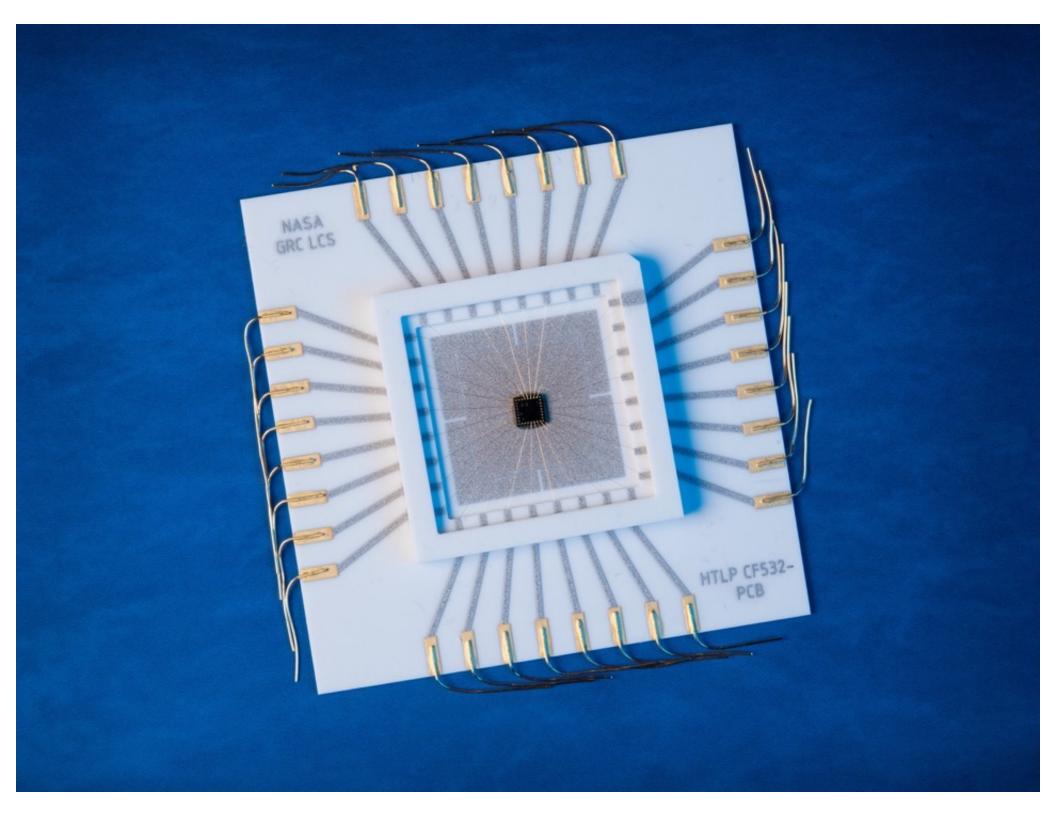

LLISSE = Long-Life In-Situ Solar System Explorer<sup>1</sup>

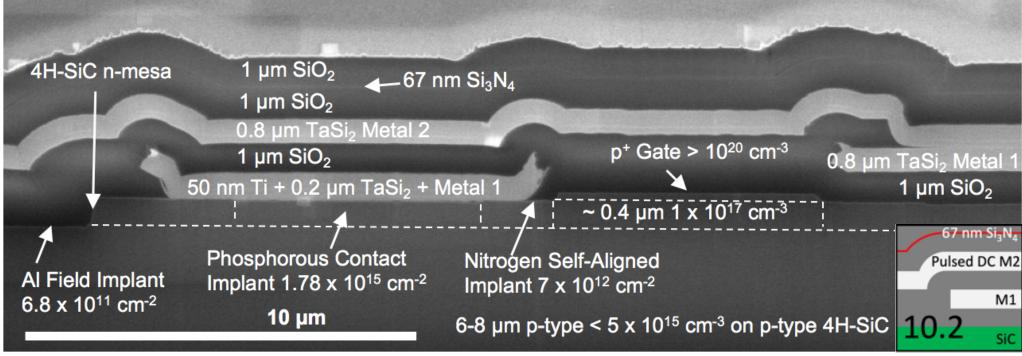

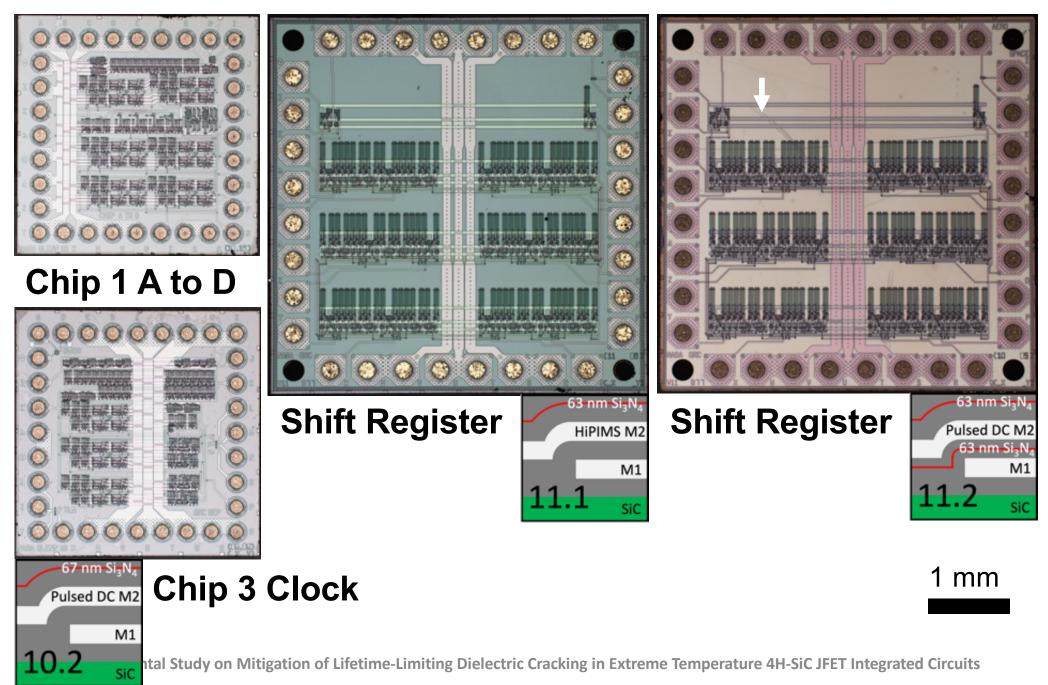

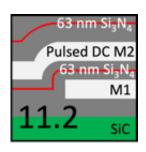

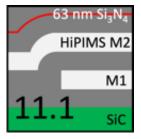

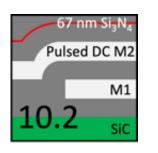

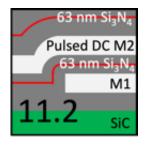

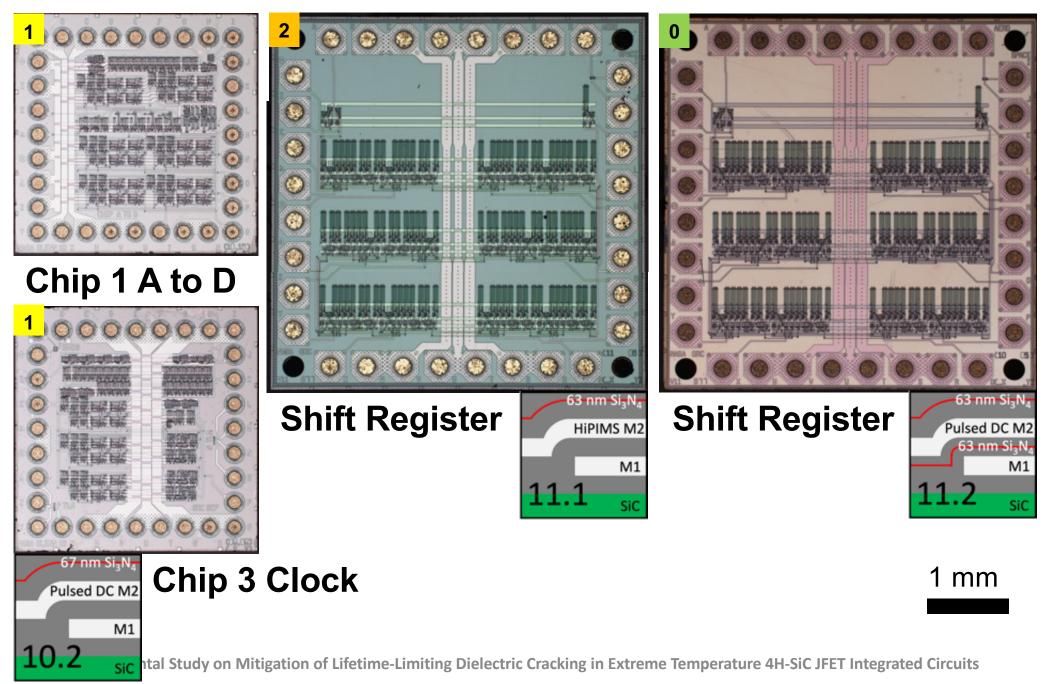

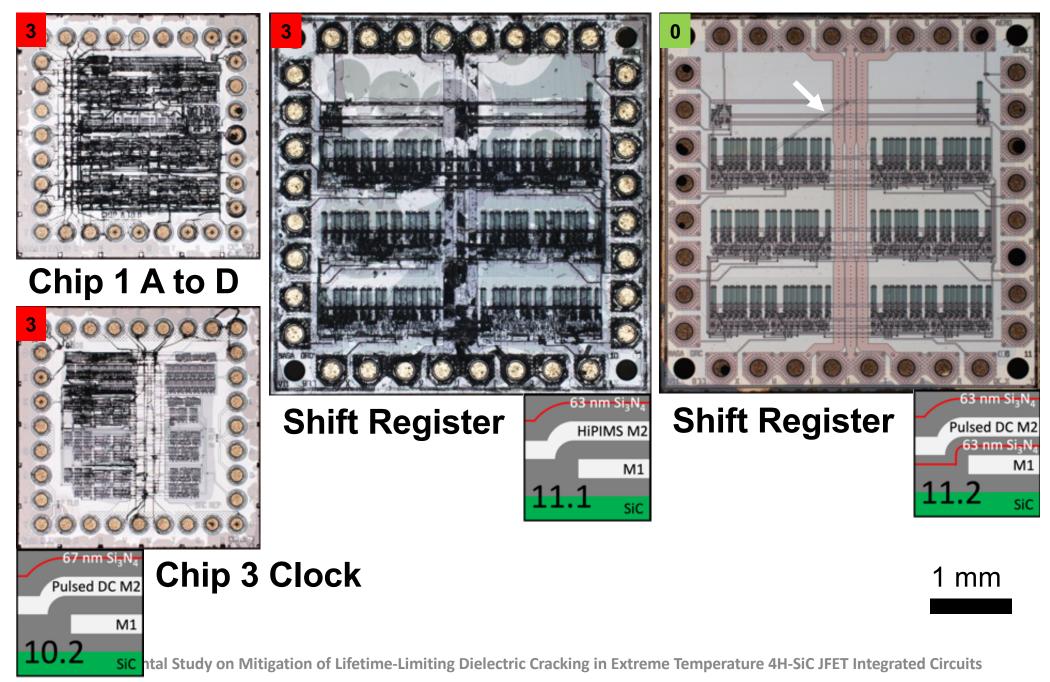

### JFET IC Wafer 10.2 vs 11.1 vs 11.2 Process

- 10.2 Pulsed-DC TaSi<sub>2</sub> and 1 Si<sub>3</sub>N<sub>4</sub> layer above Metal 2

- 11.1 HiPIMS TaSi<sub>2</sub> and 1 Si<sub>3</sub>N<sub>4</sub> layer above Metal 2

- 11.2 Pulsed-DC TaSi<sub>2</sub> & Two Si<sub>3</sub>N<sub>4</sub> layers

-above Metal 2

-between Metal 1 and Metal 2

# SiO<sub>2</sub> deposited at 720 °C by LPCVD using TEOS and 63nm stoichiometric Si<sub>3</sub>N<sub>4</sub> deposited also at 720 °C by LPCVD using DCS and NH<sub>3</sub>.

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits3

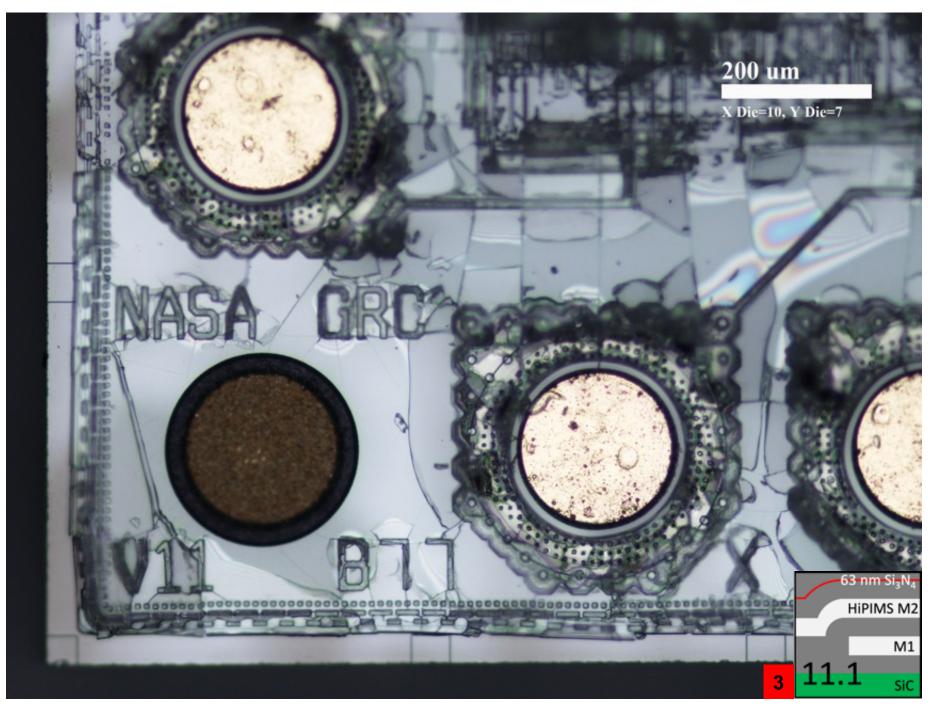

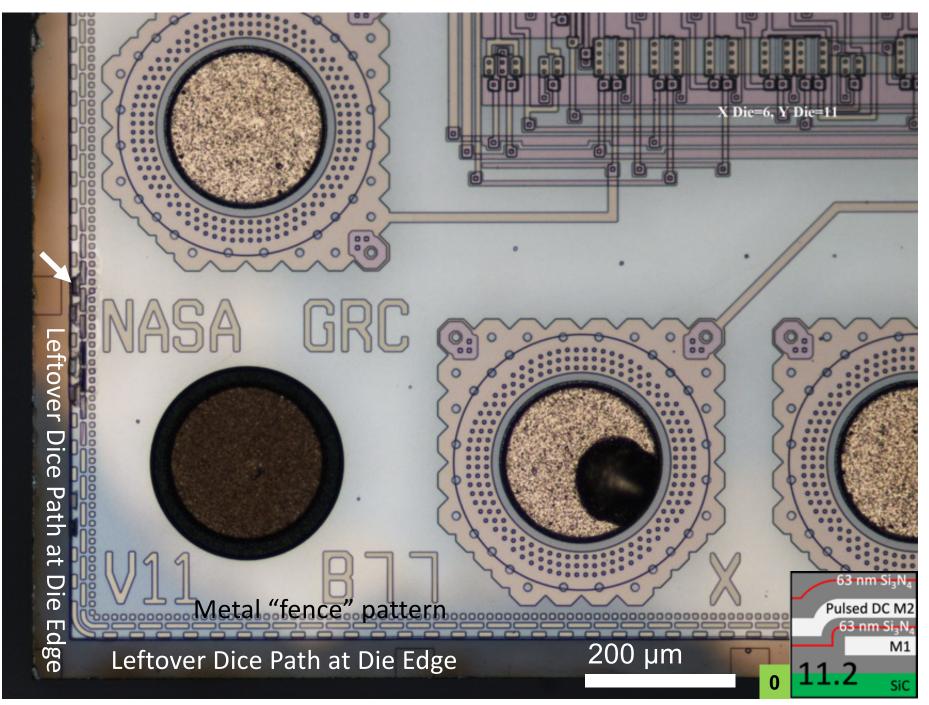

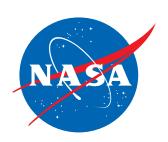

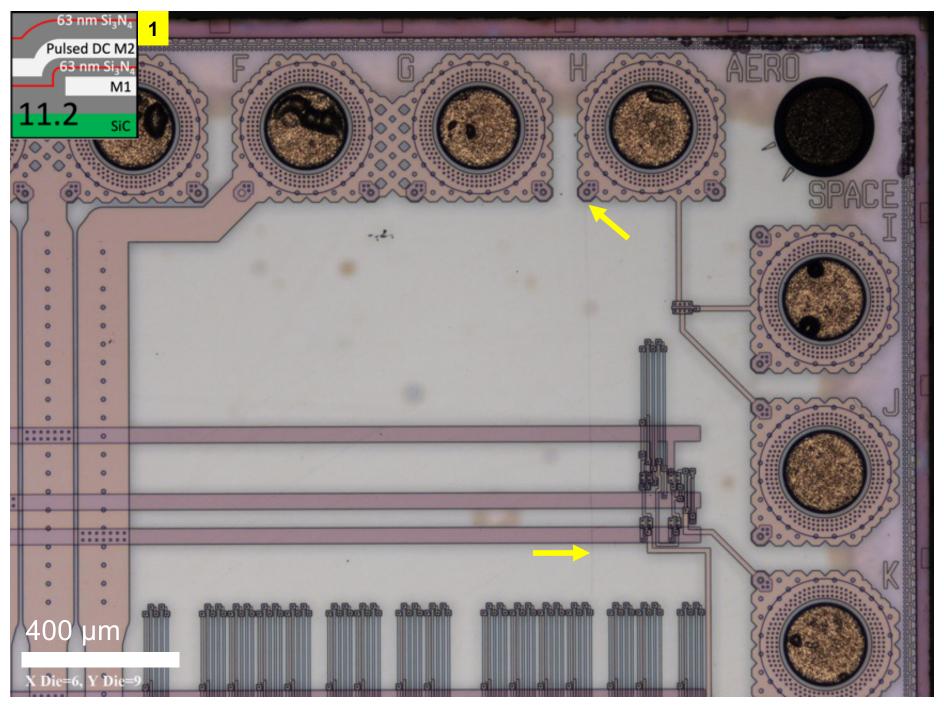

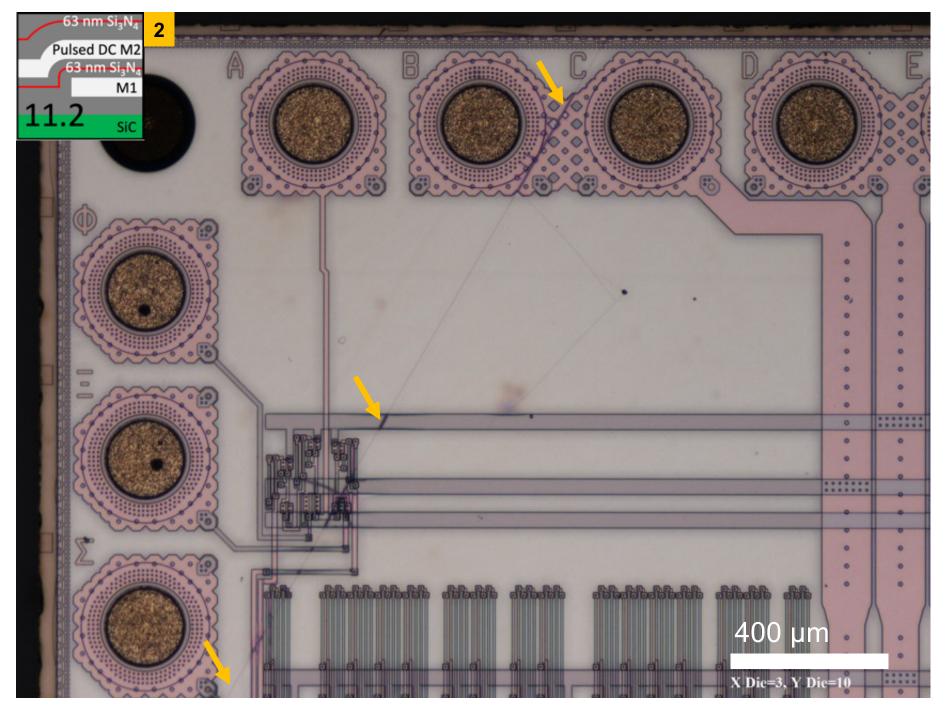

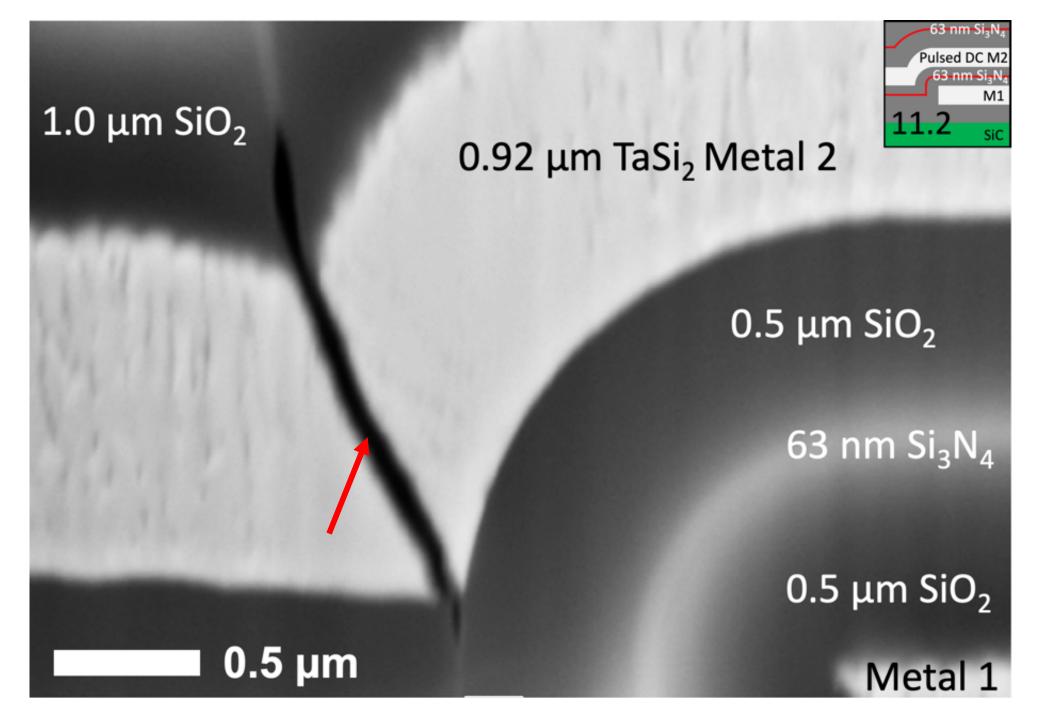

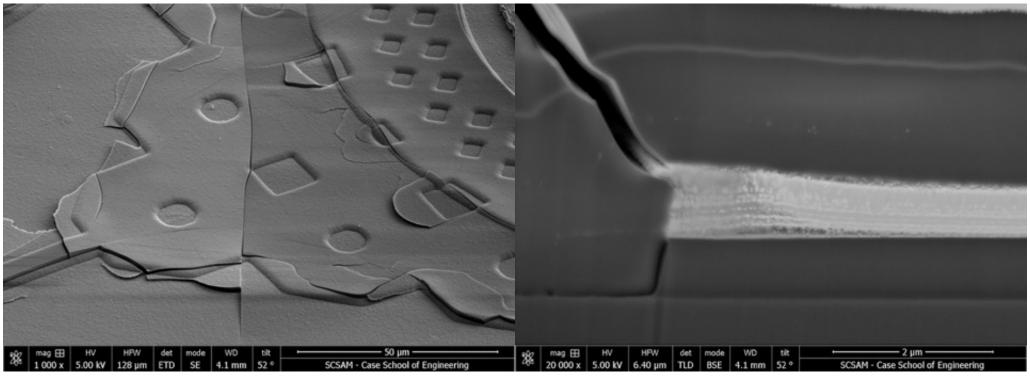

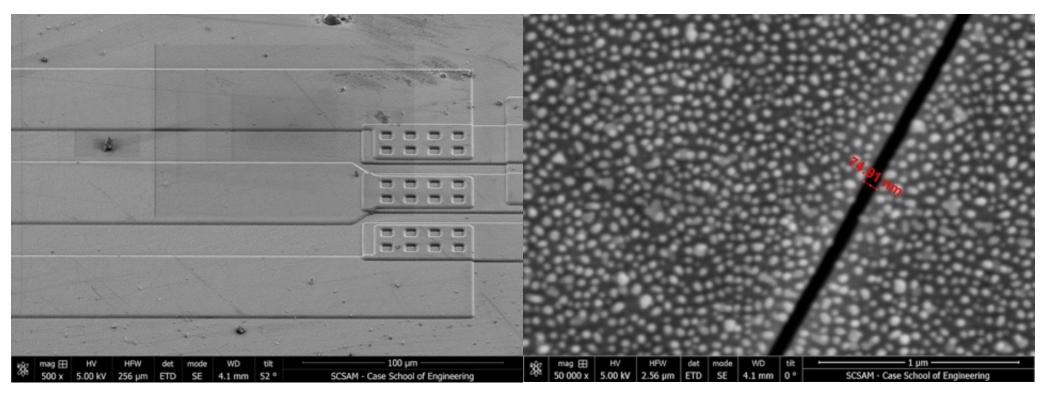

#### JFET IC Wafer 11.2 - Metal 2 Crack

## JFET IC Wafer 10.2 vs 11.1 vs 11.2 Layout

#### • 10.2

3 X 3 mm, active area 2 X 2 mm, 6 μm gate & resistors, 175 transistors >10,000 hours at 500 °C in air ambient 9 die versions Die tested in the report Chip 1 A to D Chip 3 Clock IC ÷2 ÷ 4 (some non-working)

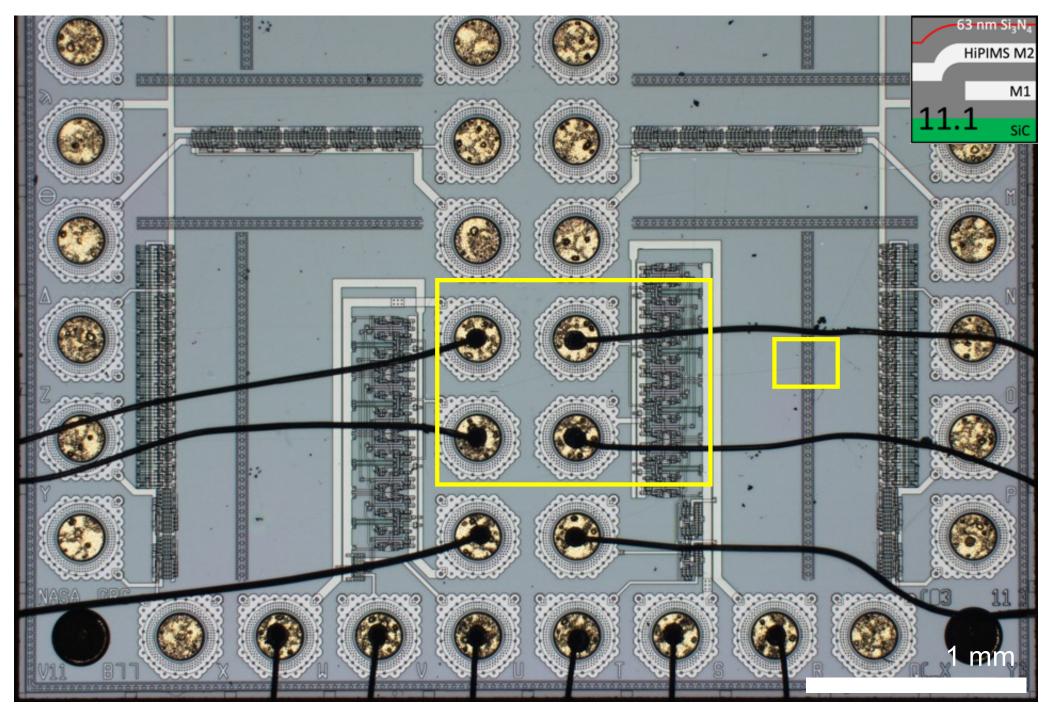

#### • 11.1 & 11.2

4.65 X 4.65mm, active area 3.55 X 3.55 mm 6 μm gate, 3 μm resistors, 348 transistors most complex ~1000 transistors

19 die versions

Die tested in this report

Chip 7 Shift Registers (non-working)

#### Chip 13B LLISSE RF Transmitter & Ring Oscillators

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits5

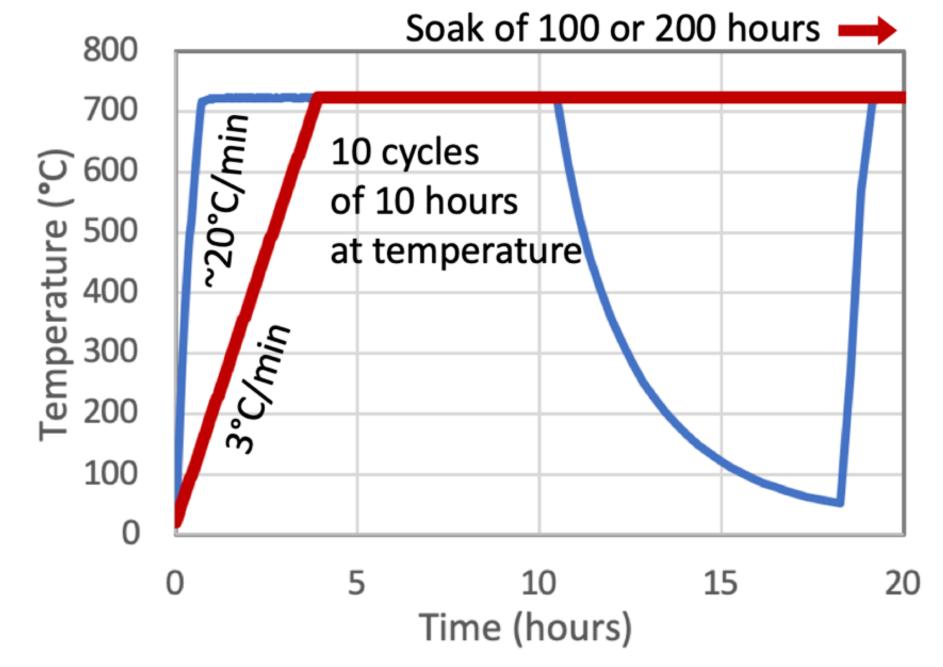

### 10 cycles 10 hrs. at 500 °C Pre-Test Images

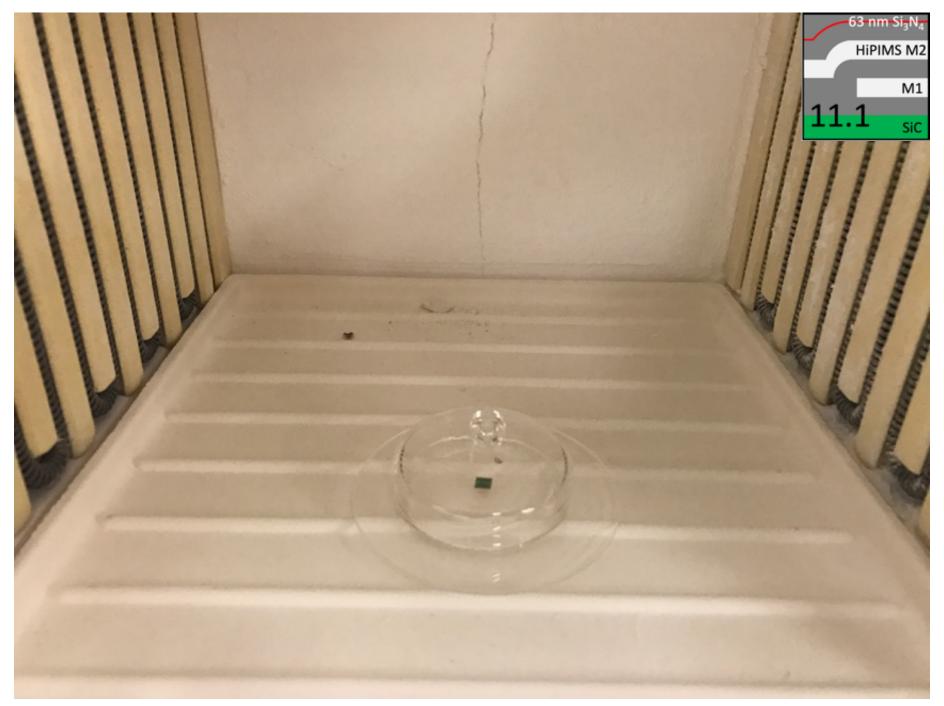

#### Unpackaged, Quartz, in Air Ambient Ovens

# 10 cycles 10 hrs. / 100hrs. / 200hrs. 500, 600, 720, and 800 °C

# Graded Results of Thermal Testing

| Version 10.2 C1   |     |     |     | °C  |

|-------------------|-----|-----|-----|-----|

| Anolog to Digital | 500 | 600 | 720 | 800 |

| 100 hours         | 1   | 1   | 3   | 3   |

| 200 hours         | 1   | 2   | 3   | 3   |

| 10-10hr cycle     | 1   | 2   | 3   |     |

| Version 11.1 C7 |     |     |     | °C  |

|-----------------|-----|-----|-----|-----|

| Shift Register  | 500 | 600 | 720 | 800 |

| 100 hours       | 1   | 3   | 3   | 3   |

| 200 hours       | 3   | 3   | 3   | 3   |

| 10-10hr cycle   | 2   | 3   | 3   |     |

| Version 10.2 C | 3   |     |     | °C  |

|----------------|-----|-----|-----|-----|

| Clock ÷2 ÷4    | 500 | 600 | 720 | 800 |

| 100 hours      | 1   | 0   | 3   | 0   |

| 200 hours      | 2   | 2   | 3   | 3   |

| 10-10hr cycle  | 1   | 2   | 3   |     |

| Version 11.2 C7 |     |     |     | °C  |

|-----------------|-----|-----|-----|-----|

| Shift Register  | 500 | 600 | 720 | 800 |

| 100 hours       | 0   | 0   | 0   | 1   |

| 200 hours       | 0   | 2   | 0   | 3   |

| 10-10hr cycle   | 0   | 0   | 0   |     |

| Good    | 0 | No cracks             |

|---------|---|-----------------------|

| Problem | 1 | TaSi2 not dicolored   |

| Fail    | 2 | TaSi2 very discolored |

| Ugly    | 3 | Dieletric pealed      |

63 nm Si<sub>a</sub>l

**HiPIMS M2**

M1

SiC

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits

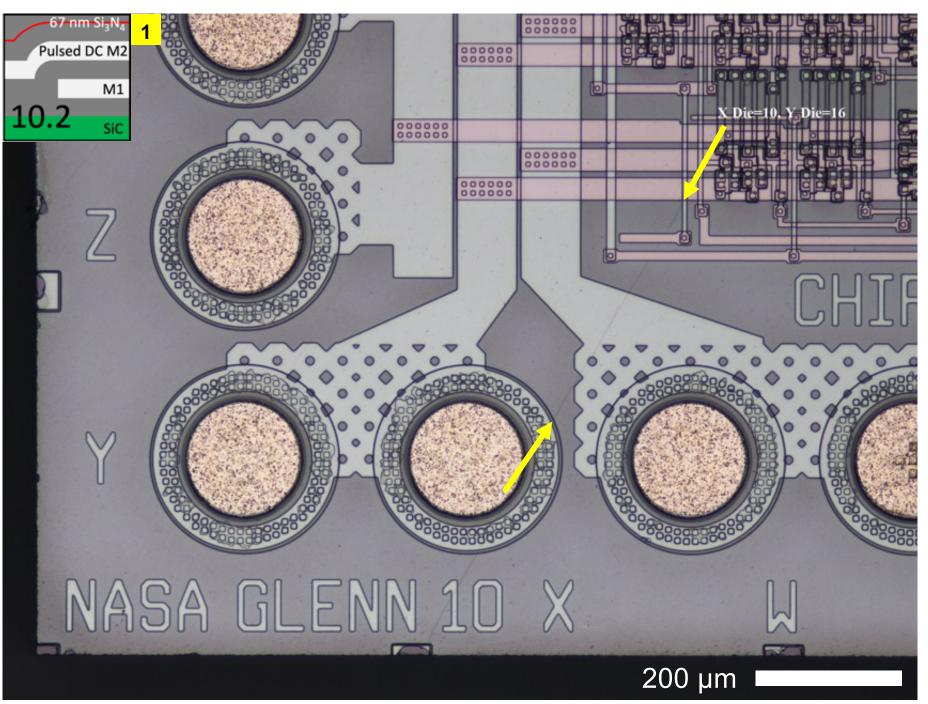

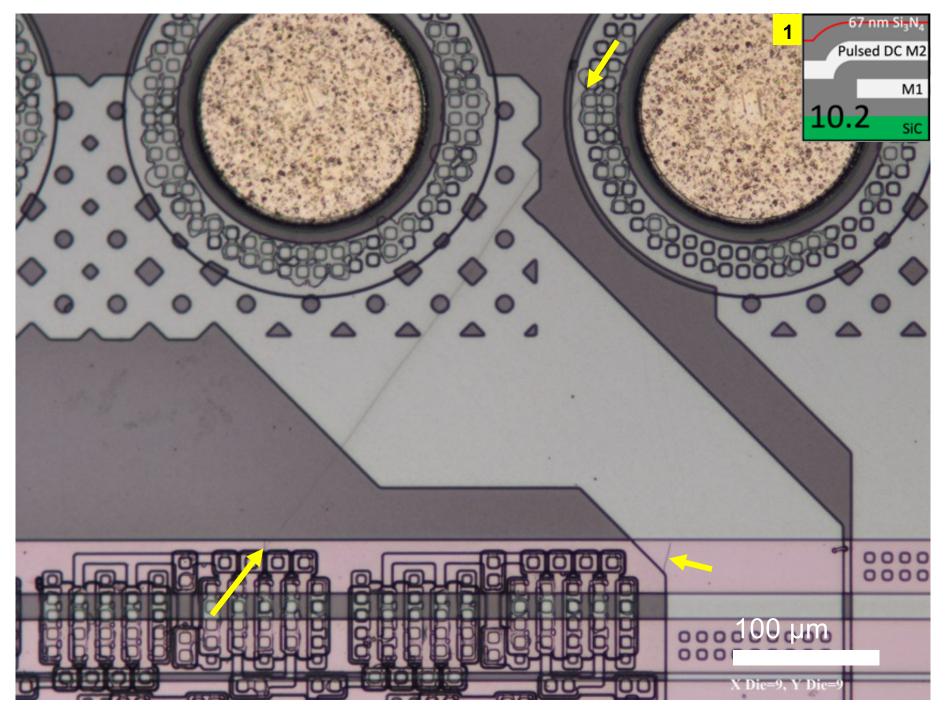

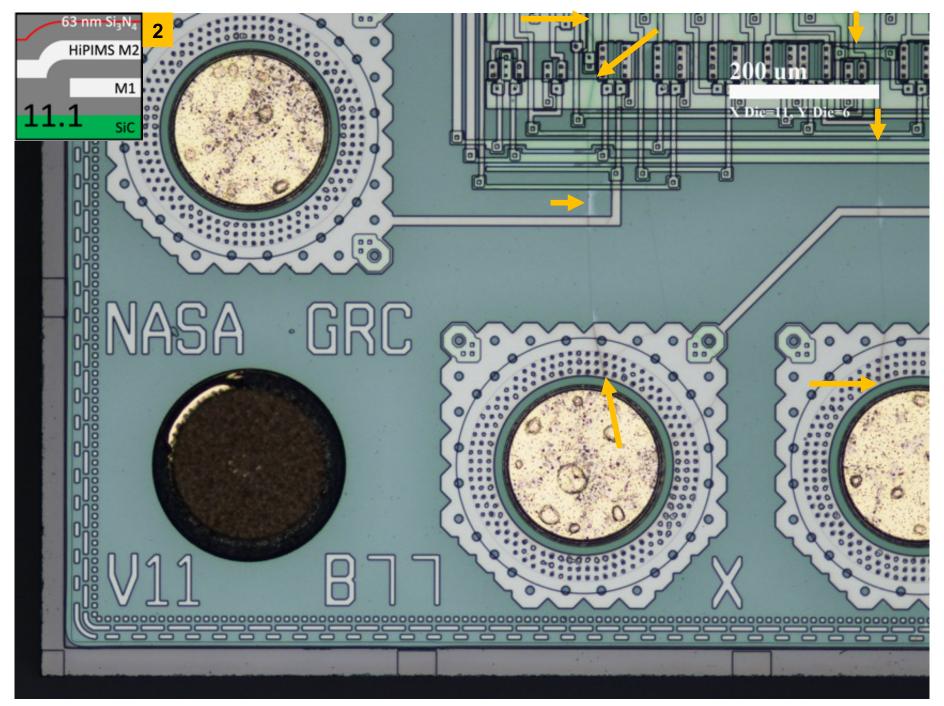

### Closer look at 10-10hr cycle 500 °C

| Version 10.2 C1   |     |     |     | °C  |

|-------------------|-----|-----|-----|-----|

| Anolog to Digital | 500 | 600 | 720 | 800 |

| 100 hours         | 1   | 1   | 3   | 3   |

| 200 hours         | 1   | 2   | 3   | 3   |

| 10-10hr cycle     | 1   | 2   | 3   |     |

| Version 11.1 C7 |     |     |     | °C  |

|-----------------|-----|-----|-----|-----|

| Shift Register  | 500 | 600 | 720 | 800 |

| 100 hours       | 1   | 3   | 3   | 3   |

| 200 hours       | 3   | 3   | 3   | 3   |

| 10-10hr cycle   | 2   | 3   | 3   |     |

| Version 10.2 C3 |     |     |     | °C  |

|-----------------|-----|-----|-----|-----|

| Clock ÷2 ÷4     | 500 | 600 | 720 | 800 |

| 100 hours       | 1   | 0   | 3   | 0   |

| 200 hours       | 2   | 2   | 3   | 3   |

| 10-10hr cycle   | 1   | 2   | 3   |     |

| Version 11.2 C7 |     |     |     | °C  |

|-----------------|-----|-----|-----|-----|

| Shift Register  | 500 | 600 | 720 | 800 |

| 100 hours       | 0   | 0   | 0   | 1   |

| 200 hours       | 0   | 2   | 0   | 3   |

| 10-10hr cycle   | 0   | 0   | 0   |     |

| Good    | 0 | No cracks             |

|---------|---|-----------------------|

| Problem | 1 | TaSi2 not dicolored   |

| Fail    | 2 | TaSi2 very discolored |

| Ugly    | 3 | Dieletric pealed      |

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits

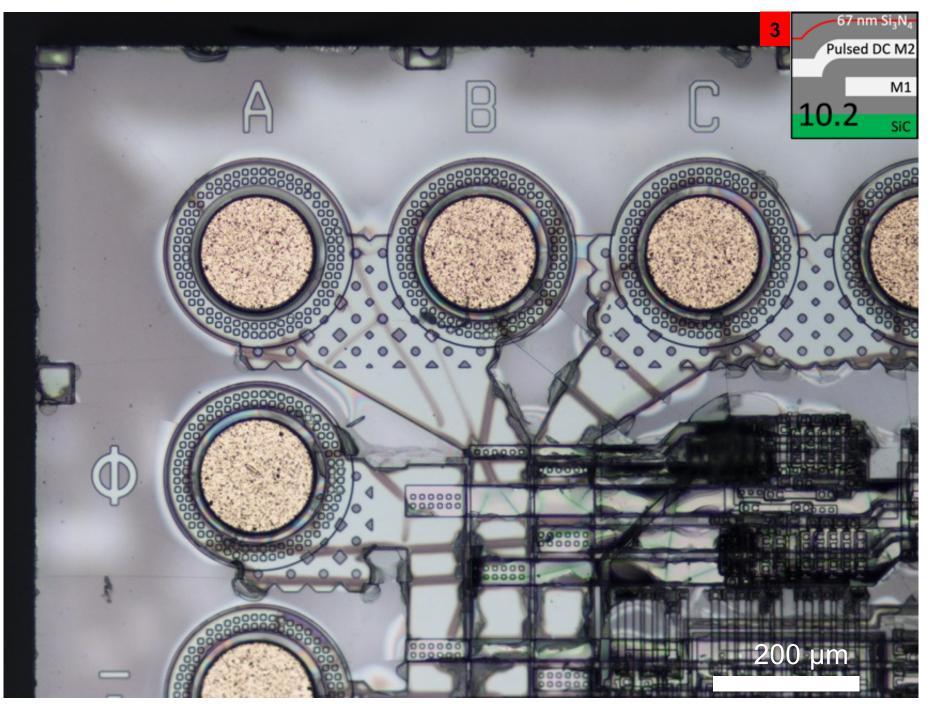

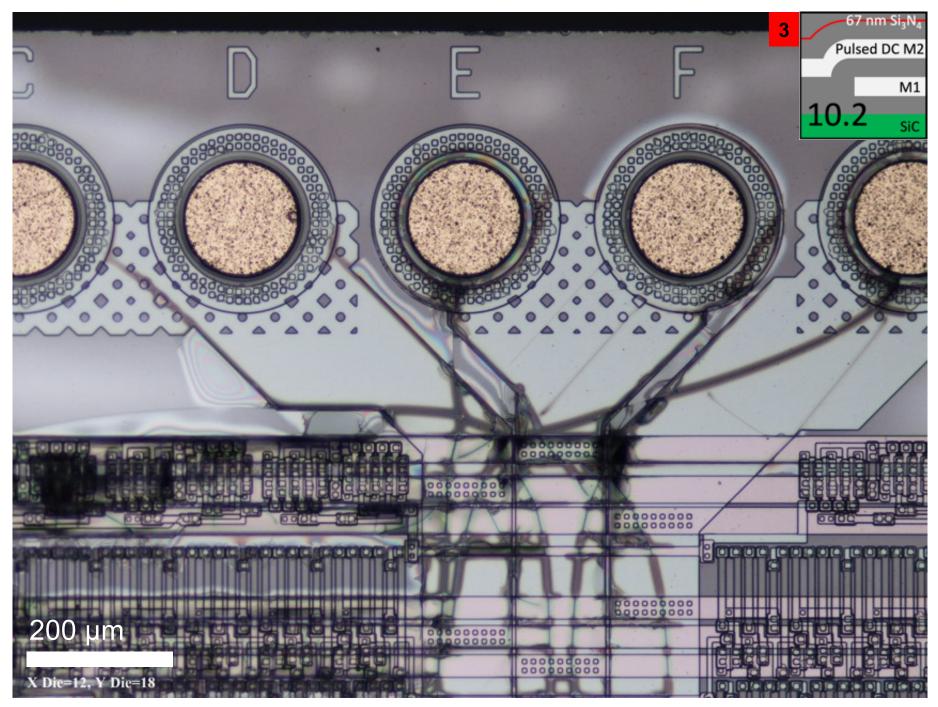

### 10 cycles 10 hrs. at 500 °C Post-Test Images

#### 10 cycles 10 hrs. at 500 °C 10.2 Chip 1

### 10 cycles 10 hrs. at 500 °C 10.2 Chip 3

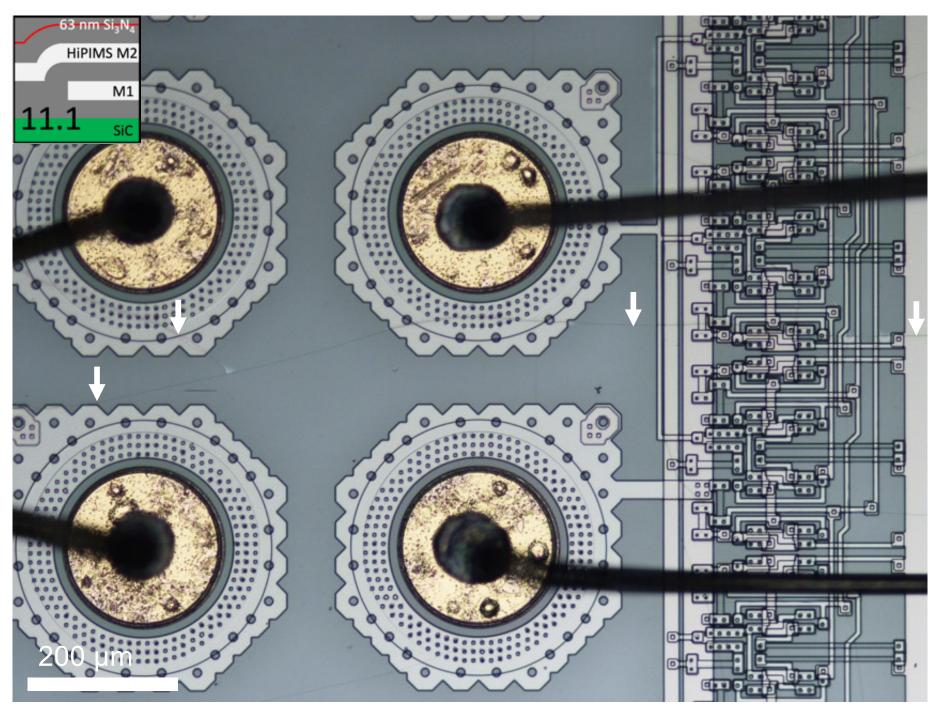

### 10 cycles 10 hrs. at 500 °C 11.1 Chip 7

| Closer loc                            | ok a          | at 1        | 0-1      | LOh           | r cycle 720                              | °C            |          | <br>11.1    | M1       |

|---------------------------------------|---------------|-------------|----------|---------------|------------------------------------------|---------------|----------|-------------|----------|

| Version 10.2 C1                       |               |             |          | °C            | Version 11.1 C7                          |               |          |             | °C       |

| Anolog to Digital                     | 500           | 600         | 720      | 800           | Shift Register                           | 500           | 600      | 720         | 800      |

| 100 hours                             | 1             | 1           | 3        | 3             | 100 hours                                | 1             | 3        | 3           | 3        |

| 200 hours                             | 1             | 2           | 3        | 3             | 200 hours                                | 3             | 3        | 3           | 3        |

| 10-10hr cycle                         | 1             | 2           | 3        |               | 10-10hr cycle                            | 2             | 3        | 3           |          |

|                                       |               |             |          |               |                                          |               |          |             |          |

| Version 10.2 C3                       |               |             |          | °C            | Version 11.2 C7                          |               |          |             | °C       |

|                                       |               |             |          | -             |                                          |               |          |             |          |

| Clock ÷2 ÷4                           | 500           | 600         | 720      | 800           | Shift Register                           | 500           | 600      | 720         | 800      |

|                                       |               | 600<br>0    | 720<br>3 |               |                                          |               | 600<br>0 | 720<br>0    | 800<br>1 |

| Clock ÷2 ÷4                           | 500           |             |          | 800           | Shift Register                           | 500           |          | _           |          |

| Clock ÷2 ÷4<br>100 hours              | 500<br>1      | 0           | 3        | 800<br>0      | Shift Register<br>100 hours              | 500<br>0      | 0        | 0           | 1        |

| Clock ÷2 ÷4<br>100 hours<br>200 hours | 500<br>1<br>2 | 0<br>2<br>2 | 3<br>3   | 800<br>0<br>3 | Shift Register<br>100 hours<br>200 hours | 500<br>0<br>0 | 0<br>2   | 0<br>0<br>0 | 1        |

63 nm S

s nm Si<sub>a</sub>N

M1

SiC

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits

TaSi2 very discolored

Dieletric pealed

Fail

Ugly

M1

SiC

2

3

### 10 cycles 10 hrs. at 720 °C Post-Test Images

### 10 cycles 10 hrs. at 720 °C 10.2 Chip 1

### 10 cycles 10 hours at 720 °C 10.2 Chip 3

### 10 cycles 10 hours at 720 °C 11.1 Chip 7

### 10 cycles 10 hours at 720 °C 11.2 Chip 7

#### Electrical Failure 5<sup>th</sup> cycle 500 °C 10.2 Chip 13B

#### Electrical Failure 5<sup>th</sup> cycle 500 °C 10.2 Chip 13B

#### Electrical Failure 5<sup>th</sup> cycle 500 °C 10.2 Chip 13B

# Summary

- The addition of a second LPCVD stochiometric Si<sub>3</sub>N<sub>4</sub> layer reduced the amount of dielectric cracking.

- Etching through to bare SiC between die, reduces dielectric cracks form dicing process.

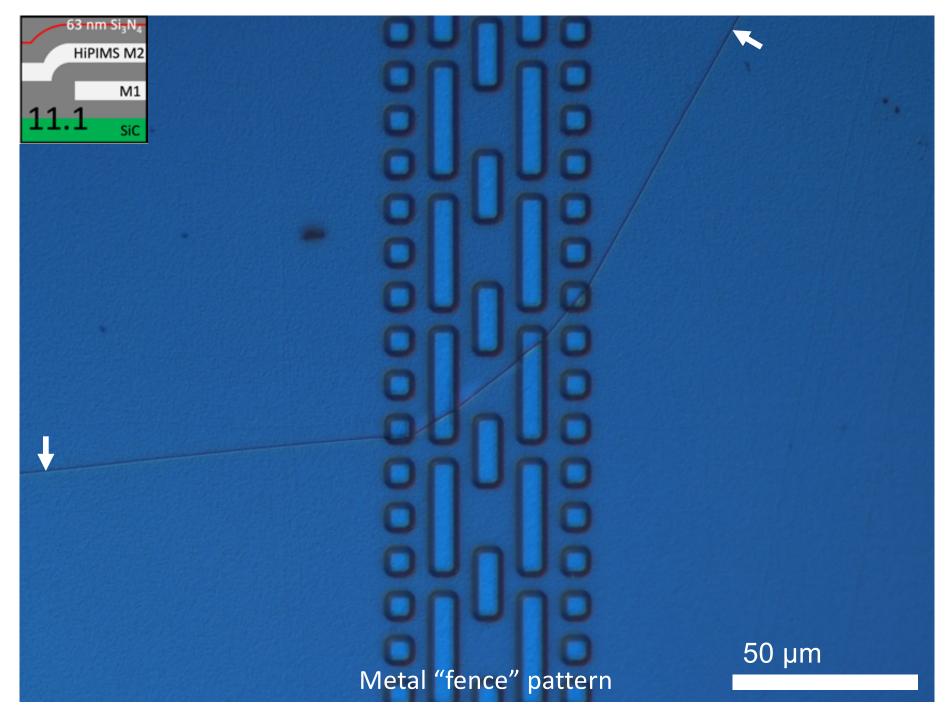

- Adding a metal 1 "fence" pattern deflected dielectric cracks from propagation into neighboring devices.

#### Acknowledgements Funded by NASA SMD-LLISSE

#### HX5 Sierra

- Kelley Moses

- Jose Gonzalez

- Michelle Mrdenovich

- Ariana Miller

- Frank Lam

#### Vantage Partners LLC

• Dorothy Lukco

#### Science Applications International Corporation (SAIC)

• Alain Izadenegahdar

#### **Case Western Reserve University**

• Amir Avishai

#### **Ohio Aerospace Institute**

• Liangyu Chen

#### **NASA Glenn Research Center**

- Robert Buttler

- Glenn Beheim

- Stephanie Booth

- Srihari Rajgopal

- Jennifer Jordan

- George Ponchak

- Michael Lienhard

- Michael Krasowski

- Norman Prokop

- Lawrence Greer

- John Wrbanek

- Diana Centeno-Gomez

- Gary Hunter

- Timothy Palinski

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuita5

#### 100 hours at 800 °C Post-Test

11.2

#### 200 hours at 600 °C Post-Test

11.2

#### 200 hours at 800 °C Post-Test

**Experimental Stu**

### JFET IC Wafer 11.2 - Metal 2 Crack Zoom-in

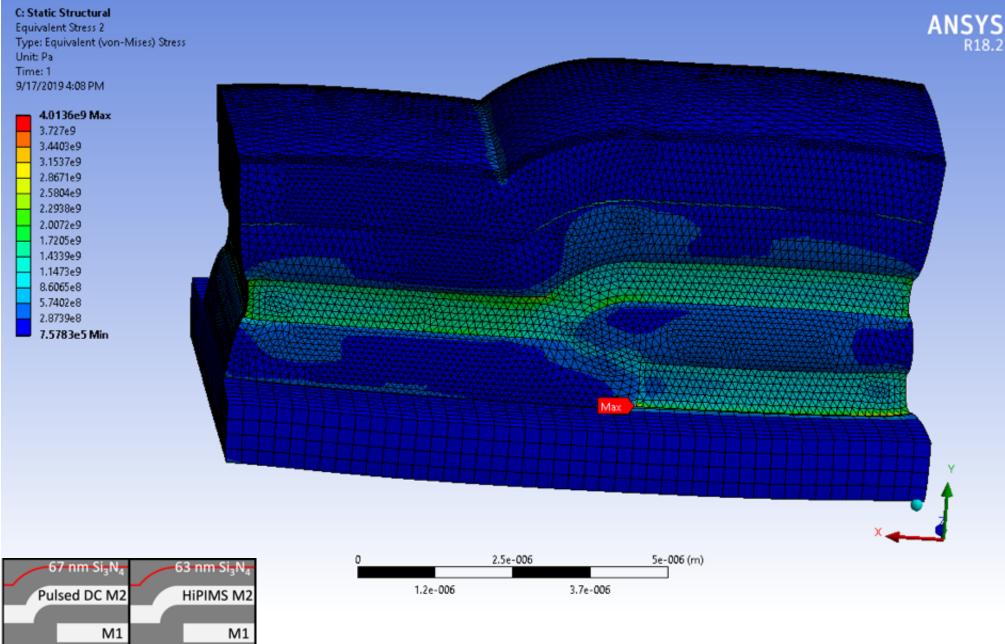

### Max Stress Point Ansys FEA 10.2 and 11.1

SiC

SiC

gation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits

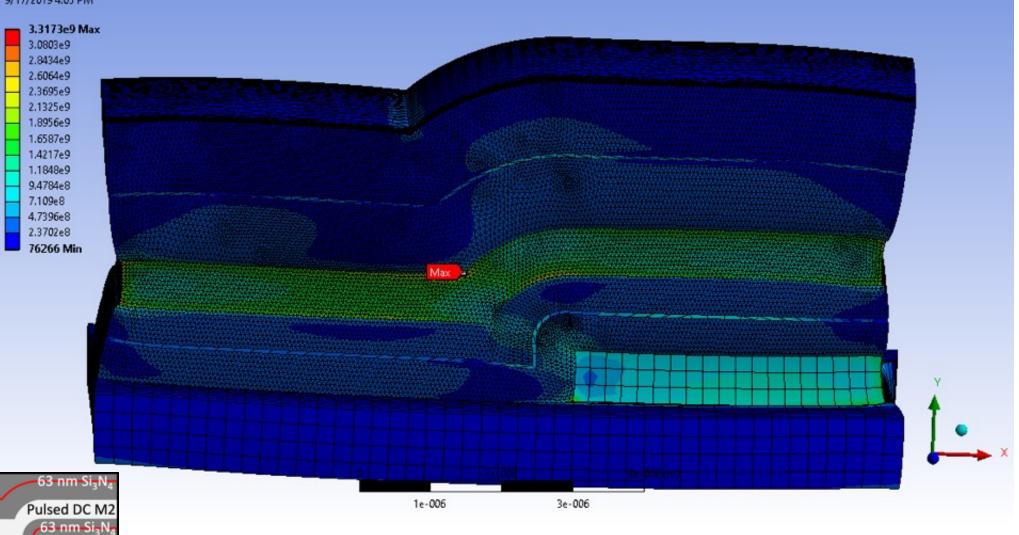

#### Max Stress Point Ansys FEA

# 11.2

ANSYS

R18.2

#### E: Static Structural - mesh curv wrefine 720 to 22C

Equivalent Stress 2 Type: Equivalent (von-Mises) Stress Unit: Pa Time: 1 9/17/2019 4:05 PM

M1

SiC

ntal Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuits

# **Future Work**

Current work was  $SiO_2$  deposited at 720 °C by LPCVD using TEOS and 63nm stoichiometric  $Si_3N_4$  deposited also at 720 °C by LPCVD using DCS and  $NH_3$ .

Make test metal insulator metal MIM capacitors to evaluate:

- 3 stoichiometric silicon nitride layers

- Thicker Si<sub>3</sub>N<sub>4</sub> layers

- Stoichiometric  $Si_3N_4$  deposited at 800 °C instead of 720 °C

- Low-stress silicon nitride layers

- High Temperature (HT) SiO<sub>2</sub> with dichlorosilane (DCS) and ammonia NH<sub>3</sub>.

- Oxynitride

- HT oxide in same run as stoichiometric Si<sub>3</sub>N<sub>4</sub>

- Other precursors for stoichiometric Si<sub>3</sub>N<sub>4</sub> such as trisilylamine (TSA) or neopentasilane (NPS) + NH<sub>3</sub> for use with TEOS in a sign tube LPCVD

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuit33

### **Typical Crack Propagation in Earth Air**

- This sample was at 727 °C sample and a old (Version 9.2) design.

Same kind of behavior when seen on some 500 °C samples.

- Cracks related to dicing, handling, design rules, and bonding.

- Various degrees of oxidation and pealing seen.

- Oxidation of TaSi<sub>2</sub> surface can be many 10s of microns wide.

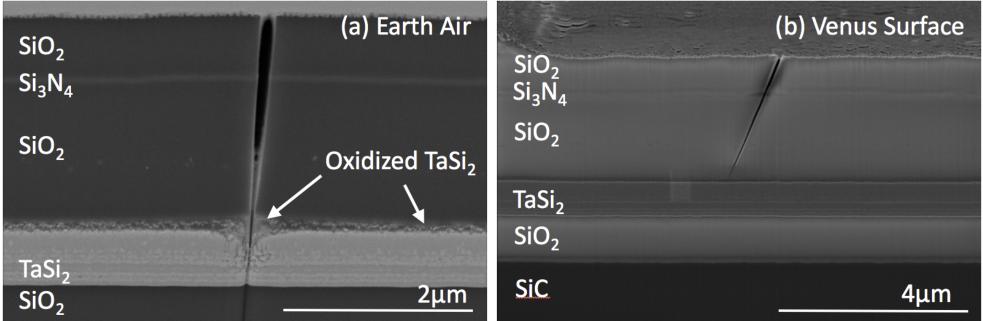

#### Crack at Venus Surface Conditions

- Only one crack seen on entire sample exposed to Venus.

- Found via optical microscope and then examined on SEM. Hard to find with FESEM.

- Very small (~ 75 nm) when viewed from the top.

### Venus Environment Durability FIB FESEM

(a) Crack typical of prolonged T  $\ge$  500 °C testing in air (727 °C for this sample)

- In Earth environment, the crack allows the top surface of the TaSi<sub>2</sub> film to oxidize which exacerbates failure.

- (b) Crack in IC sample tested in Venus surface condition.

- In Venus environment, the crack reaches the top of the TaSi<sub>2</sub> but does not propagate through the TaSi<sub>2</sub> and there is no observable evidence of TaSi<sub>2</sub> film oxidation.

#### STARC-ABL: Single-aisle Turboelectric AiRCraft with Aft Boundary Layer propulsion

Experimental Study on Mitigation of Lifetime-Limiting Dielectric Cracking in Extreme Temperature 4H-SiC JFET Integrated Circuit38