# Effect of High-κ Dielectric Layer on 1/f Noise Behavior in Graphene Field-Effect Transistors

Yifei Wang, 14 Vinh X. Ho, 14 Zachary. N. Henschel, 1 Michael P. Cooney, 2 and Nguyen Q. Vinh 1\*

<sup>1</sup> Department of Physics and Center for Soft Matter and Biological Physics, Virginia Tech, Blacksburg, VA 24061, USA

<sup>2</sup> NASA Langley Research Center, Hampton, Virginia 23681, USA

<sup>†</sup>Yifei Wang and Vinh X. Ho contributed equally to this work.

\* Corresponding author: vinh@vt.edu; phone: 1-540-231-3158

**Keywords:** Graphene, field-effect transistor, flicker noise, 1/f noise, high-κ dielectric thin film, atomic layer deposition

## **ABSTRACT**

We report the 1/f noise characteristics at low-frequency in graphene field-effect transistors that utilized a high- $\kappa$  dielectric tantalum oxide encapsulated layer (a few nanometers thick) placed by atomic layer deposition on Si<sub>3</sub>N<sub>4</sub>. A low-noise level of  $\sim 2.2 \times 10^{-10}$  Hz<sup>-1</sup> has been obtained at f=10 Hz. The origin and physical mechanism of the noise can be interpreted by the McWhorter context, where fluctuations in the carrier number contribute dominantly to the low-frequency noise. Optimizing fabrication processes reduced the number of charged impurities in the graphene field-effect transistors. The study has provided insights into the underlying physical mechanisms of the noise at low-frequency for reducing the noise in graphene-based devices.

## INTRODUCTION

The outstanding electrical properties of graphene (a single atomic layer) have received considerable attention for future electronics including high speed transistors, photodetectors, components of integrated circuits, flexible and wearable devices, touch screens, ultrasensitive sensors.<sup>1-3</sup> In these applications, the flicker or low-frequency 1/f noise (f < 100 kHz) is the key factor of the device performance. The amplitude of the flicker noise defines the limit of the operation of electronics devices.<sup>4-8</sup> Therefore, to enhance the performance of graphene devices, several configurations have been realized to scale down the flicker noise. Graphene field-effect transistors (GFETs) containing a few graphene layers helped reduce noise level. GFETs with the graphene channel on h-BN or encapsulated by two h-BN layers, which reduce charged impurities and trapping sites, can suppress the flicker noise by a factor of 5 to 10 times compared to that of graphene on Si/SiO<sub>2</sub> substrates. 10-12 The noise at low-frequency of graphene devices can be reduced through irradiation.<sup>5, 13</sup> Another approach is to employ a high-κ dielectric layer that can protect graphene from exposure conditions to prevent the increase of the noise. Nevertheless, the mobility degradation in graphene can occur when the dielectric layer is grown atop graphene. The flicker noise in GFET devices with an  $HfO_2$  high- $\kappa$  dielectric thin film grown by atomic layer deposition (ALD) has been realized. 14 A reduction of the low-frequency noise with a top-gated GFET using Al<sub>2</sub>O<sub>3</sub> as gate-dielectric has been reported.<sup>15</sup> However, a high dark current in the milliampere scale of such GFETs is an obstruction for many applications. For example, the high dark current in GFET photodetectors causes a high shot noise, and thus, sets a high-level noise floor of these devices. These reports mostly focused on GFETs under the voltage control of the top-gate. However, the back-gated FETs are the backbone for a variety of electronic applications. Therefore, it is essential to improve GFETs with low noise in the backgated configuration, which is covered by a high-κ dielectric thin film with a few nanometers thick. Among various high-κ dielectric materials, we have focused on the tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) with high dielectric constant ( $\kappa = 25 - 40$ ) and good chemical and thermal stability. The material has been used in many applications in solar energy conversion as well as microelectronics, including photocatalytic materials, 16 charge-trapping for nonvolatile resistive random access memories, 17 atomic switches, 18 capacitors, insulators, <sup>19</sup> thin-film electroluminescent devices, <sup>20</sup> and high-speed elements. <sup>21</sup>

Here, we report the reduction of the flicker noise in GFETs by engineering the high-quality dielectric tantalum oxide ( $Ta_2O_5$ ) layer grown by ALD on  $Si_3N_4$ . The back-gate bias dependence of the flicker noise on the graphene channel size with the source-drain distance varied from 10 to 200  $\mu$ m has been investigated systematically. The noise magnitude has been observed to be a factor of 10 times lower in comparison with that in recent reports. The normalized noise-power spectral density of  $\sim 2.2 \times 10^{-10}$  Hz<sup>-1</sup> at f = 10 Hz has been obtained. The noise mechanism can be explained by fluctuations of the carrier number, which are originated from the carrier trapping and de-trapping processes.

#### RESULTS AND DISCUSSION

To investigate the flicker noise, we fabricated GFETs on different substrates (Si/SiO<sub>2</sub> and Si/Si<sub>3</sub>N<sub>4</sub>) with and without an encapsulated high- $\kappa$  dielectric layer (Ta<sub>2</sub>O<sub>5</sub>). A highly *p*-doped Si wafer (1 – 10  $\Omega$ .cm) and a 300-nm SiO<sub>2</sub> (or 300-nm Si<sub>3</sub>N<sub>4</sub>) layer are employed as the back-gate and dielectric layer, respectively. Graphene transistors were prepared in following steps. First, photolithography, electron-beam deposition and lift-off processes were employed to form metal contacts of Cr (3 nm) and Au (100 nm) for source, drain and back-gate. Second, a single graphene sheet was transferred onto the SiO<sub>2</sub>/Si or Si<sub>3</sub>N<sub>4</sub>/Si substrate. A Ta<sub>2</sub>O<sub>5</sub> dielectric layer has been grown on top of graphene for some GFET devices in two steps, including growing a 2-nm Ta<sub>2</sub>O<sub>5</sub> seed layer by electron beam evaporation and an 18-nm Ta<sub>2</sub>O<sub>5</sub> film by ALD.<sup>22-23</sup> Photolithography and dry etching steps were employed to determine the active size of the devices. The distances between source and drain (length), *L*, are 10, 20, 30, 50, 75, 100, 150, 200  $\mu$ m, and the ratio between the width and length, *W/L*, of the active area is fixed at 2. The detail of the fabrication is provided in the Supplementary Information. A diagram of fabrication steps is illustrated in Figure S1. A surface image of a graphene sheet on Si<sub>3</sub>N<sub>4</sub>/Si using atomic force microscope (AFM) is provided in Figure S2.

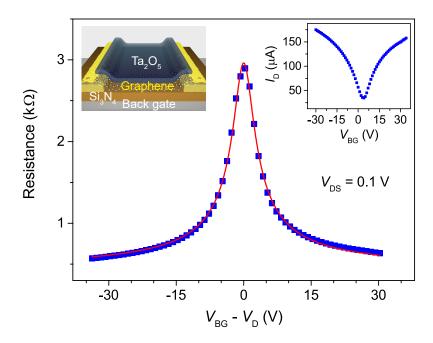

The current – voltage (I-V) behavior was characterized by two Keithley source-meters units. A Keithley 2400 was employed to vary the back-gate voltage,  $V_{\rm BG}$ , while a Keithley 2450 was used to set a constant voltage between drain and source contacts,  $V_{\rm DS}$ , and to measure the drain current,  $I_{\rm D}$ . Our electrical measurements were performed at room temperature. The I-V characteristics of a GFET covered by an ALD Ta<sub>2</sub>O<sub>5</sub> film on Si<sub>3</sub>N<sub>4</sub> ( $L=10~\mu m$ ,  $W=20~\mu m$ ) under  $V_{\rm DS}=0.1~{\rm V}$  is provided as an example in Figure 1, inset. Details of the setup and I-V characteristics at different  $V_{\rm DS}$  are illustrated in Figures S3 and S4.

To accurately determine the mobility,  $\mu$ , of carriers in graphene, the contact resistance,  $R_c$ , on a level with the graphene channel resistance,  $R_{ch}$ , is estimated from the total device resistance,  $R = V_{DS}/I_D$ . The mobility of carriers in the graphene device can be extracted by fitting the resistance – voltage (R-V) characteristic curve (Figure 1) in the following form.<sup>24-26</sup>

$$R = 2R_{\rm c} + R_{\rm ch} = 2R_{\rm c} + \frac{L}{Wq\mu\sqrt{n_0^2 + n_a^2}},$$

(1)

where q is the charge of electron,  $n_0$  is the carrier density resulting from charged impurities at the interface between dielectric layers and graphene or in the dielectric layers,  $n_g = \frac{c_G}{q}(V_{BG} - V_D)$  is the density of charged carriers generated by a voltage on the back-gate away from the charge neutrality point voltage,  $V_D$ , (the Dirac point),  $C_G = \frac{\varepsilon \varepsilon_0}{d}$  is the areal capacitance of the gate, with d being the thickness of the Si<sub>3</sub>N<sub>4</sub> dielectric material (d = 300 nm),  $\varepsilon_0$  is the vacuum permittivity, and  $\varepsilon \sim 6$  is the dielectric constant of

$\mathrm{Si_3N_4.^{27}}$  The capacitance of the 300-nm  $\mathrm{Si_3N_4}$  dielectric layer is ~17 nF/cm<sup>2</sup>. The red curve in Figure 1 presents the best fit to the R-V characteristic data using Eq. 1. We obtained the contact resistance at each electrode of ~209  $\Omega$ . The carrier density generated by charged impurities is ~2.4 × 10<sup>11</sup> cm<sup>-2</sup> at Dirac point. A high carrier mobility has been obtained in the GFET of ~5080 cm<sup>2</sup>/(V·s).

The level of the flicker noise is the key point for the performance of graphene devices. The 1/f noise was identified using a 100 kHz FFT spectrum analyzer (SR770) at room temperature. A current amplifier (FEMTO DLPCA-200) was employed to amplify the drain current. At a fixed back-gate voltage, the drain current was varied by adjusting drain-source voltage,  $V_{\rm DS}$ , from 20 mV to 0.5 V. The noise-power spectral density can be described as,

$$S_{\rm I} = \frac{Al_{\rm D}^2}{f^{\gamma}} \,, \tag{2}$$

where A is the amplitude of the noise and follows the empirical relation,  $A = \alpha_H/n$ , with  $\alpha_H$  being the Hooge's noise parameter to evaluate the magnitude of the flicker noise, <sup>4-5</sup> n is the total amount of carriers passing through the conducting area,  $\gamma \approx 1$  is an experimental value.<sup>5,7</sup>

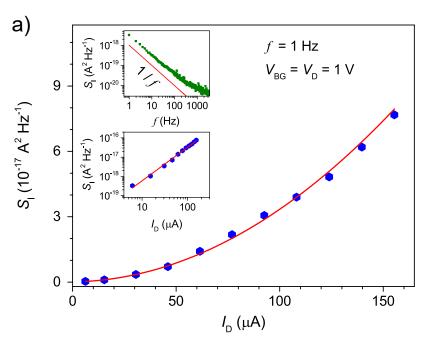

The noise-power spectral density of GFETs on  $Si_3N_4$  ( $L \times W = 10 \times 20 \ \mu\text{m}^2$ ) with the ALD  $Ta_2O_5$  encapsulated layer was investigated under different drain current from 6.18 to 156.8  $\mu$ A, and the voltage of the back-gate was fixed at Dirac point ( $V_{BG} = V_D = 1 \ V$ ). A typical noise-power spectral density under  $V_{DS} = 0.1 \ V$  is shown in Figure 2a (upper inset). This plot follows the 1/f dependence (namely,  $\gamma = 1$ ), and the noise-power spectral density,  $S_I$ , is  $\sim 10^{-18} \ A^2 \ Hz^{-1}$  at 1 Hz. The absence of bulges on the noise-power spectral density in this GFET device indicates that traps with a specific time constant are not dominated in the spectrum. Note that a few bulges have been reported in GFETs on  $Si/SiO_2$ . The bulges come from the generation-recombination (G-R) noise indicating fluctuation processes with well-defined frequencies.<sup>5</sup> When the drain current,  $I_D$ , was varied from 6.18 to 156.8  $\mu$ A, the noise-power spectral density increases with a square function from  $3.2 \times 10^{-19}$  to  $7.7 \times 10^{-17} \ A^2 \ Hz^{-1}$  at  $f = 1 \ Hz$  as plotted on a linear scale (Figure 2a) and a log-log plot (Figure 2a, lower inset). The noise-power spectral density proportional to  $I_D^2$  is also reported in previous reports for graphene devices on  $SiO_2$ .<sup>5,10</sup>

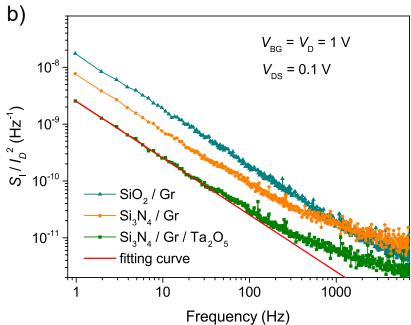

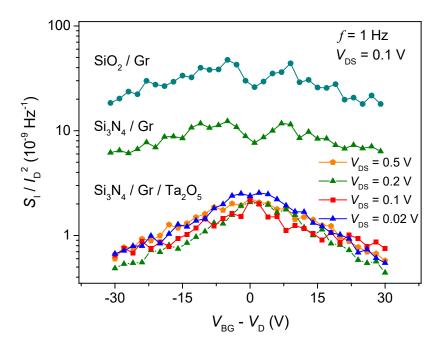

To evaluate the noise of GFETs on different insulator/dielectric layers, we determine the normalized noise-power spectral density, in which the noise is normalized with current,  $S_{\rm I}/I_{\rm D}^2$ , or the noise behavior independent of the drain current flowing through the device. The experiments performed under  $V_{\rm DS} = 0.1$  V and  $V_{\rm BG} = V_{\rm D} = 1$  V for graphene devices on SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and on Si<sub>3</sub>N<sub>4</sub> with the ALD Ta<sub>2</sub>O<sub>5</sub> encapsulated layer (Figure 2b). These devices were fabricated under the same conditions and graphene channel size of  $L = 10~\mu m$  and  $W = 20~\mu m$ . The noise level at f = 1 Hz of the graphene device on SiO<sub>2</sub> without the ALD Ta<sub>2</sub>O<sub>5</sub> layer is  $1.8 \times 10^{-8}$  Hz<sup>-1</sup>, which is similar to previous reports.<sup>10, 12</sup> The graphene on Si<sub>3</sub>N<sub>4</sub> device without the ALD Ta<sub>2</sub>O<sub>5</sub> layer shows a lower noise level of  $0.8 \times 10^{-8}$  Hz<sup>-1</sup>, which is about 2 times lower

than that of graphene on SiO<sub>2</sub> device. However, the graphene device covered with the high- $\kappa$  Ta<sub>2</sub>O<sub>5</sub> dielectric layer on Si<sub>3</sub>N<sub>4</sub> shows a noise level of  $2.5 \times 10^{-9}$  Hz<sup>-1</sup>. At f = 10 Hz, the normalized noise-power spectral density,  $S_1/I_D^2$ , of this device is equal to  $2.2 \times 10^{-10}$  Hz<sup>-1</sup>, indicating a reduction of the 1/f noise by 5 and 50 times as compared to that of graphene devices on h-BN and SiO<sub>2</sub>, respectively.<sup>10-12</sup>

The gate-bias characteristics of the noise-power spectral density normalized with current were further examined for the graphene device on Si<sub>3</sub>N<sub>4</sub> with the ALD Ta<sub>2</sub>O<sub>5</sub> layer under different back-gate voltage. The normalized noise-power spectral density,  $S_{\rm I}/I_{\rm D}^2$ , and together with the amplitude of the noise, A= $(1/M)\sum_{m=1}^{M} f_m S_{lm}/I_m^2$ , as function of gate voltage,  $(V_{BG} - V_D)$ , for graphene devices on SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and on  $Si_3N_4$  with the ALD  $Ta_2O_5$  encapsulated layer at f = 1 Hz are illustrated in Figures 3 and S5, respectively. Note that the noise amplitude is an average over several frequencies, thus, is the same as the noise-power spectral density normalized with current,  $S_{\rm I}/I_{\rm D}^2$ . As shown in Figure 3, M-shape behaviors of the noise-power spectral density normalized with current have been observed in devices with graphene on SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> with local minimum at  $V_{BG} = V_{D}$ . The observation of the noise behavior agrees with previous reports, 10, 12, 28 indicating that the noise at low-frequency in our devices on SiO<sub>2</sub> is typical for graphene. The characteristic is related to the presence of the spatial charge inhomogeneity as well as electron-hole puddles in graphene devices on SiO<sub>2</sub>.<sup>28</sup> In contrast, the behavior is not observed in graphene devices on Si<sub>3</sub>N<sub>4</sub> with the ALD Ta<sub>2</sub>O<sub>5</sub> layer. The noise-power spectral density normalized with current together with the amplitude of the noise are more than one order of magnitude lower in the graphene device on Si<sub>3</sub>N<sub>4</sub> with the ALD Ta<sub>2</sub>O<sub>5</sub> encapsulated layer compared to that on SiO<sub>2</sub>. A Λ-shape instead of an M-shape has been observed in the device (Figure 3). The noise level is lower when voltage applied to the back-gate is further away from Dirac point voltage. Graphene devices without a dielectric layer (Ta<sub>2</sub>O<sub>5</sub>) can absorb water vapor or organic contaminations under environmental exposures, which leads to a high noise level. 12, 29-30

We now address the origin and physical mechanism of the flicker noise behavior in our devices. From a relation between the drain current, mobility and the number of charge carriers  $(I_D \propto q\mu n)$  in Eq. 1, fluctuations in the drain current can be described as  $\delta I_D \propto qn\delta\mu + q\mu\delta n$ .<sup>5-6</sup> The flicker noise in FET devices typically originates from fluctuations in the carrier mobility or the number of charge carriers, or both.<sup>31</sup> In the context of the fluctuations in the carrier mobility described by Hooge model, the carrier mobility in graphene is typically affected by long-range Coulomb scatterings associated with charged impurities, and short-range disorder scatterings related to intrinsic defects, cracks, or boundaries of graphene.<sup>29-30</sup> Other scattering processes including ripples, phonons, mid-gap states generate fluctuations in the carrier mobility similar to that expected from the long- and short-range scatterings.<sup>1,32-36</sup> Thus, we will analyze the fluctuations in these two scattering sources separately. The carrier mobility limited by

the long-range Coulomb scattering does not exhibit gate-bias dependence, whereas the mobility associated with the other scattering depends on the gate-bias.<sup>1</sup> The behavior of the noise will be determined by which scattering mechanism contributes dominantly. In the viewpoint of fluctuations in the carrier number expected from the McWhorter's relation, the fluctuations are induced by the number of charge carriers passing through graphene layer due to the trapping/de-trapping processes near graphene-dielectric interfaces. The efficiency of these processes is defined by the density of empty as well filled states near the Fermi level.

Our observation of an M-shape behavior in graphene on SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>, devices (Figure 3) is consistent with previous reports of non-encapsulated GFET structures on SiO<sub>2</sub>.<sup>10, 29-30</sup> In these structures, molecules from the air (i.e., water-like contaminants) trapped on graphene are likely adding to the source of the charge-density inhomogeneity (or charge puddles) near Dirac point, which arises the long-range Coulomb scattering across the graphene channel.<sup>35-36</sup> Transforming from the M- to V-shape after annealing these devices was assigned to the suppression of the long-range scattering by removing absorbed molecules, thus, reducing the fluctuations in the carrier mobility.<sup>29</sup> On the other hand, the M-shape noise behavior can also originate from the high trap density in the device fabrication process.<sup>28</sup> These traps cause trapping/de-trapping processes of charged carriers near the graphene - SiO<sub>2</sub> interface that induces the fluctuations in number carrier.

The unexpected gate-bias behavior of the flicker noise in graphene on SiO<sub>2</sub> reported in several observations complies with the Hooge approach.<sup>37</sup> The measured noise can be interpreted by an empirical relation between the Hooge's noise parameter,  $\alpha_{\rm H}$ , the mobility,  $\mu$ , and a network of resistors.<sup>30</sup> While carrier mobility associated with the long-range Coulomb scattering is independent of the gate-voltage (i.e.,  $\mu_{\rm L} = 1/C_{\rm L}$ ), the carrier mobility related to the short-range scattering is inversely proportional to voltage applied on the back gate,  $\mu_{\rm S} = 1/(C_{\rm S}(V_{\rm BG} - V_{\rm D}))$ , where  $C_{\rm L}$  and  $C_{\rm S}$  are the long- and short-range scattering constants.<sup>38-39</sup> Following the dependence of the Hooge parameter (i.e.,  $\alpha_{\rm H} \approx (1/\mu)^{\delta}$ ) on the carrier mobility<sup>30</sup> and Matthiesen's rule (i.e.,  $1/\mu = 1/\mu_{\rm L} + 1/\mu_{\rm S}$ ), the dependence on the gate bias of normalized noise-power spectral density is expressed as,<sup>30</sup>

$$\frac{S_1}{I^2} = \frac{\alpha_H}{nf^{\gamma}} \approx \frac{\left(C_S(V_{BG} - V_D) + C_L\right)^{\delta}}{\left(V_{BG} - V_D\right)f^{\gamma}},\tag{3}$$

where the  $\delta \approx 3$  is experimentally determined for graphene on a substrate device.<sup>30, 40</sup> The 1/f noise is contributed by both the short- and long-range carrier scattering. The transport property of carriers near Dirac point in graphene channel is governed by spatial charge inhomogeneity which is related to the presence of electron-hole puddles in graphene, resulting in an increase in fluctuations.<sup>28</sup> The V-shape have been observed. For voltage applied on the back-gate away from Dirac point, fluctuations are

governed by long-range Coulomb scattering, thus, the 1/f noise decreases with increasing  $V_{\rm BG}$ .<sup>30</sup> The M-shape behavior has been observed in our graphene device on SiO<sub>2</sub>.

To improve the device performance as well as to reduce the flicker noise in our graphene devices, we have employed a high- $\kappa$  dielectric material, Si<sub>3</sub>N<sub>4</sub>, for the insulator gate, and encapsulated graphene with an ALD Ta<sub>2</sub>O<sub>5</sub> layer. As mentioned above, the normalized noise-power spectral density is more than one order of magnitude lower in the graphene device on Si<sub>3</sub>N<sub>4</sub> with the ALD top layer as compared to that on SiO<sub>2</sub>. The observed 1/f noise behavior in these devices presents the  $\Lambda$ -shape dependence (Figure 3). The short-range disorder scattering does not primarily attribute to the flicker noise of our devices. Therefore, the carrier-mobility fluctuations in the short- and long-range scatterings associated with the Hooge model do not contribute dominantly to the flicker noise, whereas the fluctuations in the carrier number associated with the McWhorter approach have a major role in the flicker noise of these devices.

The decrease of impurities in graphene devices on  $Si_3N_4$  with an ALD  $Ta_2O_5$  encapsulated layer is expected from our fabrication process. Although our devices are not annealed to remove atmospheric contaminants, the 1/f noise reduction and  $\Lambda$ -shape behavior have been obtained. Typically, metal contacts were implemented by depositing metals on top of graphene on a substrate. This method caused the contamination of photoresist residues on graphene during the photolithography process. In contrast, our fabrication process starts with a well-prepared structure of  $Si/Si_3N_4$ /metal-contacts, and a single graphene sheet is transferred onto this structure. Graphene surface is not covered by polymer at any stage of the fabrication, reducing the number of traps at interfaces of graphene/metal contacts and graphene/ $Si_3N_4$ . The reduction of photoresist residuals on graphene surface before growing the ALD  $Ta_2O_5$  layer was confirmed by AFM image (Supplementary information, Figure S2).

In order to reduce the fluctuations in the carrier mobility, the high- $\kappa$  ALD Ta<sub>2</sub>O<sub>5</sub> dielectric layer has been deposited on the top of our graphene devices to suppress the long-range Coulomb scattering as well as protect the graphene surface. Although a degradation of the carrier mobility in graphene could happen when the dielectric layer was grown on top of graphene, this dielectric layer with high quality could protect graphene from exposure conditions to prevent the increase of 1/f noise. <sup>14</sup> The dielectric screening effect of the high- $\kappa$  Ta<sub>2</sub>O<sub>5</sub> dielectric material can minimize the long-range Coulomb scattering efficiently. <sup>41</sup> On the other hand, to achieve a uniform deposition of the ALD layer on graphene, a 2-nm Ta<sub>2</sub>O<sub>5</sub> seed layer was deposited by electron beam evaporation. The samples were loaded into a vacuum chamber (3 × 10<sup>-6</sup> Torr), which significant reduced contaminants on the surface of graphene before growing the 2-nm Ta<sub>2</sub>O<sub>5</sub> seed layer. During the evaporation step, the 2-nm Ta<sub>2</sub>O<sub>5</sub> layer contains oxygen vacancies, acting as carrier traps at the interface between graphene and the seed layer. The oxygen vacancy-related traps can generate fluctuations in the carrier number through random trapping/detrapping processes of carriers. Thanks to H<sub>2</sub>O pulses during the first few cycles of the ALD process at

300 °C, the 2-nm  ${\rm TaO_x}$  seed layer is fully oxidized, resulting in a low number of carrier traps in the seed layer. Consequently, the suppression of the long-range scattering as well as fewer effective trap states at the interfaces between graphene and oxide resulted in the reducing of the noise and produced the  $\Lambda$ -shape gate-bias behavior. Note that by varying the voltage applied on the gate, we can control the carrier number in the active area. As mentioned before, the normalized noise-power spectral density does not follow the simple  $1/(V_{\rm BG} - V_{\rm D})$  dependence as expected from the Hooge approach (Figure 3). The  $\Lambda$ -shape gate-bias behavior suggests that another physical mechanism for the flicker noise of the drain current dominates in our GFETs.

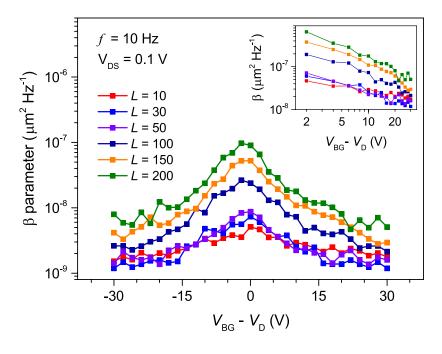

To shed light on the mechanism of the flicker noise, we further investigated noise characteristics with different device area. The active area,  $L \times W$ , is varied in a wide range from 200 to 80000  $\mu$ m<sup>2</sup>, where the lengths, L, are 10, 20, 30, 50, 75, 100, 150, 200  $\mu$ m, and the ratio of W/L is fixed at 2. The voltage between source and drain,  $V_{DS}$ , was fixed at 0.1 V. For the device with  $L \times W = 200 \times 400 \,\mu\text{m}^2$ , at Dirac point ( $V_{BG}$ =  $V_D$ ) and f = 10 Hz, a maximum value of  $\sim 1 \times 10^{-12}$  Hz<sup>-1</sup> has been observed for the normalized noisepower spectral density (Figure S6). The value is several orders of magnitude lower than that in devices on SiO<sub>2</sub> reported in the literature. <sup>10-12</sup> To compare the flicker noise behavior in the graphene devices with different active area, we employ the area-normalized noise-power spectral density,  $\beta = (S_I/I_D^2)(L \times W)$ . <sup>10-11</sup> Figure 4 shows plots of  $\beta$  parameter at f = 10 Hz, ranging between  $1 \times 10^{-9}$  to  $5 \times 10^{-9}$  µm<sup>2</sup> Hz<sup>-1</sup> for the length, L, of  $< 50 \mu m$ . In the micrometer scale, the flicker noise in these devices was reduced by a factor of 5 as compared to that in graphene devices encapsulated by two h-BN layers, 11 a HfO<sub>2</sub> dielectric gate<sup>14</sup>, or on h-BN<sup>10</sup> with  $\beta$  reported from  $5 \times 10^{-9}$  to  $10^{-7}$  µm<sup>2</sup> Hz<sup>-1</sup> at f = 10 Hz. The value is the same order with multiple graphene layers on a substrate. 42 However, the mobility of carrier decreases with adding graphene layers, 42-43 thus, reducing the performance of the devices. Note that under identical conditions including gate-bias and temperature, the carrier number is proportional to the active area. 12 As illustrated in Figure 4, the area-normalized noise-power spectral density does not scale inversely proportional to the device area (namely, the simple 1/n dependence or the graphene sheet resistant).<sup>44</sup> This suggests that the reduction of the noise and the  $\Lambda$ -shape behavior of the devices covered with the ALD Ta<sub>2</sub>O<sub>5</sub> dielectric layer cannot be explained with the Hooge's model.

To provide insight into the  $\Lambda$ -shape behavior, we employed the framework of the McWhorter approach based on the fluctuations in the carrier number of single-layer graphene in field-effect transistors. The amount of charged carriers in the active area can be varied by sweeping the back-gate voltage further away from Dirac point, and this value is proportional to the gate voltage,  $V_{\rm BG}$  (see Eq. 1).<sup>24</sup> In the McWhorter model, normalized noise-power spectral density,  $S_{\rm I}/I_{\rm D}^2$ , reduces with the  $1/n^2$  dependence, thus, the  $\beta$  parameter is proportion to 1/n or  $1/V_{\rm BG}$ .<sup>12</sup> The carrier tunneling to/from the

graphene channel through the trapping/de-trapping processes gives rise to the fluctuations in the carrier number in the graphene channel, which mainly contributes to the 1/f noise. The inset of Figure 4 shows the  $\beta$  parameter is scaled down with the back-gate bias,  $V_{\rm BG}$ . The noise characteristic in our devices can be explained by the McWhorter model, in which the fluctuations in the carrier number are the dominant source for the flicker noise.

Following the McWhorter approach, we can estimate the effective trap density,  $D_{\rm eff}$ , at Fermi level from normalized noise-power spectral density:<sup>45</sup>

$$\frac{S_{\rm I}}{l^2} = \frac{k_{\rm B}TD_{\rm eff}}{fLWn_c^2\ln(\tau_{\rm max}/\tau_{\rm min})},\tag{4}$$

where T is the temperature,  $\tau_{\rm min}$  and  $\tau_{\rm max}$  are the minimum and maximum time for carrier tunneling, respectively, and  $k_{\rm B}$  is Boltzmann's constant. The carrier concentration in the active area can be estimated from the charged carrier density,  $n_c = \sqrt{{n_0}^2 + {n_g}^2}$ . The approach has been used to analyze the low-frequency noise in metal-oxide-semiconductor field-effect transistors based on Si or GaAs.<sup>45</sup> To estimate  $D_{\rm eff}$ , we fit the experimental results to the McWhorter model (Eq. 4) with  $\ln(\tau_{\rm max}/\tau_{\rm min}) = 4$ ,<sup>15, 45</sup> (the red line in Figure 2b). Under  $V_{\rm DS} = 0.1$  V, the effective trap density,  $D_{\rm eff}$ , is ~1.14 × 10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup> at Dirac point (i.e.,  $V_{\rm BG} = V_{\rm D}$ ), which is a factor of 10 times lower than that of GFETs on the SiO<sub>2</sub>/Si substrate.<sup>32-33, 46</sup>

## **CONCLUSIONS**

In summary, we have carried out measurements of the low-frequency 1/f noise on graphene field-effect transistors covered by the high-k dielectric  $Ta_2O_5$  layer (a few nanometers thick) on  $Si_3N_4$ . A low noise level of  $\sim 2.2 \times 10^{-10}$  Hz<sup>-1</sup> has been obtained at f = 10 Hz. The dependence on the channel graphene area of the noise was also investigated systematically. The origin and physical mechanism of the noise can be interpreted by the McWhorter model, in which the tunneling of carriers from/to the graphene channel via the trapping/de-trapping processes in dielectric layers processes is the determining factor. The considerable suppression of flicker noise can offer guidance on practical implications.

# ASSOCIATED CONTENT

**Supporting Information**: The Supporting Information is available free of charge on the ACS Publications website at xxx. Details for GFET fabrication, atomic force microscopy images, electrical setup, I-V transfer characteristics, noise amplitude, normalized noise-power spectral density.

# **AUTHOR INFORMATION**

# **Corresponding Author**

\*E-mail: vinh@vt.edu

# **ORCID**

V. X. Ho: 0000-0001-5413-9030 N. Q. Vinh: 0000-0002-3071-1722

## **Author Contributions**

<sup>†</sup>Y. Wang and V. X. Ho contributed equally to this work.

# **Notes**

The authors declare no competing financial interest.

## **ACKNOWLEDGMENTS**

The authors gratefully acknowledge the financial support of this effort by the Earth Science Technology Office (ESTO), NASA.

# Figure captions

Figure 1: Resistance – voltage transfer characteristics of a graphene device covered by an ALD Ta<sub>2</sub>O<sub>5</sub> film on Si<sub>3</sub>N<sub>4</sub> ( $L = 10 \mu m$ ,  $W = 20 \mu m$ ) at room temperature under  $V_{DS} = 0.1 \text{ V}$ . The left inset provides a schematic of our graphene device, and the right inset shows the original current – voltage transfer curve.

Figure 2: The flicker noise in GFETs ( $L = 10 \, \mu m$ ,  $W = 20 \, \mu m$ ) at Dirac point voltage (mainly,  $V_{\rm BG} = V_{\rm D} = 1$ ) and under  $V_{\rm DS} = 0.1 \, \rm V$ . (a) The noise-power spectral density at  $f = 1 \, \rm Hz$  increases with a square function of the drain current. Upper inset provides the noise-power spectral density, while lower inset presents the noise-power spectral density at  $f = 1 \, \rm Hz$ . (b) The noise-power spectral density is normalized with current in graphene on SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and on Si<sub>3</sub>N<sub>4</sub> with the ALD Ta<sub>2</sub>O<sub>5</sub> encapsulated layer.

**Figure 3:** Normalized noise-power spectral density as function of back-gate voltage ( $V_{BG}$  -  $V_D$ ) for graphene on SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and Si<sub>3</sub>N<sub>4</sub> with the ALD Ta<sub>2</sub>O<sub>5</sub> encapsulated layer at f = 1 Hz.

**Figure 4:** Area-normalized noise-power spectral density,  $\beta = (S_I/I_D^2)(L \times W)$ , at f = 10 Hz plots again the back-gate voltage  $(V_{BG} - V_D)$  for graphene devices on  $Si_3N_4$  with the ALD  $Ta_2O_5$  encapsulated layer. Inset shows the data on the log-log scale.

## REFERENCES

- 1. Das Sarma, S.; Adam, S.; Hwang, E. H.; Rossi, E., Electronic transport in two-dimensional graphene. *Rev Mod Phys* **2011**, *83*, 407-470.

- 2. Liao, L.; Lin, Y. C.; Bao, M. Q.; Cheng, R.; Bai, J. W.; Liu, Y. A.; Qu, Y. Q.; Wang, K. L.; Huang, Y.; Duan, X. F., High-speed graphene transistors with a self-aligned nanowire gate. *Nature* **2010**, *467* (7313), 305-308.

- 3. Koppens, F. H. L.; Mueller, T.; Avouris, P.; Ferrari, A. C.; Vitiello, M. S.; Polini, M., Photodetectors based on graphene, other two-dimensional materials and hybrid systems. *Nat Nanotechnol* **2014**, *9*, 780-793.

- 4. Vandamme, L. K. J., Model for 1-F Noise in Mos-Transistors Biased in the Linear Region. *Solid State Electron* **1980**, *23*, 317-323.

- 5. Balandin, A. A., Low-frequency 1/f noise in graphene devices. *Nat Nanotechnol* **2013**, *8*, 549-555.

- 6. Hung, K. K.; Ko, P. K.; Hu, C. M.; Cheng, Y. C., A Unified Model for the Flicker Noise in Metal Oxide-Semiconductor Field-Effect Transistors. *IEEE T Electron Dev* **1990**, *37*, 654-665.

- 7. Dutta, P.; Horn, P. M., Low-Frequency Fluctuations in Solids 1-F Noise. *Rev Mod Phys* **1981**, *53*, 497-516.

- 8. Liu, G. X.; Rumyantsev, S.; Shur, M. S.; Balandin, A. A., Origin of 1/f noise in graphene multilayers: Surface vs. volume. *Appl Phys Lett* **2013**, *102*, 093111.

- 9. Liu, G. X.; Rumyantsev, S.; Shur, M.; Balandin, A. A., Graphene thickness-graded transistors with reduced electronic noise. *Appl Phys Lett* **2012**, *100*, 033103.

- 10. Kayyalha, M.; Chen, Y. P., Observation of reduced 1/f noise in graphene field effect transistors on boron nitride substrates. *Appl Phys Lett* **2015**, *107*, 113101.

- 11. Stolyarov, M. A.; Liu, G. X.; Rumyantsev, S. L.; Shur, M.; Balandin, A. A., Suppression of 1/f noise in near-ballistic h-BN-graphene-h-BN heterostructure field-effect transistors. *Appl Phys Lett* **2015**, *107*, 023106.

- 12. Rumyantsev, S.; Liu, G.; Stillman, W.; Shur, M.; Balandin, A. A., Electrical and noise characteristics of graphene field-effect transistors: ambient effects, noise sources and physical mechanisms. *J Phys-Condens Mat* **2010**, *22*, 395302.

- 13. Wu, T.; Alharbi, A.; Taniguchi, T.; Watanabe, K.; Shahrjerdi, D., Low-frequency noise in irradiated graphene FETs. *Appl Phys Lett* **2018**, *113*, 193502.

- 14. Liu, G.; Stillman, W.; Rumyantsev, S.; Shao, Q.; Shur, M.; Balandin, A. A., Low-frequency electronic noise in the double-gate single-layer graphene transistors. *Appl Phys Lett* **2009**, *95*, 033103.

- 15. Peng, S. G.; Jin, Z.; Zhang, D. Y.; Shi, J. Y.; Mao, D. C.; Wang, S. Q.; Yu, G. H., Carrier-Number-Fluctuation Induced Ultralow 1/f Noise Level in Top-Gated Graphene Field Effect Transistor. *ACS Appl Mater Inter* **2017**, *9*, 6661-6665.

- 16. Marschall, R.; Wang, L. Z., Non-metal doping of transition metal oxides for visible-light photocatalysis. *Catal Today* **2014**, *225*, 111-135.

- 17. Gritsenko, V. A.; Perevalov, T. V.; Voronkovskii, V. A.; Gismatulin, A. A.; Kruchinin, V. N.; Aliev, V. S.; Pustovarov, V. A.; Prosvirin, I. P.; Roizin, Y., Charge Transport and the Nature of Traps in Oxygen Deficient Tantalum Oxide. *ACS Appl Mater Inter* **2018**, *10*, 3769-3775.

- 18. Gu, T. K.; Tada, T.; Watanabe, S., Conductive Path Formation in the Ta<sub>2</sub>O<sub>5</sub> Atomic Switch: First-Principles Analyses. *ACS Nano* **2010**, *4*, 6477-6482.

- 19. Alimardani, N.; King, S.; French, B. L.; Tan, C.; Lampert, B. P.; Conley, J. F., Investigation of the impact of insulator material on the performance of dissimilar electrode metal-insulator-metal diodes. *J Appl Phys* **2014**, *116*, 024508.

- 20. Kozawaguchi, H.; Tsujiyama, B.; Murase, K., Thin-Film Electroluminescent Device Employing Ta<sub>2</sub>O<sub>5</sub> Rf Sputtered Insulating Film. *Jpn J Appl Phys 1* **1982**, *21*, 1028-1031.

- 21. Freeman, Y., *Tantalum and Niobium-Based Capacitors: Science, Technology, and Applications.* Springer; 1st Ed.: 2018.

- 22. Wang, Y.; Ho, V. X.; Henschel, Z. N.; Pradhan, P.; Howe, L.; Cooney, M. P.; Vinh, N. Q., Graphene Photodetector Based on Interfacial Photogating Effect with High Sensitivity. *Proceedings of SPIE* **2020**, *11503*, 1150306.

- 23. Wang, Y.; Ho, V. X.; Pradhan, P.; Cooney, M. P.; Vinh, N. Q., Graphene-Germanium Quantum Dot Photodetector with High Sensitivity *Proceedings of SPIE* **2019**, *11088*, 1108809.

- 24. Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K., Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric. *Appl Phys Lett* **2009**, *94*, 062107.

- 25. Chen, K.; Wan, X.; Liu, D. Q.; Kang, Z. W.; Xie, W. G.; Chen, J.; Miao, Q.; Xu, J. B., Quantitative determination of scattering mechanism in large-area graphene on conventional and SAM-functionalized substrates at room temperature. *Nanoscale* **2013**, *5*, 5784-5793.

- 26. Wang, N.; Ma, Z. H.; Ding, C.; Jia, H. Z.; Sui, G. R.; Gao, X. M., Characteristics of Dual-Gate Graphene Thermoelectric Devices Based on Voltage Regulation. *Energy Technol-Ger* **2020**, *8*, 1901466.

- 27. Stoffel, A.; Kovacs, A.; Kronast, W.; Muller, B., LPCVD against PECVD for micromechanical applications. *J Micromech Microeng* **1996**, *6*, 1-13.

- 28. Xu, G. Y.; Torres, C. M.; Zhang, Y. G.; Liu, F.; Song, E. B.; Wang, M. S.; Zhou, Y.; Zeng, C. F.; Wang, K. L., Effect of Spatial Charge Inhomogeneity on 1/f Noise Behavior in Graphene. *Nano Lett* **2010**, *10*, 3312-3317.

- 29. Kaverzin, A. A.; Mayorov, A. S.; Shytov, A.; Horsell, D. W., Impurities as a source of 1/f noise in graphene. *Phys Rev B* **2012**, *85*, 075435.

- 30. Zhang, Y.; Mendez, E. E.; Du, X., Mobility-Dependent Low-Frequency Noise in Graphene Field-Effect Transistors. *ACS Nano* **2011**, *5*, 8124-8130.

- 31. Scholten, A. J.; Tiemeijer, L. F.; van Langevelde, R.; Havens, R. J.; Zegers-van Duijnhoven, A. T. A.; Venezia, V. C., Noise modeling for RF CMOS circuit simulation. *Ieee T Electron Dev* **2003**, *50*, 618-632.

- 32. Tan, Y. W.; Zhang, Y.; Bolotin, K.; Zhao, Y.; Adam, S.; Hwang, E. H.; Das Sarma, S.; Stormer, H. L.; Kim, P., Measurement of scattering rate and minimum conductivity in graphene. *Phys Rev Lett* **2007**, *99*, 246803.

- 33. Wang, H. M.; Wu, Y. H.; Cong, C. X.; Shang, J. Z.; Yu, T., Hysteresis of Electronic Transport in Graphene Transistors. *ACS Nano* **2010**, *4*, 7221-7228.

- 34. Katsnelson, M. I.; Geim, A. K., Electron scattering on microscopic corrugations in graphene. *Philos T R Soc A* **2008**, *366*, 195-204.

- 35. Zhang, Y. B.; Brar, V. W.; Girit, C.; Zettl, A.; Crommie, M. F., Origin of spatial charge inhomogeneity in graphene. *Nat Phys* **2009**, *5*, 722-726.

- 36. Cho, S.; Fuhrer, M. S., Charge transport and inhomogeneity near the minimum conductivity point in graphene. *Phys Rev B* **2008**, *77*, 081402.

- 37. Strasser, C.; Ludbrook, B. M.; Levy, G.; Macdonald, A. J.; Burke, S. A.; Wehling, T. O.; Kern, K.; Damascelli, A.; Ast, C. R., Long- versus Short-Range Scattering in Doped Epitaxial Graphene. *Nano Lett* **2015**, *15*, 2825-2829.

- 38. Adam, S.; Hwang, E. H.; Galitski, V. M.; Das Sarma, S., A self-consistent theory for graphene transport. *P Natl Acad Sci USA* **2007**, *104*, 18392-18397.

- 39. Nomura, K.; MacDonald, A. H., Quantum Hall ferromagnetism in graphene. *Phys Rev Lett* **2006**, *96* (25), 256602.

- 40. Lin, Y. M.; Avouris, P., Strong suppression of electrical noise in bilayer graphene nanodevices. *Nano Lett* **2008**, *8*, 2119-2125.

- 41. Chen, F.; Xia, J. L.; Ferry, D. K.; Tao, N. J., Dielectric Screening Enhanced Performance in Graphene FET. *Nano Lett* **2009**, *9*, 2571-2574.

- 42. Rumyantsev, S. L.; Jiang, C. L.; Samnakay, R.; Shur, M. S.; Balandin, A. A., 1/ f Noise Characteristics of MoS2 Thin-Film Transistors: Comparison of Single and Multilayer Structures. *IEEE Electr Device L* **2015**, *36*, 517-519.

- 43. Nagashio, K.; Nishimura, T.; Kita, K.; Toriumi, A., Mobility Variations in Mono- and Multi-Layer Graphene Films. *Appl Phys Express* **2009**, *2*, 025003.

- 44. Hossain, M. Z.; Rumyantsev, S.; Shur, M. S.; Balandin, A. A., Reduction of 1/f noise in graphene after electron-beam irradiation. *Appl Phys Lett* **2013**, *102*, 153512.

- 45. Levinshtein, M. E.; Rumyantsev, S. L.; Tauk, R.; Boubanga, S.; Dyakonova, N.; Knap, W.; Shchepetov, A.; Bollaert, S.; Rollens, Y.; Shur, M. S., Low frequency noise in InAlAs/InGaAs modulation doped field effect transistors with 50-nm gate length. *J Appl Phys* **2007**, *102*, 064506.

- 46. Yan, J.; Zhang, Y. B.; Kim, P.; Pinczuk, A., Electric field effect tuning of electron-phonon coupling in graphene. *Phys Rev Lett* **2007**, *98*, 166802.

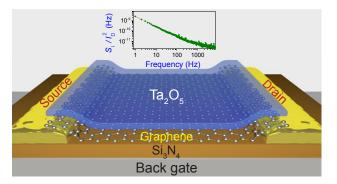

# **Table of Contents graphic:**

Schematic of graphene devices including back-gate, graphene, dielectric layers (Si<sub>3</sub>N<sub>4</sub>, Ta<sub>2</sub>O<sub>5</sub>), and 1/f noise.

Figure 1

Figure 2

Figure 3

Figure 4