# **Final Technical Report**

# **NASA WIRELESS SMART PLUG**

**Experimental Control Logic Laboratory (XCLL)**

| Au | th | ors: |

|----|----|------|

|----|----|------|

Akeem Whitehead Project Manager

Derek Garsee Software Engineer

Jeffrey Jordan Hardware Engineer

Christian Carmichael System Integrations Engineer

# **Faculty Advisor:**

Dr. Jay Porter

Electronic Systems Engineering Technology, Texas A&M University

# **Sponsor:**

Dr. Scott A. Howe

National Aeronautics and Space Administration

**Due:** May 7, 2013

**Delivered:** May 7, 2013 **Responsibility:** Group **Contact Information:**

| Reviewed by: |  |  |

|--------------|--|--|

|              |  |  |

| Signaturo    |  |  |

Dear Dr. Joseph A. Morgan, D.E., P.E.,

Experimental Control Logic Laboratory (XCLL) is pleased to present the Final Technical Report for the NASA Wireless Smart Plug (NWSP). The NWSP project is sponsored by NASA through the 2013 eXploration Habitat (X-Hab) Academic Innovation Challenge. XCLL is a Capstone based team, consisting of four undergraduate seniors from the Electronics Engineering Technology program.

XCLL's faculty Technical Advisor is Dr. Jay Porter, and the team members are:

- Akeem Whitehead Project Manager

- Derek Garsee Software Engineer

- Jeffrey Jordan Hardware Engineer

- Christian Carmichael Systems Integration Engineer

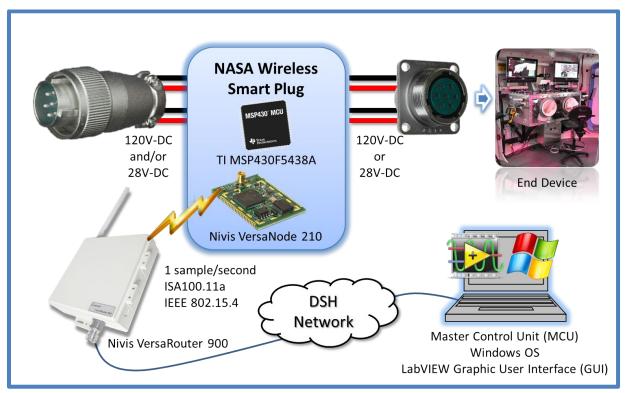

The NWSP is a current monitoring and control device that enables users to identify and respond to situations when an end-device being used on NASA's mock-up Deep Space Habitat (DSH) is exceeding optimal current draw. Given the DSH will require strict consideration of power consumption, the ability to manually load shed between end-devices of various priorities will provide users with the ability to continue operating end-devices that are critical to the mission objective. By equipping the NWSP with a disconnect feature, load shedding is made possible remotely from the user's computer station running a LabVIEW based executable. NASA requires the NWSP to monitor and control current between 0 to 5 amperes on either or both a 28V-DC and 120V-DC load line, at increments of 100 milliamperes, and to update the LabVIEW executable in 1 second intervals. The user will be prompted when an end-device's current exceeds a threshold, and the option to manually disconnect from the DSH will reside with the user. Five NWPS units are to be delivered to NASA and work in parallel, thus the LabVIEW executable will be able to monitor and control multiple devices simultaneously.

The NWSP was scheduled to begin on January, 17, 2013. XCLL is to deliver five fully functioning NWSPs to NASA by May 20, 2013. After delivery, the project will be transferred to the Texas A&M University Mobile Integrated Solutions Lab (MISL) for final testing and delivery on-site at NASA Johnson Space Center (JSC). XCLL has completed the production of five NWSPs for NASA's DSH as described in this proposal on time, over budget, and with requisite quality. All ownership of intellectual property in the development of the NWSP will belong to NASA.

Regards,

Akeem P. Whitehead Project Manager, XCLL

# **Table of Contents**

# Contents

| List of Figures                                 | 7  |

|-------------------------------------------------|----|

| List of Tables                                  | 9  |

| 1.0 Introduction                                | 10 |

| 1.1 General                                     | 10 |

| 1.2 Background                                  | 10 |

| 1.3 Justification                               | 10 |

| 2.0 Problem Statement & Scope                   | 11 |

| 2.1 Functional Requirements                     | 11 |

| 2.1.1 Power Control                             | 11 |

| 2.1.2 Communications                            | 11 |

| 2.1.3 Form Factor & Fit                         | 12 |

| 3.0 Design Implementation Strategy and Overview | 13 |

| 3.1 Hardware                                    | 13 |

| 3.1.1 Microcontroller                           | 13 |

| 3.1.2 Nivis VersaNode 210                       | 13 |

| 3.2 Software                                    | 14 |

| 3.3 Integration                                 | 14 |

| 4.0 System Requirements                         | 15 |

| 4.1 Hardware                                    | 15 |

| 4.2 Software                                    | 16 |

| 4.2.1 Embedded Intelligence Software            | 16 |

| 4.2.2 Graphic User Interface Software           | 16 |

| 4.3 Enclosure                                   | 16 |

| 4.4 Performance Specifications                  | 16 |

| 5.0 System Analysis                             | 18 |

| 5.1 Current Sense Conversion                    | 18 |

|     | 5.1.1 Signal Conditioning                                                   | 18 |

|-----|-----------------------------------------------------------------------------|----|

|     | 5.1.2 Analog to Digital Conversion                                          | 19 |

| į   | 5.2 ISA-100.11a Wireless Standard                                           | 20 |

| į   | 5.3 Serial Peripheral Interface                                             | 21 |

| 6.0 | Hardware Design                                                             | 22 |

| (   | 5.1 Functional Block Diagram                                                | 22 |

|     | 6.1.1 Microcontroller Interfaced with Radio Design                          | 23 |

|     | 6.1.2 Voltage Regulation and Ground Isolation for Internal Circuitry Design | 23 |

|     | 6.1.3 Current Sense and Conversion Design                                   | 25 |

|     | 6.1.4 Relay Control Design                                                  | 25 |

|     | 6.1.5 Voltage Measurement Design                                            | 26 |

|     | 6.1.6 Light Emitting Diode Indicator Design                                 | 27 |

| (   | 5.2 Schematic                                                               | 27 |

|     | 6.2.1 Microcontroller Schematic                                             | 28 |

|     | 6.2.2 Radio Module Schematic                                                | 29 |

|     | 6.2.3 Power Schematic                                                       | 30 |

|     | 6.2.4 Current Sensing Conversion and Calibration Schematic                  | 31 |

|     | 6.2.5 Voltage Detection Schematic                                           | 32 |

|     | 6.2.6 LED Indicators Schematic                                              | 33 |

|     | 6.2.7 Relay Control Schematic                                               | 33 |

|     | 6.2.8 Connector and Ground Isolation Schematic                              | 34 |

| (   | 5.3 PCB Layout                                                              | 35 |

|     | 6.3.1 Copper Top                                                            | 36 |

|     | 6.3.2 Copper Inner Layer 1                                                  | 37 |

|     | 6.3.3 Copper Inner Layer 2                                                  | 38 |

|     | 6.3.3 Copper Bottom Layer                                                   | 39 |

| 7.0 | Software Design                                                             | 43 |

| -   | 7.1 Implementation Strategy                                                 | 43 |

| 7.2 Hierarchy Chart                          | 43 |

|----------------------------------------------|----|

| 7.2.1 Current_Init                           | 44 |

| 7.2.2 Current_Measure                        | 44 |

| 7.2.3 ADC_Convert                            | 44 |

| 7.2.4 Parse_Message                          | 44 |

| 7.2.5 Toggle_Relay                           | 44 |

| 7.3 Flow Diagrams                            | 44 |

| 7.3.1 High Level Diagram                     | 45 |

| 7.3.2 Main Loop Diagram                      | 45 |

| 7.3.3 Application Flow Diagram               | 46 |

| 7.3.4 Message Parse Flow Diagram             | 47 |

| 7.4 Code Description                         | 48 |

| 7.4.1 Current Measurement                    | 48 |

| 7.4.2 ADC Conversion                         | 49 |

| 7.5 Graphic User Interface                   | 49 |

| 7.5.1 Receive Data                           | 49 |

| 7.5.2 Transmit Data                          | 51 |

| 7.5.3 Features                               | 52 |

| 7.6 Wireless Communication                   | 52 |

| 8.0 Testing                                  | 53 |

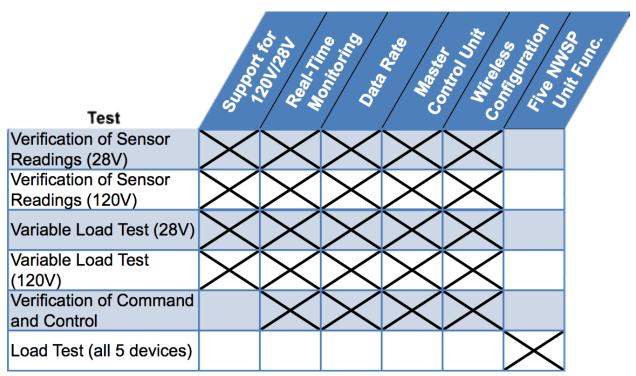

| 8.1 Test Matrix                              | 53 |

| 8.2 Test Plan                                | 53 |

| 8.2.1 Verification of Sensor Readings (28V)  | 53 |

| 8.2.2 Verification of Sensor Readings (120V) | 54 |

| 8.2.3 Variable Load Test (28V)               | 54 |

| 8.2.4 Variable Load Test (120V)              | 55 |

| 8.2.5 Verification of Command and Control    | 56 |

| 8.2.6 Five Device Load Test                  | 56 |

| 9.0 Problems & Solutions                                   | 58  |

|------------------------------------------------------------|-----|

| 9.1 Technical                                              | 58  |

| 9.1.1 Current Sensor Conversion Error                      | 58  |

| 9.1.2 Wireless Communication Overhead                      | 60  |

| 10.0 Conclusions                                           | 61  |

| Appendices                                                 | 62  |

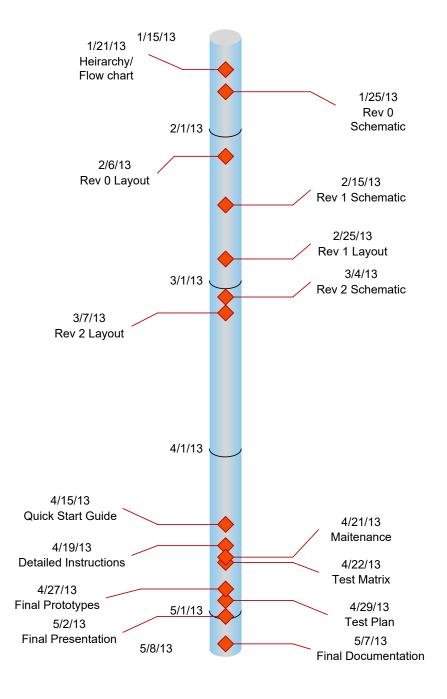

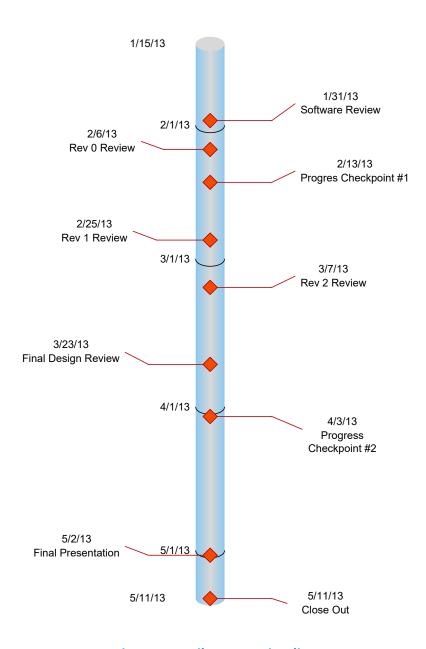

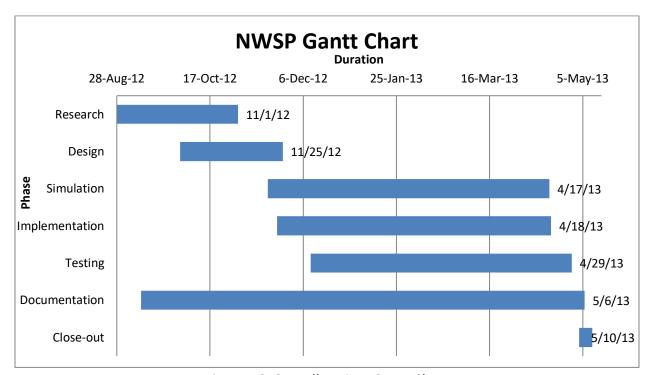

| Appendix A: System Design Process                          | 62  |

| Appendix B: Parts Lists with Unit and 100 Quantity Pricing | 95  |

| Appendix C: Complete Alpha Schematics                      | 98  |

| Appendix D: Complete Bravo Schematics                      | 105 |

| Appendix E: Alpha PCB Layout                               | 110 |

| Appendix F: Bravo PCB Layout                               | 116 |

| Appendix G: Code Listing                                   | 122 |

| Appendix H: Mechanical Drawings                            | 123 |

| Appendix I: Flow Charts                                    | 127 |

| Appendix J: NWSP to DSH and End-Device Connection Diagram  | 130 |

| Appendix K: Resumes                                        | 132 |

# **List of Figures**

| Figure 1: Conceptual Block Diagram                              | 15 |

|-----------------------------------------------------------------|----|

| Figure 2: Current Sensor Characterization Graphed               | 18 |

| Figure 3: Differential Amplifier Configuration                  | 19 |

| Figure 4: ISA-100.11a Reference Model                           | 20 |

| Figure 5: Single Protocol Data Unit                             | 21 |

| Figure 6: Full Protocol Data Unit                               | 21 |

| Figure 7: Functional Block Diagram Overview                     | 22 |

| Figure 8: Microcontroller Interfaced with Radio Block Diagram   | 23 |

| Figure 9: Voltage Regulation and Ground Isolation Block Diagram | 24 |

| Figure 10: Current Sense and Conversion Block Diagram           | 25 |

| Figure 11: Relay Control Block Diagram                          | 26 |

| Figure 12: Voltage Measurement Block Diagram                    | 26 |

| Figure 13: Light Emitting Diode Indicator Block Diagram         | 27 |

| Figure 14: Microcontroller Schematic                            | 29 |

| Figure 15: Radio Module Schematic                               | 30 |

| Figure 16: Power Schematic                                      | 31 |

| Figure 17: Current Sensing Conversion and Calibration Schematic | 32 |

| Figure 18: Voltage Detection Schematic                          | 32 |

| Figure 19: LED Indicators Schematic                             |    |

| Figure 20: Relay Control Schematic                              | 34 |

| Figure 21: Connector and Ground Isolation Schematic             | 34 |

| Figure 22: PCB Copper Top                                       | 36 |

| Figure 23: PCB Copper Inner Layer 1                             | 37 |

| Figure 24: PCB Copper Inner Layer 2                             | 38 |

| Figure 25: PCB Copper Bottom                                    | 39 |

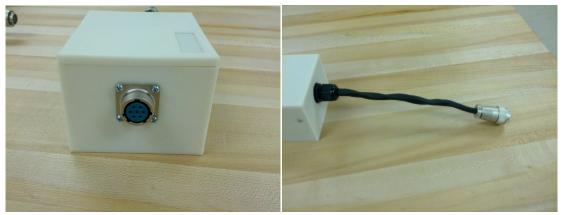

| Figure 26: Complete Enclosure                                   | 40 |

| Figure 27: Complete Enclosure                                   | 40 |

| Figure 28: Input and Output Connectors of NWSP                  | 41 |

| Figure 29: Hierarchy Chart                                      | 43 |

| Figure 30: High Level Flow Diagram                              | 45 |

| Figure 31: Main Loop Diagram                                    | 46 |

| Figure 32: Application Flow Diagram                             | 47 |

| Figure 33: Message Parse Flow Diagram                           | 48 |

| Figure 34: LabVIEW GUI Receive Function                         | 50 |

| Figure 35: LahVIEW GUI Tahle View                               | 50 |

| Figure 36: LabVIEW GUI Configuration View                    | 51 |

|--------------------------------------------------------------|----|

| Figure 37: LabVIEW GUI Graphing Feature                      | 52 |

| Figure 38: Alpha Design Results of Current Sensor Conversion | 58 |

| Figure 39: Current Sensor Output Offset Equivalent Results   | 59 |

| Figure 40: Bravo Design Signal Conditioning Solution Results | 59 |

# **List of Tables**

| Table 1: Alpha Board Costs | 42 |

|----------------------------|----|

| Table 2: Bravo Board Costs | 42 |

| Table 3: Test Matrix       | 53 |

# 1.0 Introduction

## 1.1 General

NASA is currently developing the Deep Space Habitat (DSH) to explore planets, asteroids, and moons beyond low earth orbit. Developing the DSH will allow a crew of four to live and work in space for up to a year. The DSH consists of a propulsion stage, Destiny-derived lab module, and an airlock. However, deep space missions present unique challenges. NASA has given universities the opportunity to participate in the eXploration Habitat (X-Hab) Academic Innovation Challenge, which will allow student teams to address specific technical challenges with innovative ideas and solutions. Experimental Control Logic Laboratory (XCLL), a team of undergraduates from Texas A&M University, has been selected to engineer and construct the NASA Wireless Smart Plug (NWSP).

# 1.2 Background

Power is a vital and limited resource on deep space missions. With crews spending up to a year in space, efficient use of the limited power on the DSH is critical. Presently, there is no way to monitor the current draw of specific end-devices connected to the DSH power system. If an end-device is drawing more current than expected, NASA needs to be able to detect and disconnect that specific end-device. The NWSP will be a small device that will plug into an outlet on the DSH. The user's end-device will be plugged into the NWSP. The NWSP will monitor the current draw of that end-device and wirelessly transmit the amperage to a Master Control Unit (MCU).

## 1.3 Justification

The NWSP will allow NASA to monitor the current draw of end-devices plugged into the DSH. Current measurements from each NWSP will be transmitted to the MCU, which will place all current readings in a table. The table will allow NASA to quickly see the current draw of each end-device plugged into each NWSP. The NWSP will have the capability to disconnect an end-device from the DSH power system. This will allow NASA to perform manual-defined load shedding to maximize the duration of the available power. NASA will receive five NWSP from XCLL. Each NWSP will be ready to use and connected to the MCU. XCLL will provide all source code to NASA, which will allow NASA engineers to modify the NWSP embedded logic or the MCU software. Once XCLL has completed creating the five NWSP units, Mobile Integrated Solutions Laboratory (MISL) will install the NWSP into the DSH mock-up.

# 2.0 Problem Statement & Scope

The five NWSPs delivered to NASA will be proof of concept prototypes intended to extend the mock-up version of the Deep Space Habitat's (DSH) capabilities to monitor and control power usage while still on Earth. The NWSPs will be used for testing and mock-up evaluation purposes only, and, therefore, are to be removed before flight or actual implementation in space.

# 2.1 Functional Requirements

As specified in the original contract solicitation, several key functional requirements have been outlined for the NASA Wireless Smart Plug. These requirements have been set to fully define the scope of the NWSP project.

## 2.1.1 Power Control

Support for 120VDC and/or 28VDC

The NWSP will be able to operate from either or both a 120VDC and/or 28VDC input.

Near Real-Time Monitoring and Control

The NWSP will be able to provide the capability to monitor and control the end-device's current related information to inform the user in near real-time.

Fail Safe

The NWSP will be able to fail safely in the event of failure. Safely has been defined as failing open, whereby, the end-device ceases to operate as if disconnected from the DSH.

Windows Based Master Control Unit (MCU)

The NWSP will send and receive data through the Master Control Unit configured on a Windows based platform running a LabVIEW executable.

#### 2.1.2 Communications

Wireless Monitoring, Configuration and Control

The NWSP unit will transmit its measurements data wirelessly to the MCU. The settings to configure and control the NWSP will be initiated at the MCU and wirelessly transmitted to the NWSP.

Data Rate

The NWSP embedded software will be able to sample the current at least once per second to report this data to the Master Control Unit.

• Use of a Nivis VersaNode210 (VN210) Radio

The NWSP will use a Nivis VN210 radio as its wireless radio peripheral to integrate with the DSH.

Support Nivis VersaRouter900 (VR900) Standards

The NWSP will be able to communicate with the Master Control Unit through the Nivis VR900 router via SPI and ISA 100.11a standards.

## 2.1.3 Form Factor & Fit

# • Cannon-Type Connector

The NWSP will have a 5 (or more) pin Cannon-type connecter available for both its input and output from the DSH and to the end-device respectively.

# • Integration with DSH

The NWSP system will be able to integrate and operate within the DSH system.

# • Deliver Five NWSP Units for Evaluation

Five operational NWSP units will be delivered for installation and evaluation on the DSH mockup.

# 3.0 Design Implementation Strategy and Overview

When the DSH receives more demand for electrical power than its available capacity can deliver, the habitat must resort to rationing the available electricity to its higher priority enddevices. This process is called load shedding. Given that XCLL is responsible for delivering five NWSP units, five end devices will be monitored and controlled, each of which can be configured and assigned a priority level by the user. This would enable the ability for an autonomous load shedding capability, such that when any one of the five devices is not supplied enough power or exceeding power based on the current sense measurements, the NWSP will disconnect the power supply from the lowest priority device. The autonomous disconnect ability is not required for the NWSP prototype and has been omitted from design due to the undesired possibility of autonomously disconnecting an end-device that the user would otherwise have needed to continue to operate. Alternatively, a manual feature will be the primary mode of operation such that the human user has all control over connect and disconnect capabilities of the NWSP. By manually prompting the user through the National Instrument's (NI) LabVIEW Graphic User Interface (GUI) executable that the current measurements are being read lower or higher than the set operating or optimal values, disconnecting the end-device in question will reside upon user's discretion.

#### 3.1 Hardware

Based on the description of the X-Hab Challenge Solicitation, the NWSP shall use a Nivis VersaNode 210 radio and a Texas Instruments (TI) MSP430F5438A microcontroller to interface to the present DSH wireless mesh network through a Nivis VersaRouter 900 gateway.

## **3.1.1** Microcontroller

The MSP430 microcontroller is equipped with both Serial Peripheral Interface (SPI) and Universal Asynchronous Receiver/Transmitter (UART) standard capabilities to communicate with the Nivis VersaNode 210 radio; however, only one may be utilized. NASA prefers the use of SPI communication due to the faster data speeds. In order to translate the output data from the current sense and voltage sense components, Analog-to-Digital Converter (ADC) ported pins are utilized with 12-bit precision for 4096 steps of 0.8mV LSB increments when using a 3.3V reference. Given NASA's requirement of monitoring current at maximum of 100mA increments, 51 steps of precision are required. This precision can be accounted for using a 6-bit or greater ADC at 51.6mV LSB increments or smaller. I/O pins are used as the driving sources for the solid-state switching relay and other potential enable signals. The clock rate is required to update the LabVIEW GUI at 1 sample per second. Multiple measurements, current calculations, and data transmission must occur within this limit.

#### 3.1.2 Nivis VersaNode 210

Nivis has recently upgraded their hardware and software release to version 2.7. However, to interface with the present DSH wireless mesh network, NASA does not require an update for NWSP project purposes. Instead, the Nivis VersaNode210 will be required to operate with

firmware version 4.3.14 (Upg\_VN210\_FullAPI\_SpeedupSPI\_ExtWakeup\_v04\_03\_14), while the Nivis VersaRouter 900 will operate on development release version 2.6.39 for intended and NASA proven compatibility. The Nivis VersaNode can communicate with the MSP430 using SPI or UART; however, the VN210 firmware is designed for SPI communication. Therefore, SPI will be the primary standard of operation. The UART interface is mandatory, however, in the case that the VN210 must be upgraded or operated in debug mode.

## 3.2 Software

Though the X-Hab Challenge Solicitation does not specify a GUI software executable requirement, the NWSP must be monitored and controlled by a MCU running on Windows Operating System (Windows XP or later). Due to XCLL's experience and knowledge of National Instrument's LabVIEW, this program was selected and approved as the MCU's front end GUI. The GUI will display numeric indicators for measured current and voltage values, controls to manually disconnect or connect end-devices, and controls to add or remove NWSPs from the GUI. NASA did not specify a GUI software requirement because they intend to port the data received by the DSH's VR900 from the NWSP into their proprietary application. When using the SPI standard, select parameters must be configured for the serial line input. These parameters include COM port, baud rate, data bits, stop bits, parity, and flow control. These universal parameter settings allow the NWSP's data to be used on interchangeable platforms.

# 3.3 Integration

MISL will deliver the five NWSPs to NASA JSC to be integrated into the mock-up DSH. Three integration tactics will be required for complete confirmation. The first tactic will require the use of XCLL's hardware platform, a laptop, brought by MISL. By connecting the DSH's VR900 to the laptop, the test matrix can be executed to ensure the NWSPs and GUI executable are compatible with interchangeable VR900s. The second tactic will require the GUI executable to run on NASA's hardware platform to ensure compatibility among varying hardware platforms and Windows Operating Systems. The third tactic will require configuration of NASA's proprietary application to interface with NWSP's parameters.

# **4.0 System Requirements**

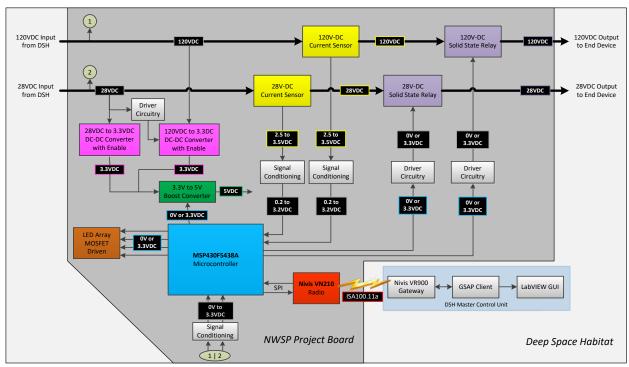

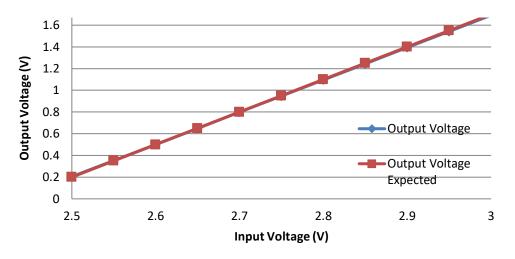

The NWSP is a current monitoring and control device that enables users to identify and respond to situations when an end-device being used on NASA's mock-up Deep Space Habitat (DSH) is exceeding optimal current draw. This section discusses the requirements requested by NASA, as well as the approved features appended by XCLL to enable demonstration and integration on the mock-up DSH. The Conceptual Block Diagram in Figure 1 illustrates an overview of both NWSP operation and integration to the DSH and MCU.

Figure 1: Conceptual Block Diagram

#### 4.1 Hardware

The DSH will be able to output either or both 120VDC and 28VDC from the onboard outlets. The NWSP is expected to be able to power its internal circuitry using one of the two available voltages, given the NWSP is not a battery operated device. Two components specified by NASA are expected to be used as part of the NWSP solution: the Texas Instruments MSP430F5438A microcontroller and Nivis VersaNode 210 radio module. Both of these components will require 3.3V to operate, thus 28VDC or 120VDC must be efficiently regulated to 3.3V. To enable integration onto the DSH, 5 (or more) pin cannon-type connectors were requested by NASA. Though only for evaluation purposes, these connectors will simulate the actual connector type NASA may ultimately use for the actual re-designed for space qualification NWSP solution. The components comprising of the NWSP circuitry are to be low-power profiled. NASA does not want the NWSP to noticeably impact the end-devices operation in the case near maximum allowable output from the DSH is necessary for an end-device to operate.

#### 4.2 Software

# **4.2.1** Embedded Intelligence Software

The primary purpose of the NWSP is to measure the current draw of an attached end-device (load). The Texas Instruments MSP430F5438A microcontroller has 12-bit ADC pins available for the required conversion process. NASA has requested the monitoring of current update on the MCU at a rate 1 sample per second, with precision of +/- 3% full scale (150mA) up to 5 amperes. However, the Texas A&M University stakeholders have requested precision of +/- 100mA. The microcontroller must be able to control whether an end-device is allowed power in the event the user configured current threshold has been exceeded. The DC solid-state relays used require a control voltage of at least 2.7V to close the relay to complete the circuit of the end-device.

# **4.2.2 Graphic User Interface Software**

NASA did not request that a graphic user interface be made available for the NWSP project; however, in order for XCLL to demonstrate that all functional requirements are met, a custom graphic user interface is required. XCLL has developed a LabVIEW executable to operate on a Windows based operating system specifically for the purposes of demonstration. NASA will have the option of modifying the LabVIEW executable to fit their needs, or discard the LabVIEW executable to use their proprietary software instead. The LabVIEW GUI was designed according to the required use of the Nivis ISA100.11a standard with an SPI protocol.

#### 4.3 Enclosure

Based on the X-Hab solicitation, NASA has required the NWSP sensor shall have a small form factor slightly larger than the size of an AC power plug that contains an AC to DC converter. NASA did not specify the dimensions for performance specification purposes, and ultimately adjusted the requirement such that XCLL be able to make the enclosure as small as possible when using the four layer PCB Bravo solution. The enclosure is to enable a panel mounted female connector as the output to the end-device, while using a pigtail extended male connecter to connect to the DSH output. XCLL has appended local LED indicator slots on the NWSP enclosure for local analysis.

# **4.4 Performance Specifications**

#### Voltage Source

The NWSP will be able to connect to a 28 VDC and/or 120 VDC source. If both sources are present, the NWSP will default to the 28 VDC for internal power usage.

#### Monitor Current

The NWSP will be able to monitor current up to 5 A with an accuracy of at least  $\pm$  3% of full scale.

#### Control Power

The NWSP will be able to set and control current from 0 to 5 A in 0.1 A increments. If the current flowing through the NWSP ever exceeds the set point, the user will be prompted to disconnect the NWSP from the end-device.

# • Data Collection and Response

To allow for near real-time monitoring, the NWSP will be able to transmit at least 1 sample per second. Furthermore, loads exceeding the set current limit will be prompted for disconnect from power within 3 seconds of continual over-current.

#### User Interface

NWSP configuration and monitoring will be done remotely using a LabVIEW GUI. This standalone GUI will run on a Windows XP based master computer and allow users to monitor NWSPs and set control routines. The ability to add or remove multiple NWSP units from the GUI will be made available through front end controls.

# Networking and Communications

In order to integrate into the current DSH wireless mesh network, the NWSP will use the Nivis VersaNode 210 wireless radio to communicate with the Master Control Unit through the Nivis VersaRouter 900 gateway located onboard the DSH. This requires that the NWSP implement the ISA100.11a standard.

#### Size

The NWSP will be no larger than a typical AC to DC converter.

#### Failure Recovery

In the event of failure, the NWSP must maintain safety. This safety measure is also taken if the NWSP loses its connection with the master control for prolonged periods of time.

#### Power Consumption

The NWSP will act as a low power node when integrated into the DHS network. The Texas Instruments MSP430F5438 microcontroller will be used as its central control intelligence in order to minimize power requirements.

#### Deliverables

There will be at least 5 NWSP units delivered and installed for testing and demonstration on the NASA DSH.

# 5.0 System Analysis

The MCU must be able to display the current draw of an end-device; therefore, understanding the process of digitizing and sensing current is critical to the operation of the NWSP. Due to the wireless communication that exists between the NWSP and the MCU, understanding the packet structure is required for appropriate conversion to port into the LabVIEW executable GUI. These two processes will be the primary operations analyzed at the NWSP's.

#### **5.1 Current Sense Conversion**

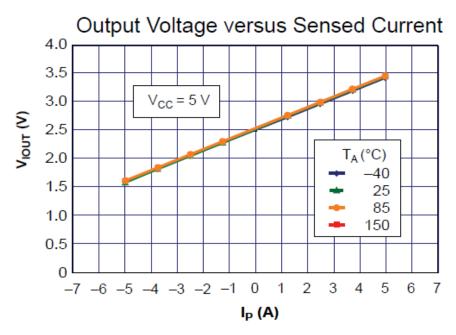

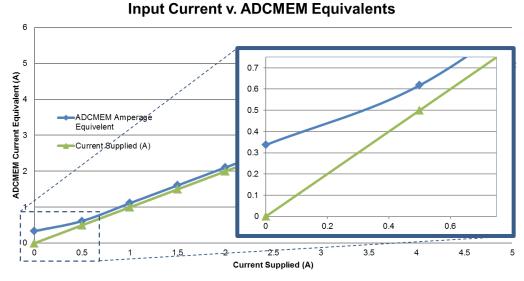

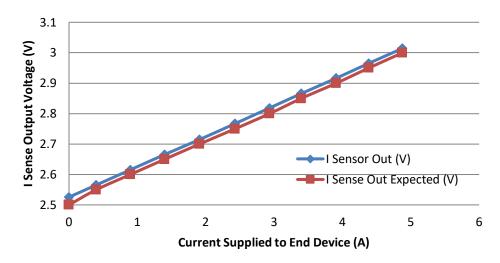

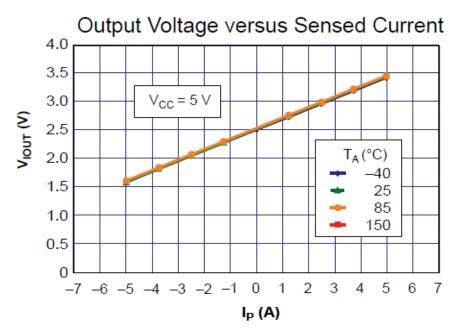

The current sensor must be accurate to within 100mA. The ACS714 hall-effect linear current sensor can accomplish this without loading down the power line due to the low internal conductor resistance of  $1.2m\Omega$ . Figure 2 shows the current range of which the ACS714 can output an equivalent voltage for when the supply voltage is 5V.

**Figure 2: Current Sensor Characterization Graphed**

This sensor uses the hall-effect to detect fluctuation in the magnetic field as the current changes. The sensor will output a linear voltage proportional to the current with an offset of+2.5V. The output voltage will change at a rate of 185mV/A. The output of the ACS714 will ultimately be connected to an ADC pin on the MSP430 post signal conditioning.

## **5.1.1 Signal Conditioning**

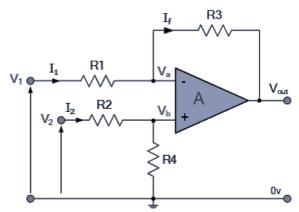

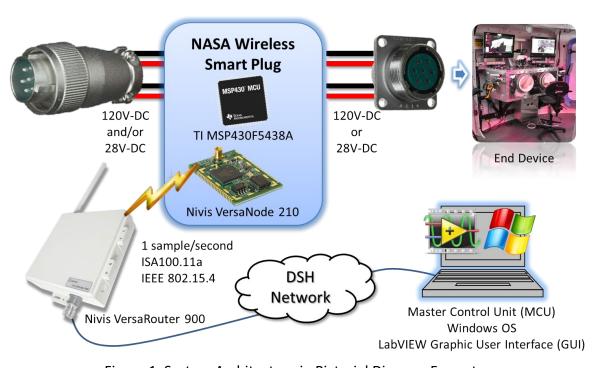

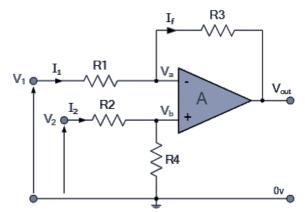

To apply an offset and gain to the voltage output proportional to current sensed, an operation amplifier must be used to amplify the difference between two voltages. This will result in an operational amplifier circuit equivalent to a subtractor. This type of operational amplifier circuit is commonly known as a Differential Amplifier configuration as shown in Figure 3.

**Figure 3: Differential Amplifier Configuration**

By connecting each input to ground, and solving for the output voltage, the transfer function for a <u>D</u>ifferential Amplifier circuit is given as:

$$V_{out} = -V_1 * \left(\frac{R_3}{R_1}\right) - V_2 * \left(\frac{R_4}{R_2 + R_4}\right) * \left(\frac{R_1 + R_3}{R_1}\right)$$

If input V1 is higher than input V2 the output voltage sum will be negative, and if V2 is higher than V1, the output voltage sum will be positive. By adding more resistors in parallel with the input resistors R1 and R3, the resultant circuit can be made to either "Add" or "Subtract" the voltages applied to their respective inputs.

## **5.1.2** Analog to Digital Conversion

The resolution of the converter indicates the number of discrete values it can produce over the range of analog values. The values are usually stored electronically in binary form, so the resolution is usually expressed in bits. In consequence, the number of discrete values available, or "levels", is a power of two. For the purposes of the NWSP, an ADC with a resolution of 12 bits can encode an analog input to one in 4096 different levels, since  $2^{12} = 4096$ . The values can represent the ranges from 0 to 4095 (i.e. unsigned integer) or from -2048 to 2047 (i.e. signed integer), depending on the application.

Resolution can also be defined electrically, and expressed in volts. The minimum change in voltage required to guarantee a change in the output code level is called the least significant bit (LSB) voltage. The resolution Q of the ADC is equal to the LSB voltage. The voltage resolution of an ADC is equal to its overall voltage measurement range divided by the number of discrete values:

$$Q = \frac{E_{FSR}}{2^M - 1}$$

where M is the ADC's resolution in bits and EFSR is the full scale voltage range (also called 'span'). EFSR is given by:

$$E_{FSR} = V_{RefHi} - V_{RefLow}$$

where  $V_{RefHi}$  and  $V_{RefLow}$  are the upper and lower extremes, respectively, of the voltages that can be coded.

Normally, the number of voltage intervals is given by

$$N = 2^{M} - 1$$

where M is the ADC's resolution in bits.

That is, one voltage interval is assigned in between two consecutive code levels.

Using the known equations, XCLL has calculated the resolution of the NWSP as follows:

- Full scale measurement range = 0 to 3.3 volts

- ADC resolution is 12 bits:  $2^{12} 1 = 4096 1 = 4095$  quantization levels (codes)

- ADC voltage resolution, Q = (3.3 V 0 V) / 4095 = 3.3 V / 4095 ≈ 806 uV.

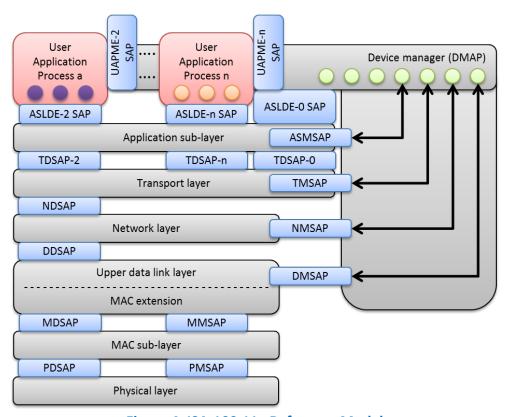

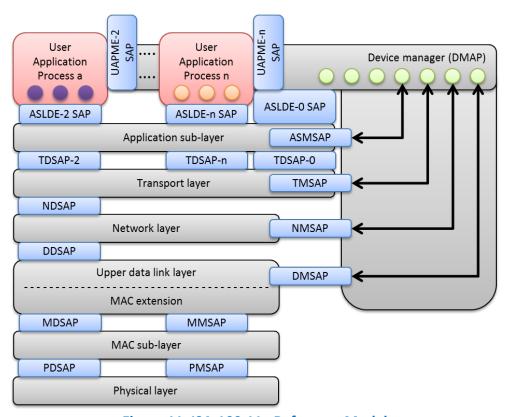

# 5.2 ISA-100.11a Wireless Standard

This standard uses the OSI layer description methodology to define protocol suite specifications, in addition to specifications for the functions of security, management, gateway, and provisioning for an industrial wireless network. The protocol layers supported are the physical layer (PhL), data link layer (DL), network layer (NL), transport layer (TL), and application layer (AL) as show in the reference model of Figure 4.

Figure 4: ISA-100.11a Reference Model

Each layer provides a service access point (SAP). The services of a layer are defined as the functions and capabilities of that layer that are exposed through the SAP to the surrounding layers. The services provided by a layer are defined by the data flowing through the SAP and, in

some cases, the states that a layer provides and the state transitions that are driven that perform the management function. Note that the device manager has a dedicated path to several of the lower layer protocol layers within a device. This is to provide direct control over the operation of these layers, as well as provide direct access to diagnostics and status information. All devices compliant to this standard are considered managed devices. All devices shall implement each SAP used by the DMAP for every protocol layer they implement. A protocol layer typically encapsulates its payload, hereafter referred to as a service data unit (SDU), with a header and footer in a single protocol data unit (PDU) as show in Figure 5. The header and footer are often referred to as overhead, with the amount of overhead depending upon how much information is necessary for the protocol to function properly. Since one of the goals of this standard is to keep PDUs short, minimizing the amount of overhead is a key attribute. A complete description of each header and footer will be found in the appropriate protocol layer clause. A full PDU includes all headers and footers as shown in Figure 6. The amount of data (measured in octets) of an application PDU that can be sent in a single transmission is determined by the difference between the maximum PhL payload and the overhead of all headers and footers.

| Header SDU                          |           |           |           |                 | Footer    |           |           |

|-------------------------------------|-----------|-----------|-----------|-----------------|-----------|-----------|-----------|

| Figure 5: Single Protocol Data Unit |           |           |           |                 |           |           |           |

|                                     |           |           |           |                 |           |           |           |

| PhL header                          | DL header | NL header | TL header | Application PDU | TL footer | NL footer | DL footer |

|                                     |           |           |           |                 |           |           |           |

Figure 6: Full Protocol Data Unit

# **5.3 Serial Peripheral Interface**

The SPI bus can operate with a single master device and with one or more slave devices. If a single slave device is used, the SS pin may be fixed to logic low if the slave permits it. Some slaves require the falling edge (high to low transition) of the chip select to initiate an action, which starts conversion on said transition. With multiple slave devices, an independent SS signal is required from the master for each slave device. Most slave devices have tri-state outputs so their MISO signal becomes high impedance (disconnected) when the device is not selected. Devices without tri-state outputs can't share SPI bus segments with other devices; only one such slave could talk to the master, and only its chip select could be activated.

# 6.0 Hardware Design

# **6.1 Functional Block Diagram**

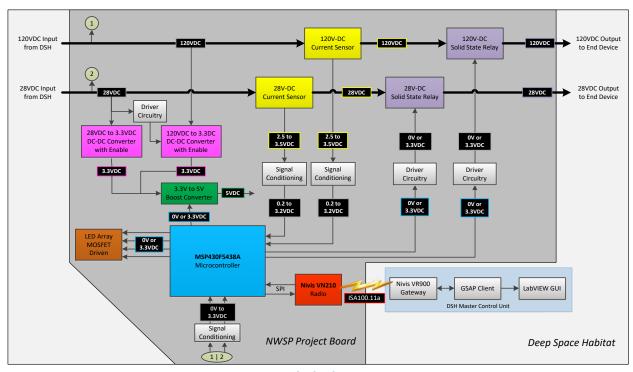

The Conceptual Block Diagram in Figure 1 provides an illustrative representation of the NWSP operation and interface methodology to the DSH and MCU. To explore these processes in more detail, the outline of specific hardware and signal types internal to the NWSP are represented in the Functional Block Diagram Overview in Figure 7. Each block representing a major internal process is color coded according to their block breakdowns in the following sections.

**Figure 7: Functional Block Diagram Overview**

The DSH will be sourcing either or both 28V-DC and 120VDC. Due to the possibility that both voltage sources will be available, the NWSP must only utilize a single supply voltage to power internal NWSP circuitry. The 120V-DC step-down converter is to be disabled in the case that both voltage sources are available. As compared to the 28V-DC power line, the 120VDC DC-DC converter is disabled given that more power is dissipated through the step down regulation process to power subsequent internal NWSP circuitry.

## 6.1.1 Microcontroller Interfaced with Radio Design

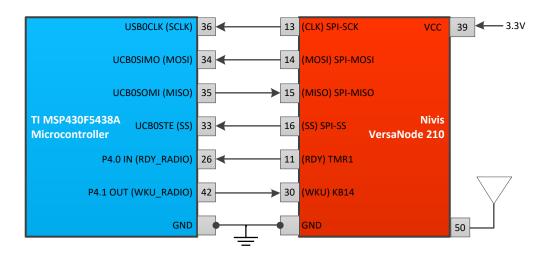

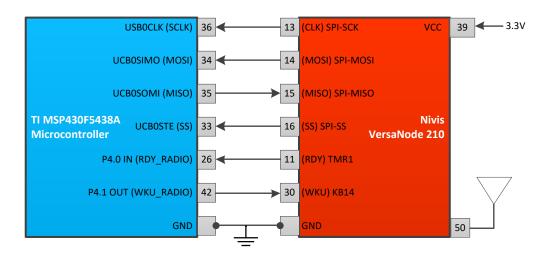

To achieve communication between the MSP430 microcontroller and Nivis VN210 radio, the ability to communicate by SPI or UART is made available to the user. SPI mode has been selected for the NWSP application based on the versioning and development release required by NASA. Figure 8 illustrates the connection scheme of the SPI interface format.

Figure 8: Microcontroller Interfaced with Radio Block Diagram

The Nivis VN210 has the option of utilizing the onboard SMT antenna connector for wireless communication, or, alternatively, using a custom or external antenna through pin contact 50. To initiate communication, the bus master (VN210) first configures the clock, using a frequency less than or equal to the maximum frequency the slave (MSP430 microcontroller) device supports. The master then transmits the appropriate chip select bit for the desired chip to a logic level 0 (chip select line is active low). If a waiting period is required, the master must wait for at least that period of time before starting to issue clock cycles. During each SPI clock cycle, a full duplex data transmission occurs. The master sends a bit on the MOSI line, and the slave reads it from that same line, while the slave sends a bit on the MISO line, and the master reads it from that same line.

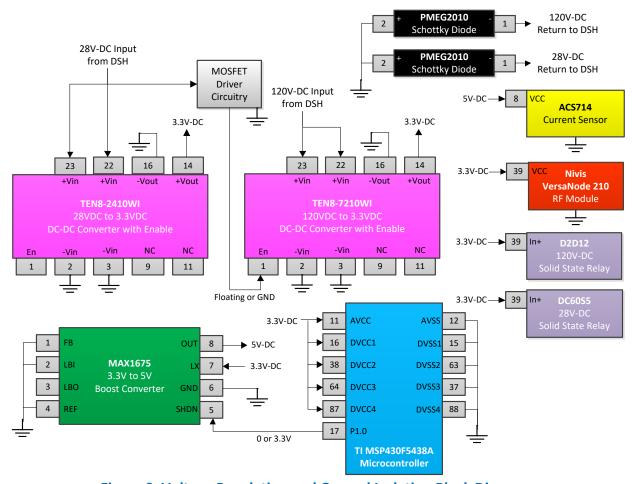

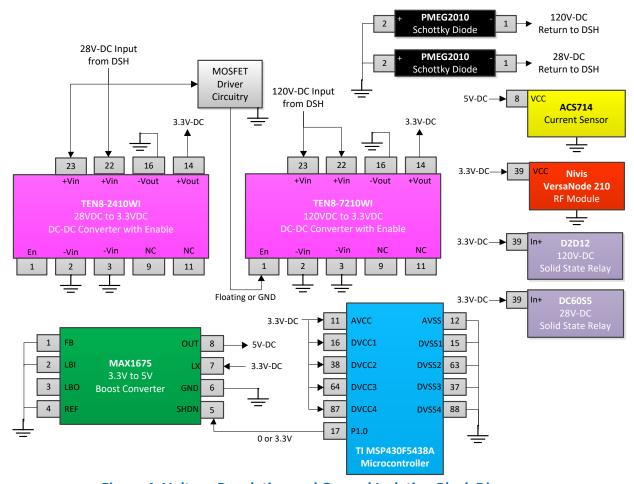

#### 6.1.2 Voltage Regulation and Ground Isolation for Internal Circuitry Design

To efficiently power the internal circuitry of the NWSP, the load line voltages must be utilized without significantly impacting the power available to the end-device. Given the power budget of the NWSP components, using highly efficient DC-DC converters will prevent potential impactful losses. Figure 9 shows the Voltage Regulation Block Diagram focused section of the Functional Block Diagram.

Figure 9: Voltage Regulation and Ground Isolation Block Diagram

Major components to be powered include the TI MSP430 microcontroller, the Nivis VN210, two current sense modules, and two DC solid state relays. The TEN8-2410WI and TEN8-7210WI both supply 3.3V-DC for the internal circuitry's components, whereby, the DSH's output of 28VDC and 120VDC are regulated respectively. The solution for the 120VDC to 28VDC regulation must include an enable low option, such that when the 28VDC source is present, the 120VDC regulation is disabled. A boost converter is used to step-up 3.3V to 5V in order to power the current sensors and the operational amplifiers used in the signal conditioning and driver circuits. The NWSP is not to act as the common ground of the 28VDC and 120VDC DSH supplies, thus a Shottky diode is used to isolate the NWSPs from the returns of both DSH voltage supplies. The DSH voltage supplies are only common at the solar panel array power source.

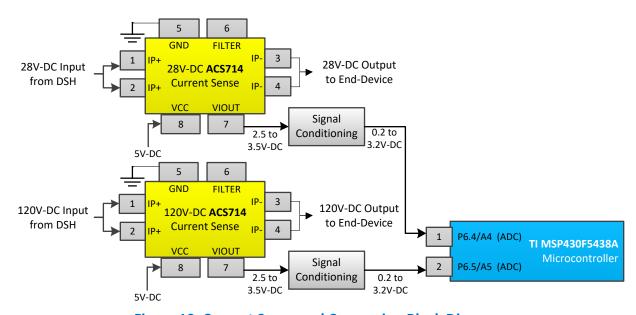

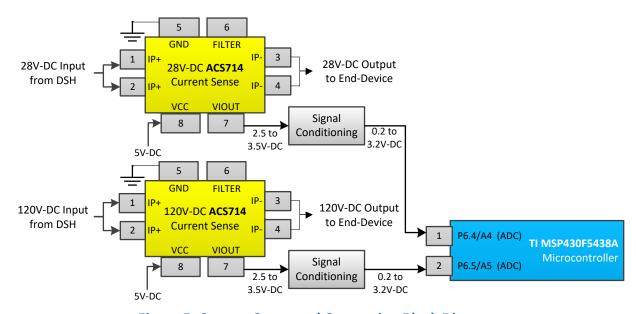

# **6.1.3 Current Sense and Conversion Design**

In order to prompt the user to disconnect in the case of out of range current measurement detection, the TI MSP430 microcontroller must be able to precisely convert the analog output of the ACS714 current sense module to a digitally interpretable value. Figure 10 shows the connection scheme of the Current Sense and Conversion Design.

Figure 10: Current Sense and Conversion Block Diagram

Two independent current sense modules for each input voltage will require the same signal conditioning between the output voltage paths and the microcontrollers ADC inputs. The typical ADC signal conditioning process consists of an offset, gain, and low pass filtering of the raw analog voltage. Given the 0 to 10A current range of interest on the ACS714 module equates to a 2.5V to 3.5V range output, the raw analog signal must be offset by 2.3V, applied a gain of 3.2V, and low pass filtered through a differential amplifier and current sensor's FILTER pin.

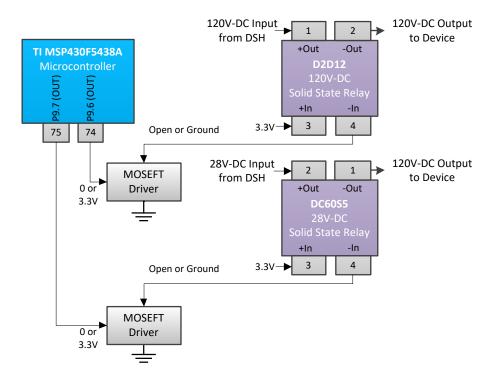

#### 6.1.4 Relay Control Design

The DC solid state relays are used to connect and disconnect the output from the DSH to the end-device. When the user is prompted to disconnect the end-device due to the current threshold being exceeded, the relays must be configured appropriately as a part of the command message at the MCU. Figure 11 shows the connection scheme of the Relay Control Design.

Figure 11: Relay Control Block Diagram

The driver circuit for the DC solid state relay will consist of an n-channel enhancement mode MOSFET circuit gated on or off by the MSP430. The MOSFET's gain will be connected to output of the relay's control terminal, such that when the MOSFET is gated off, the relay is opened, and the end-device does not receive power. When the MOSFET is gated on, the output of the relay's control terminal is shorted to ground, completing the circuit, and closes the relay to enable power to the end-device.

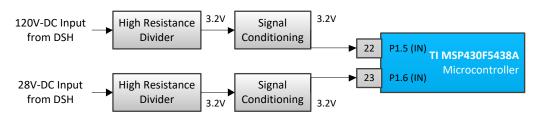

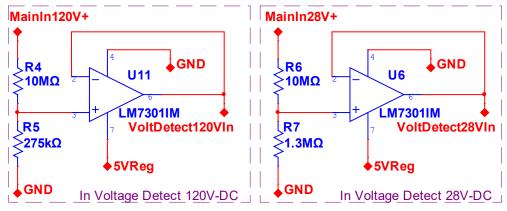

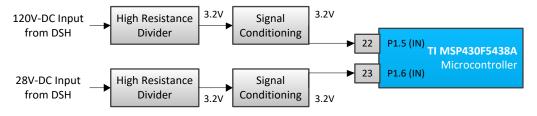

## **6.1.5 Voltage Measurement Design**

In addition to measuring the current draw of the end-device, the NWSP will be equipped with the ability to detect the voltage at the input of the NWSP. Figure 12 depicts the connection scheme of the Voltage Detection Design.

Figure 12: Voltage Measurement Block Diagram

To ensure the end-device is receiving either 120V-DC or 28V-DC, this monitoring feature is to be used as a multi-purpose indicator. Indications as to whether the DSH is actually sourcing 120V-DC and/or 28V-DC or if the solid-state relay controlling these power lines are open or closed. The voltage divider circuit will be drawing power continuously, thus, the resistors selected must be of high magnitude in value (i.e. mega ohms or greater) to reduce current draw. The power consumed must be negligible to the power profile of the NWSP's internal circuitry. The unity gain buffer's high input resistance ensures the voltage transferred from the voltage divider circuit is reduced to a low input impedance level for the MSP430's digital I/O pin.

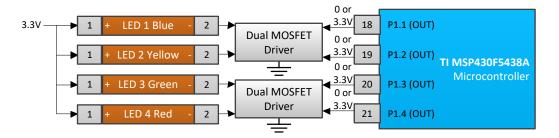

# **6.1.6 Light Emitting Diode Indicator Design**

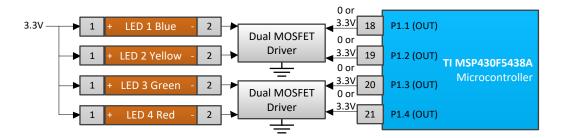

To locally indicate the status of the NWSP, an array of light emitting diodes (LEDs) are used to indicate specific connection states and warnings. This local indication will enable the user to visually identify immediate information without having to reference the graphic user interface. Figure 13 depicts the connection scheme of the LED indicator design.

**Figure 13: Light Emitting Diode Indicator Block Diagram**

The LEDs' cathodes can be held in two states, floating or shorted to ground. By default, the LEDs will be floating, and thus remain in the off state while the microcontroller is sourcing a low, OV signal. When the microcontroller outputs a high, 3.3V signal to the gate of the MOSFET, the LED's cathode, connected to drain, will short to ground through the MOSFET's source connected to ground. The blue LED is only on, and flashes at an on/off rate of 1 second when the NWSP is connected to the DSH network and transmitting. The yellow LED will be the first LED to turn on when attempting to initialize and is disconnected from the DSH network. The yellow LED will remain solid until the NWSP is connected to the DSH network. The green LED indicates the NWSP is connected to the network, but not transmitting. The red LED indicates that the current threshold configured on the NWSP has been exceeded, thus prompting that the user must decide whether to disconnect the NWSP from the end-device.

# 6.2 Schematic

The schematic of the NWSP has been divided into multiple schematics using global connectors to indicator interconnectivity. Each schematic represents a sub-circuit of a specific operation of

the NWSP, similar to the format of the Functional Block Diagram. The schematics will be explained on a component level to describe functionality.

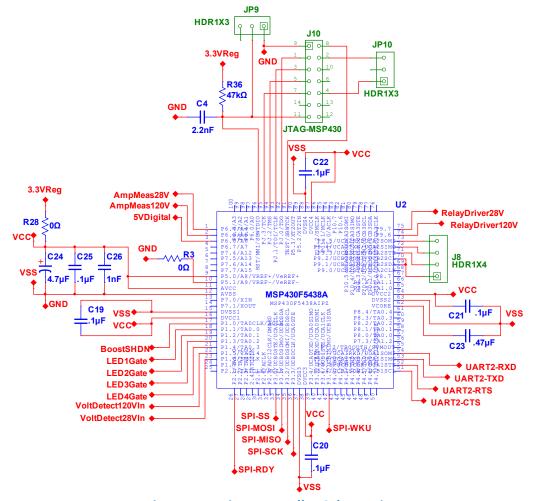

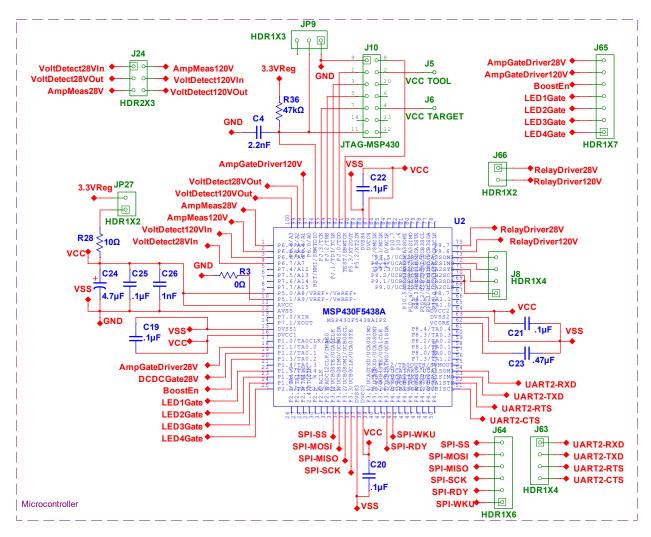

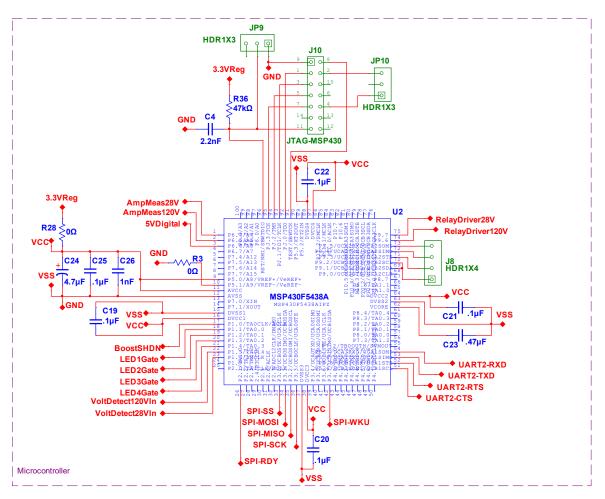

#### **6.2.1 Microcontroller Schematic**

The detailed microcontroller schematic is shown in Figure 14. The power provided to the microcontroller is 3.3V from the output of the DC-DC converter. A decoupling capacitor is used to decouple one part of this electrical circuit from the remainder of the NWSP. Noise caused by other circuit elements is shunted through the capacitor, reducing the effect they have on the rest of the circuit. The capacitor cannot provide DC power because it stores only a small amount of energy but this energy can respond very quickly to changing current demands. The capacitors effectively maintain power-supply voltage at frequencies from hundreds of kHz to hundreds of MHz (in the milliseconds to nanoseconds range). A 4.7uF, 0.1uF, and 1nF capacitor have been selected for the microcontroller's analog supply pin, while only 0.1uF are used on the digital supply pins.

The ADC12\_A module supports fast 12-bit analog-to-digital conversions. The module implements a 12-bit SAR core, sample select control, and a 16-word conversion-and-control buffer. The conversion-and-control buffer allows up to 16 independent analog-to-digital converter (ADC) samples to be converted and stored without any CPU intervention. Only three of the ADC pins must be used for the NWSP: current sensing of the 28V based end-device, current sensing of the 120V based end-device, and the digitization of 5V form the boost converter for calibration purposes. To interface to the VN210, the microcontroller is enabled to use both SPI and UART protocols. In synchronous mode, the USCI connects the device to an external system via three or four pins: UCxSIMO, UCxSOMI, UCxCLK, and UCxSTE. SPI mode is selected when the UCSYNC bit is set, and SPI mode (3-pin or 4-pin) is selected with the UCMODEx bits. In asynchronous mode, the USCI\_Ax modules connect the device to an external system via two external pins, UCAxRXD and UCAxTXD. UART mode is selected when the UCSYNC bit is cleared.

To drive LEDs low or high, detect the presence of voltage, and open or close relays, digital I/O pins are used as drivers and indicators. To enable onboard flash programming and debugging of the microcontroller, a 4-wire JTAG programming communication configuration has been designed.

**Figure 14: Microcontroller Schematic**

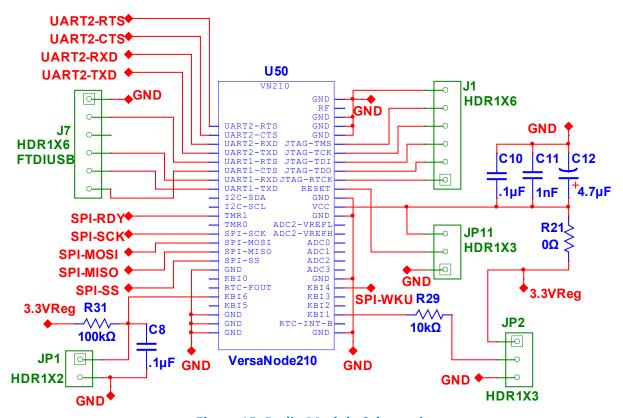

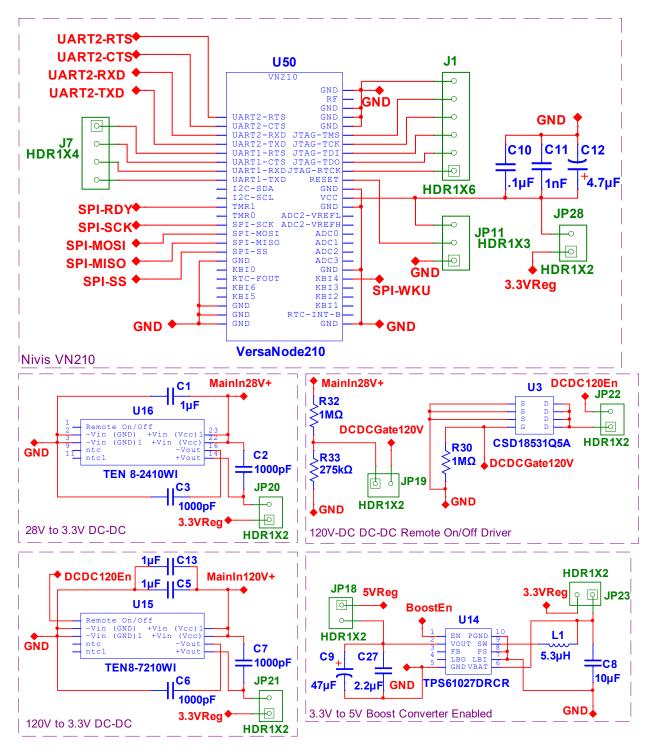

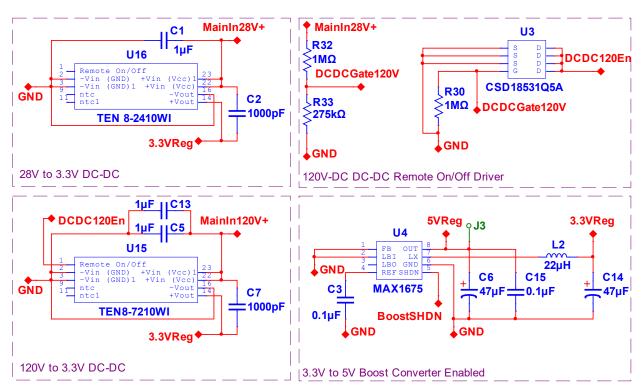

## **6.2.2 Radio Module Schematic**

The detailed VN210 radio module schematic is shown in Figure 15. The power provided to the radio module is 3.3V from the output of the DC-DC converter. The RESET pin must be held high in order for the module to operate. Though the SPI protocol is the primary means of interfacing with the MSP430 microcontroller, UART is made available as an alternative. For the purposes of provisioning the radio, KBI6 and KBI1 can be pulled high or low through the user of jumpers replicating push buttons. To upload firmware to the module, UART1 has been enabled to a fit FTDI-to-USB conversion pin format.

**Figure 15: Radio Module Schematic**

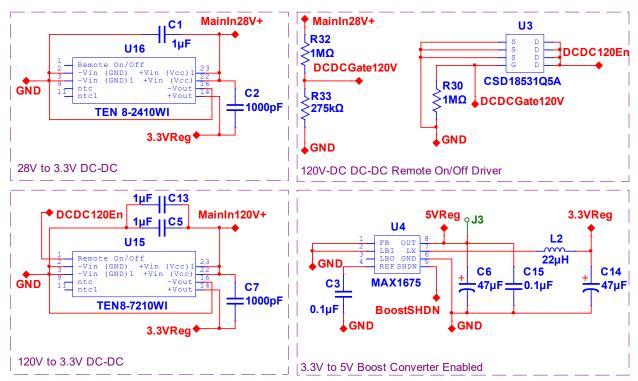

## **6.2.3 Power Schematic**

The detailed power schematic is shown in Figure 16. The TEN8-2410WI steps-down input voltages ranging from 9V to 36V down to 3.3V. The TEN8-7210WI steps-down input voltages ranging from 43V to 160V down to 3.3V. TEN8-2410WI will always be enabled to convert the expected input voltage of 28V, given the Remote On/Off pin is floating. As long as this pin remains floating, the TEN8-2410WI is in the on-state. However, the TEN8-7210WI can be disabled when 28VDC drives the gate of the CDS18531Q5A MOSFET high, resulting in the TEN8-7210WI Remote On/Off pin shorting to ground. When 3.3V is present, the MAX1675 boost converter activates. Though the boost converter has a SHDN' pin controlled by a digital high or low from the microcontroller, the boost converter is to remain high during the entire operation of the NWSP.

**Figure 16: Power Schematic**

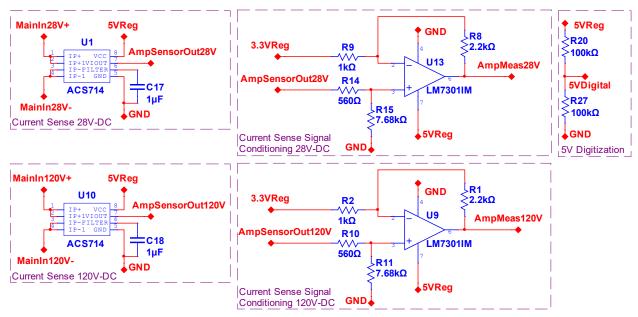

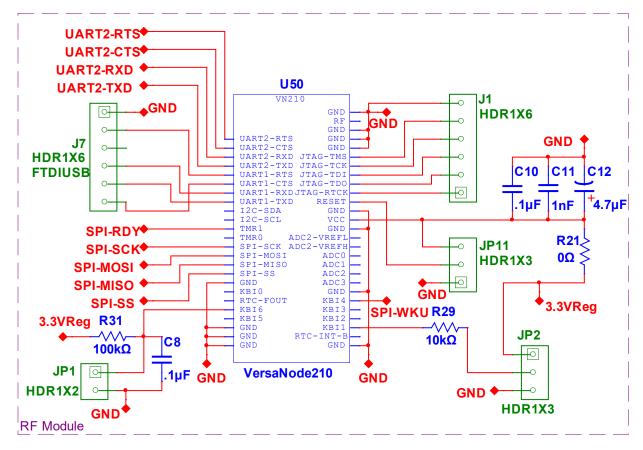

# **6.2.4 Current Sensing Conversion and Calibration Schematic**

The detailed current sensing conversion and calibration schematic is shown in Figure 17. The design of the current sense circuitry is based on the output of the current sensor. The current sensor has a FILTER pin. In low-frequency sensing applications, adding an RC filter to the output of the device improves the signal-to-noise ratio, and therefore the resolution, of the device output signal. The LM7301 rail-to-rail input-output operational amplifier has a minimum output swing of 112mV, thus the resistor configuration is designed such that the minimum output the signal conditioning circuitry is 200mV. Considering 5V exceeds the microcontroller's external reference voltage of 3.3V, a resistive voltage divider is used to reduce the voltage applied to the ADC pin to 2.5V. This voltage enables boost converter output offset in both the positive and negative direction to avoid saturation of the digitized signal.

Figure 17: Current Sensing Conversion and Calibration Schematic

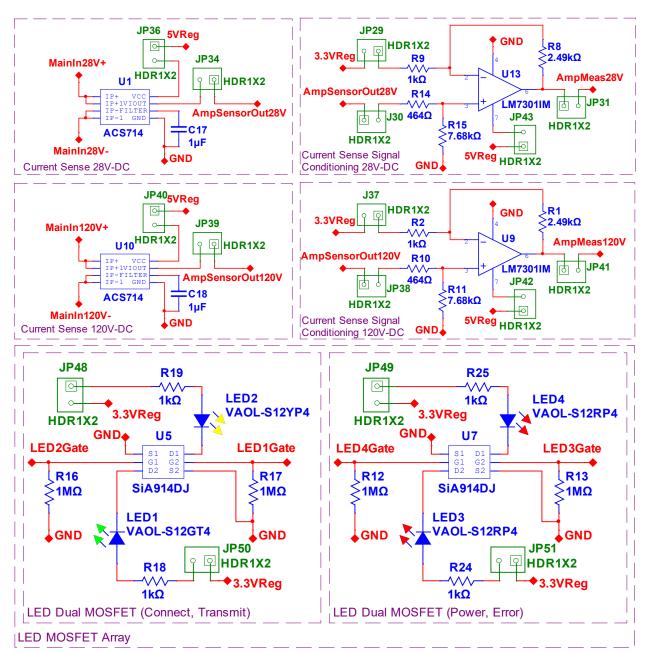

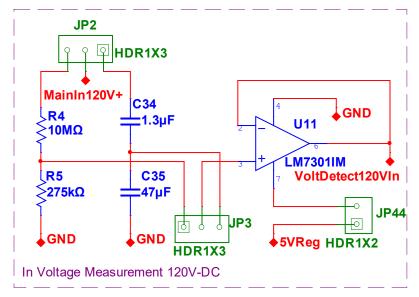

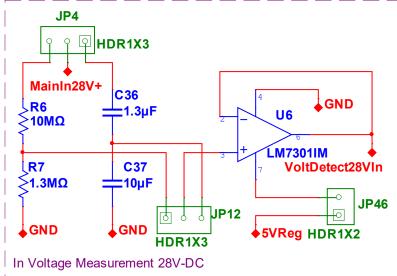

# **6.2.5 Voltage Detection Schematic**

The detailed voltage detection schematic is shown in Figure 18. Considering that voltage is only detected, and the exact value is not measured, a digital high or low is ultimately necessary to indicate whether the expected 28VDC and 120VDC supplies are present at the NWSPs input. To reduce the power dissipated by the resistive dividers, high resistive values are used to reduce both voltages to 3.2V. The subsequent LM7301 is used as a buffer amplifier to transfer a voltage from a first circuit (resistive divider), having a high output impedance level, to a second circuit (MSP430 digital I/O) with a low input impedance level. The interposed buffer amplifier prevents the second circuit from loading the first circuit unacceptably and interfering with its desired operation. In the ideal voltage buffer in the diagram, the input resistance is infinite, the output resistance zero (impedance of an ideal voltage source is zero).

**Figure 18: Voltage Detection Schematic**

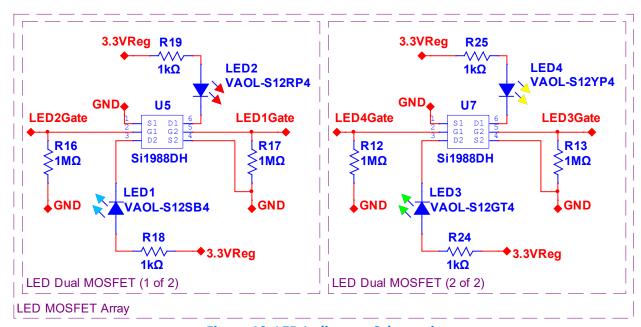

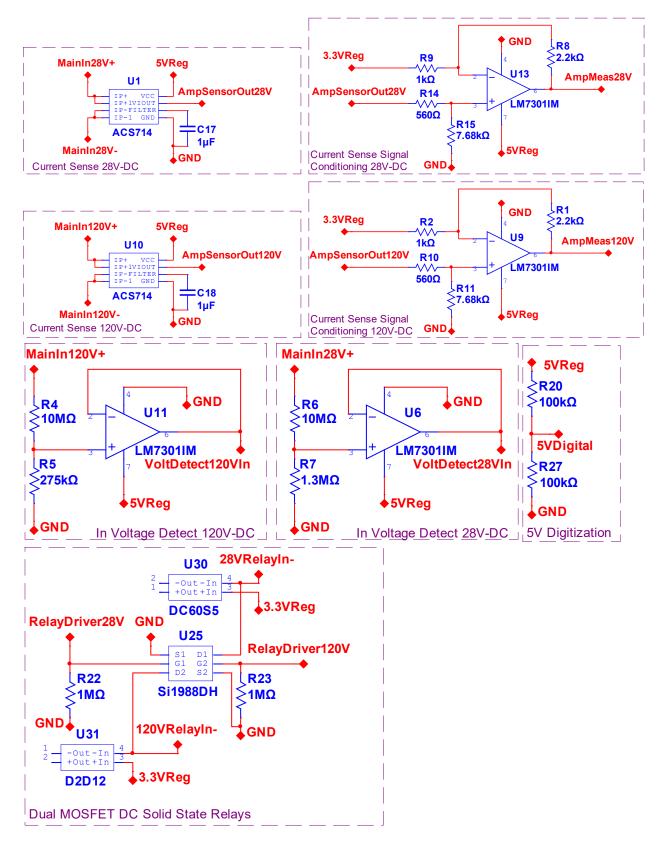

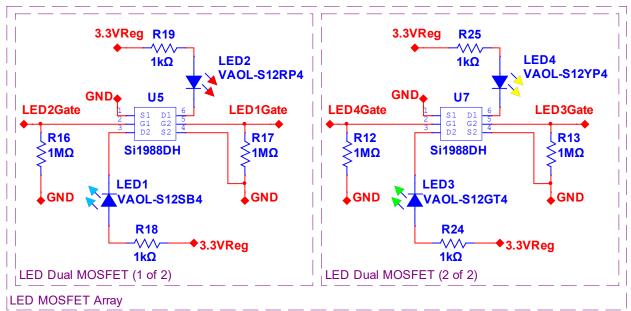

#### **6.2.6 LED Indicators Schematic**

The detailed LED indicators schematic is shown in Figure 19. Each LED receives 3.3V from the output of the DC-DC converts. The voltage drop of each LED was considered, whereby the red LED has the lowest voltage drop of 1.8V, while the blue LED has the largest voltage drop of 3V. The current supplied to each LED is limited by a  $1k\Omega$  resistor. Each LED is turned on or off based on the input to the MOSFET's gate voltage. If the microcontroller is outputting a low signal, the LED will be off given the cathode will remain floating at the drain of the MOSFET. The  $1M\Omega$  pull-down resistor ensures the gate will not be floating in the case the microcontroller's digital output is misconfigured or floating. When the gate of the MOSFET is high, drain shorts through the source to ground, thus completing the circuit of the LED.

**Figure 19: LED Indicators Schematic**

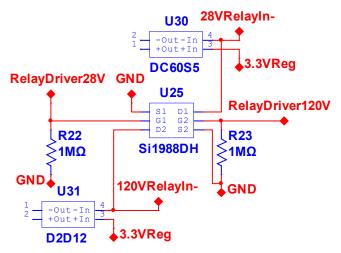

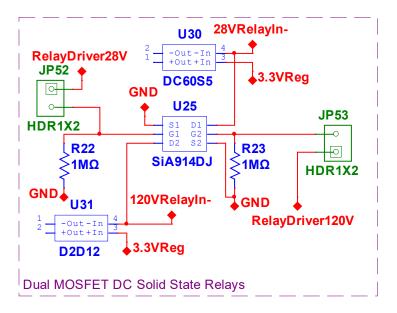

## **6.2.7 Relay Control Schematic**

The detailed relay control schematic is shown in Figure 20. The relays require a minimum of 2.7V at the control input in order to close the load side. 3.3V is supplied to the input of the control terminal of the relays. Similar to the LED control, when the gate of the MOSFET receives a low signal form the microcontroller's digital output, the relay will remain in open state given the control signal will be floating. When the gate of the MOSFET is supplied a high signal for the microcontroller's digital output, the relay control signal can complete its circuit by grounding through the drain-source of the MOFET. In the case the microcontroller's digital output is floating, a  $1M\Omega$  resistor is used as a pull-down resistor to set the gate in a low state.

**Figure 20: Relay Control Schematic**

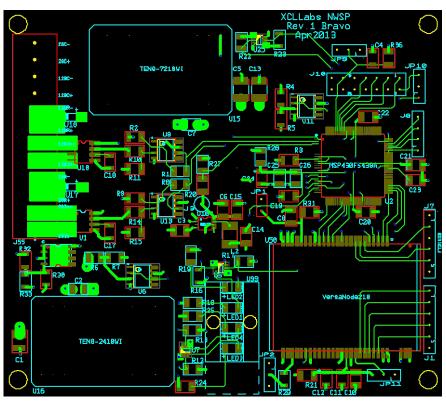

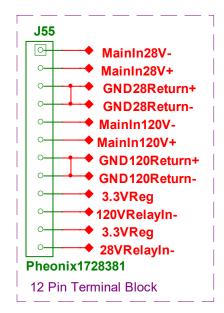

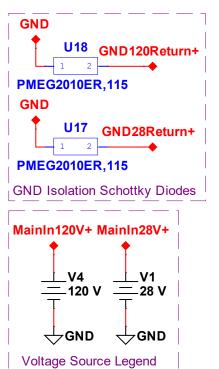

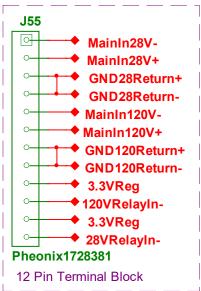

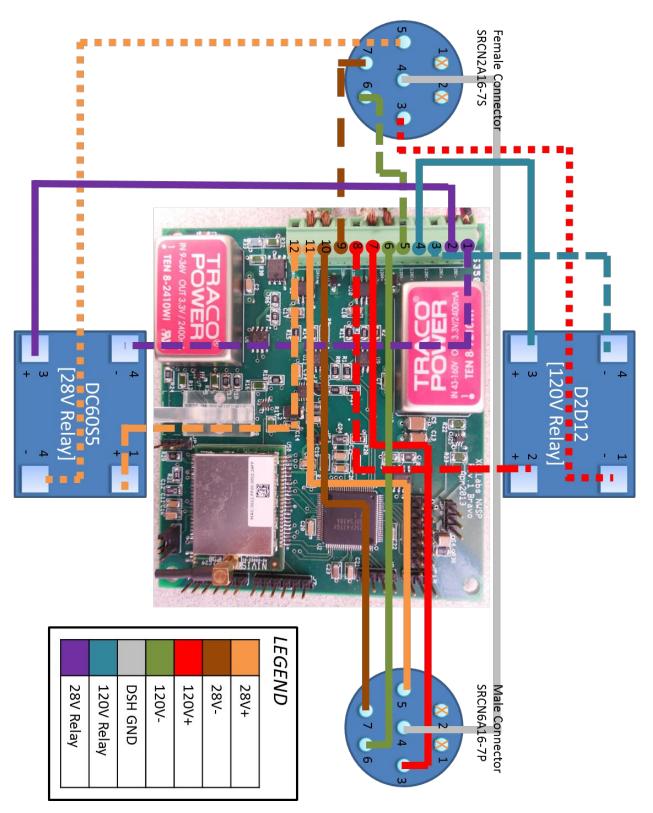

## **6.2.8 Connector and Ground Isolation Schematic**

The detailed connector and ground isolation schematic is shown in Figure 21. The 12-pin terminal block is used to interface the NWSP to the connectors of DSH and end-device. 16 gauge wire is used for all terminals pertaining to the input and output of the NWSP, while 20 gauge wire is used for the relay control terminals. The Shottky diodes share a common ground on the anode side, but are separated independently at the returns of the DSH voltage supplies, whereby one diode connects to the 28V return and the other diode connects to the 120V return.

**Figure 21: Connector and Ground Isolation Schematic**

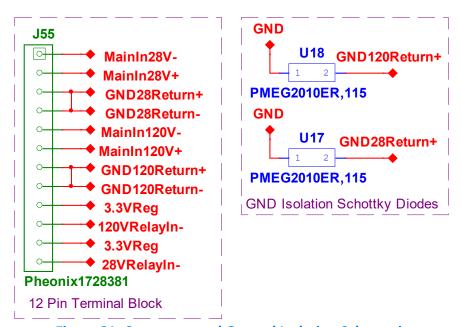

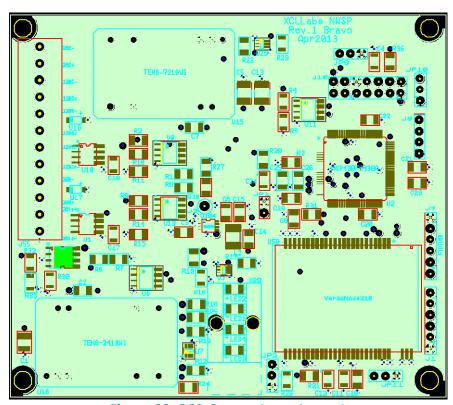

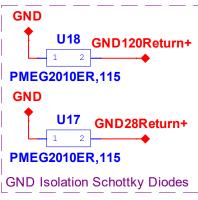

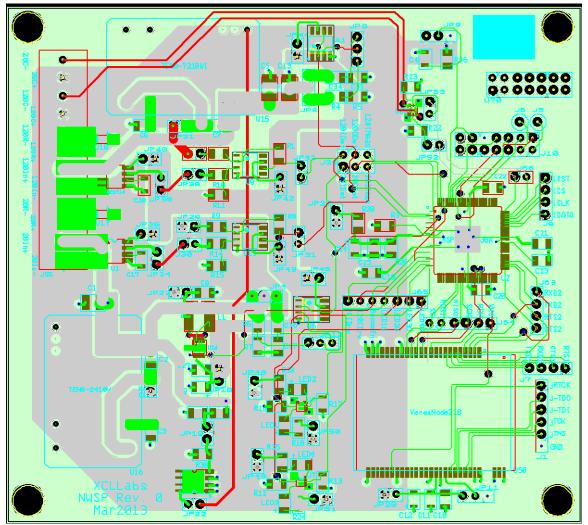

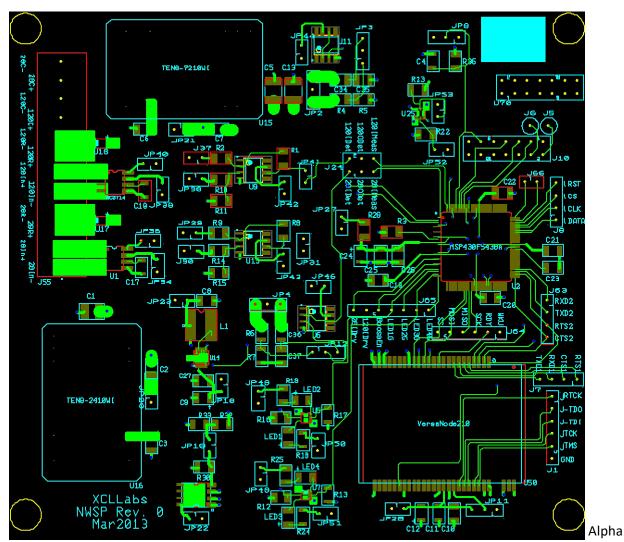

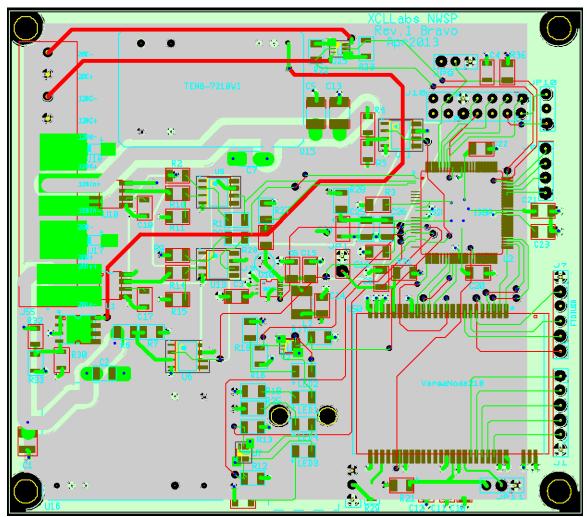

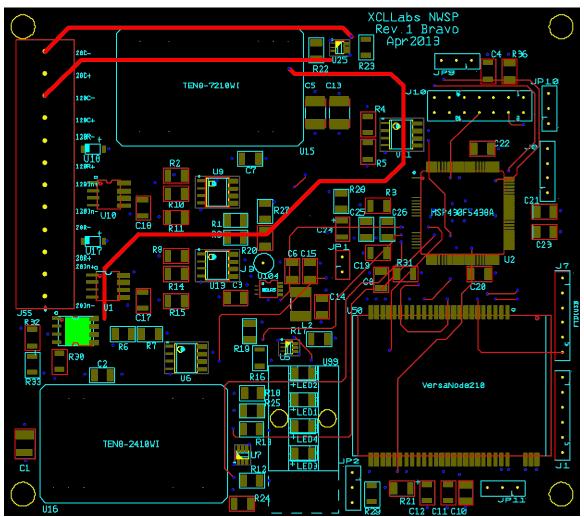

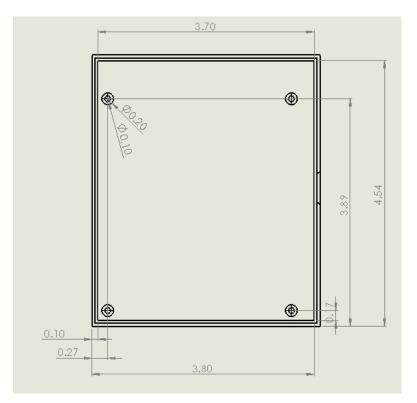

# **6.3 PCB Layout**

The final PCB layout for NWSP is referred to as the Bravo Board Layout. The NWSP's PCB measures 3.88" by 3.41" as a four layer board. The overall thickness of the board measures 62 mils. All trace widths on the Bravo Board measure 10 mils with the exception of power and ground. The power traces on the Bravo Board measure at least 25 mils, while any ground traces measure at least 30 mils. This increase in width is to accommodate the larger amount of current that may be drawn when the NWSP's VN210 is transmitting or the DC-DC converter is using more internal resources to step-down a specific voltage to 3.3V.

## 6.3.1 Copper Top

Figure 22 shows the top copper layer of the Bravo Board PCB for the NWSP. The top copper layer stores all the components of the device, as well as the majority of signal traces. The top copper layer was designed with specific groupings of components. On the left side is located the 12-pin terminal block, where the high voltage inputs access the board. The current sensors were located closest to the pins of the terminal block that would carry the voltage and current to be supplied to the end-device. The DC-DC converters and voltage detection resistor configurations were located closest with a secondary priority to the same pins considering these two applications do not carry high currents on their respective traces. The center of the board comprises of the circuitry related to current sensing and signal conditioning. The right side of the board pertains to the digital processing and wireless communications. To avoid interference potentially caused by the presence of high voltages and currents as expected on the left, the microcontroller specifically was located on the right-most side of the PCB, followed by the radio module.

Figure 22: PCB Copper Top

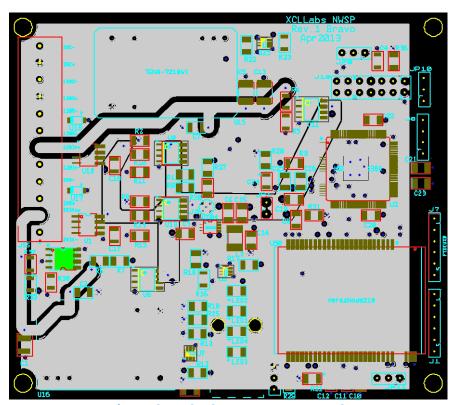

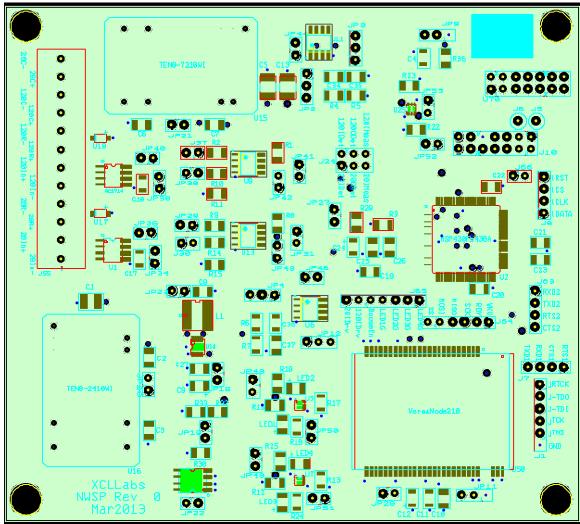

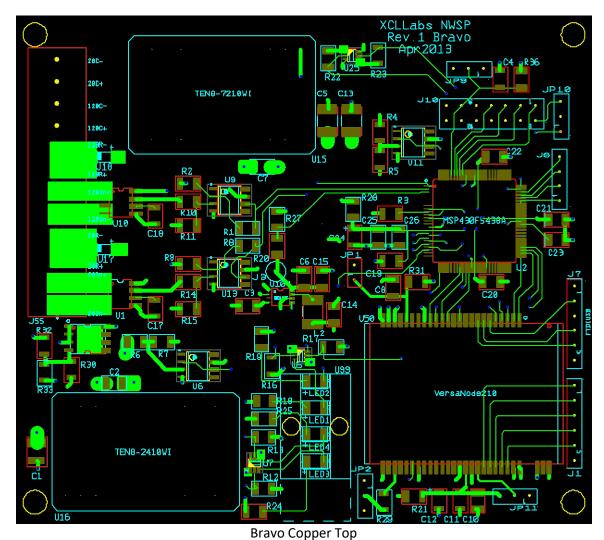

# 6.3.2 Copper Inner Layer 1

Figure 23 shows the copper inner layer 1 of the Bravo Board PCB for the NWSP. This layer is strictly reserved for the purpose of internal analog and digital ground. No power or signal traces are shared on this plane.

Figure 23: PCB Copper Inner Layer 1

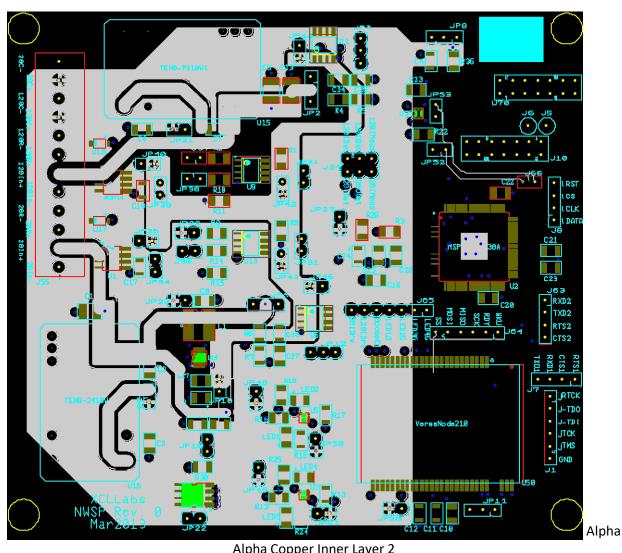

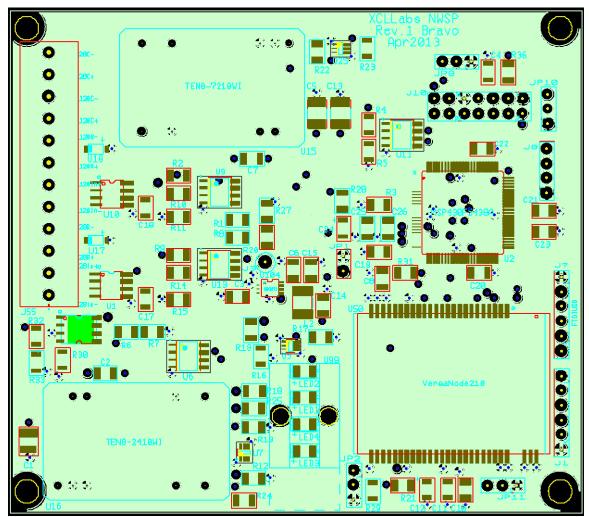

# 6.3.3 Copper Inner Layer 2

Figure 24 shows the copper inner layer 1 of the Bravo Board PCB for the NWSP. This layer is strictly reserved as a power plane. The majority of the layer is compensated by the 3.3V polygon. The second largest polygon is used for 5V applications. 28VDC and 120VDC are routed to their respective DC-DC converter and voltage detection resistor configuration. Due to the concern of 120VDC arcing to the adjacent 3.3V layer, a clearance of 50 mils has been provided. Likewise, for the 28VDC trace, a signal trace of 30 mils has been provided. Both 28VDC and 120VDC traces were designed to be as short as possible to avoid spanning underneath or near components and signal traces requiring high precision and minimal interference.

Figure 24: PCB Copper Inner Layer 2

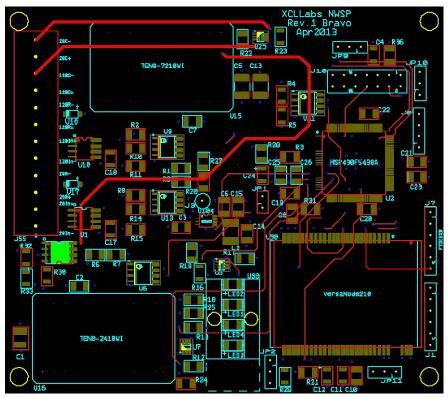

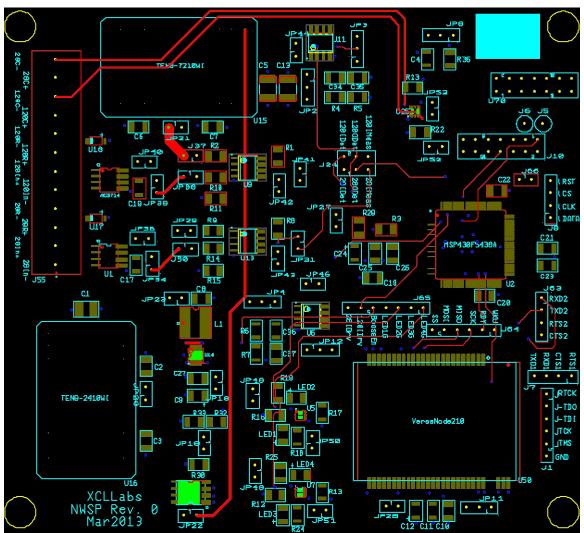

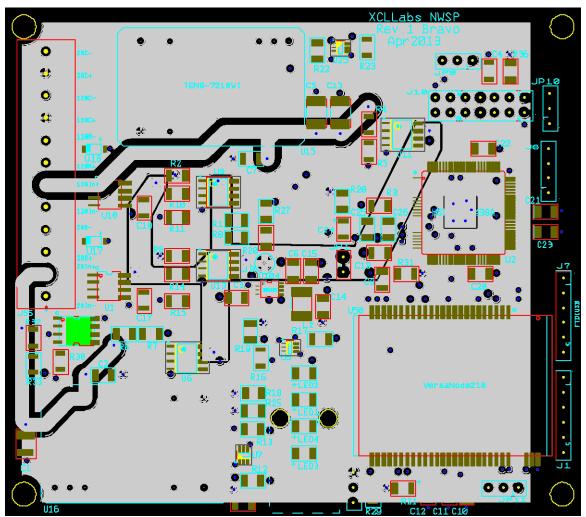

# **6.3.3 Copper Bottom Layer**

Figure 25 shows the copper bottom layer of the Bravo Board PCB for the NWSP. This layer has been used as the reserve layer for signal traces that would otherwise overlap on the top layer. Considering this layer is closer to the adjacent power plane layer, the signal traces that would usually directly route to their destination using the shortest path have been rerouted to avoid placement adjacent to high voltage traces.

**Figure 25: PCB Copper Bottom**

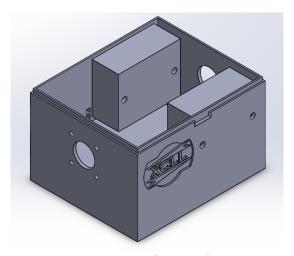

#### **6.4 Enclosure**

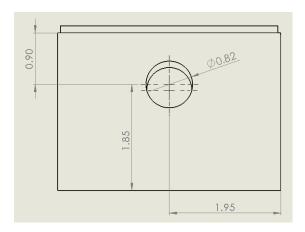

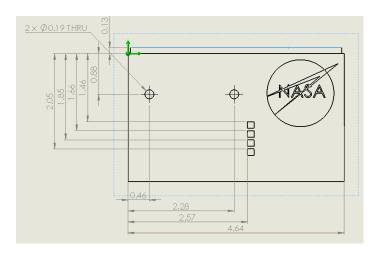

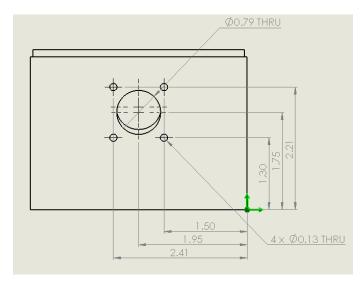

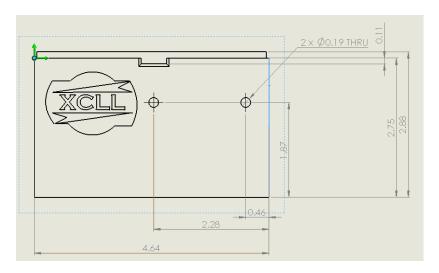

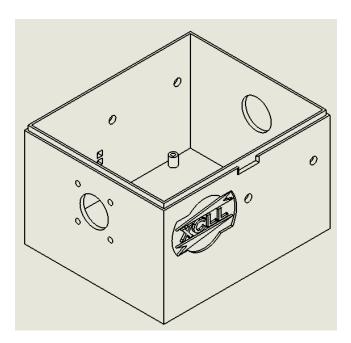

An enclosure was designed and created to house and protect the NWSP. The enclosure was designed in SolidWorks 2013 and printed using the uPrint SE rapid prototyping system. The printing medium is ABSplus plastic. The enclosure was meant to provide secure housing for the NWSP PCB and two relays. The enclosure should be as small as possible while providing enough distance between components to maintain a safe environment inside the enclosure. The PCB is secured to the enclosure using four quarter inch #4-40 ANSI screws. Figure 26 shows the enclosure mockup designed in SolidWorks 2013.

**Figure 26: Complete Enclosure**

The enclosure is 4.64x3.90x2.75 inches. The front of the enclosure has a hole 0.5 inches in diameter for the female panel mount connector. This connector is screwed in using four quarter inch #4-40 ANSI screw. On the opposite end, a hole 0.5 inches in diameter for the grommet which secures the pigtail to the back of the enclosure. Figure 27 shows the complete enclosure.

**Figure 27: Complete Enclosure**

The rectangular depression on the top of the enclosure is sized for label on which the MAC address of the VN210 radio can be written. A small rectangular depression on the side of the enclosure is designed to allow the user to remove the lid with ease.

#### 6.5 Connectors

A requirement for the NWSP is to use cannon-type circular connectors. The NWSP uses two connectors, a female SRCN2A16-7S socket and male SRCN6A16-7P plug. Figure 28 shows both connectors as viewed from the NWSP.

Figure 28: Input and Output Connectors of NWSP

#### 6.5.1 SCRN2A16-7S Socket

A female SCRN2A16-7S socket is found on the front of the NWSP. This is where the end device will plug into the NWSP. The SCRN2A16-7S is a box mount, cannon-type, circular socket. This socket can support a 10A max current draw at a 300VDC max input voltage.

#### 6.5.2 SCRN6A16-7P Plug

A male SCRN6A16-7S plug is found on a pig tail attached to the back of the NWSP. This is where the NWSP will plug into the DSH Mockup. The SCRN6A16-7P is a cable mount, cannon-type, circular plug. This plug can support a 10A max current draw at a 300VDC max input voltage.

#### 6.6 Cost Data

To develop a fully functioning prototype, XCLL developed two revisions of the NWSP. The cost associated with the NWSP is divided into each revision.

#### 6.6.1 Alpha NWSP

The alpha revision of the NWSP was XCLL's first attempt at designing a fully functioning NWSP. XCLL purchased two alpha revision boards. Everything worked with the exception of the boost converter and VN210. The boost converter was in a very small package, which proved difficult to solder and test. The VN210 did not have the proper pins brought to the MSP430l, and the

pins needed to provision the radio and flash firmware were not brought to headers. The costs associated with the alpha revision are in Table 1.

**Table 1: Alpha Board Costs**

| Date      | Vendor           | Cost |

|-----------|------------------|------|

| 3/5/2013  | Mouser           |      |

| 3/5/2013  | AdvancedCircuits |      |

| 3/25/2013 | Digikey          |      |

|           | Total            |      |

#### 6.6.2 Bravo NWSP

The bravo revision of the NWSP is the last revision made by XCLL. XCLL purchased five boards. Everything worked as expected with the exception of two pins from the MSP430 routed to the wrong pins on the VN210. XCLL was able to correct the board by cutting the traces and using 30 AWG blue wire to swap the pins. The bravo board was smaller than the alpha board. The costs associated with the final bravo revision can be found in Table 2.

**Table 2: Bravo Board Costs**

| Table 2: Blave Board Cooks |                  |      |  |

|----------------------------|------------------|------|--|

| Date                       | Vendor           | Cost |  |

| 4/9/2013                   | AdvancedCircuits |      |  |

| 4/9/2013                   | Mouser           |      |  |

| 4/9/2013                   | Powergate        |      |  |

| 4/9/2013                   | Digikey          |      |  |

| 4/17/2013                  | Mouser           |      |  |

| 4/23/2013                  | Mouser           |      |  |

| 4/24/2013                  | Digikey          |      |  |

|                            | Total            |      |  |

#### 6.6.3 Final Costs

The final cost to produce one NWSP is \$. When quantities of 100 are ordered, the final cost is \$ for all 100 or \$ for one. This includes the cost of outsourcing enclosures, professional population, and putting together the final NWSP. For a complete listing of prices associated with the NWSP, please refer to the Bill of Material found in Appendix B.

# 7.0 Software Design

# 7.1 Implementation Strategy

The embedded code on the NWSP was an addition of plug capabilities to software provided by NASA. The software operates on an interrupt with polling solution based mainly around the Nivis VN210 radio communications. There are three states of communications between the MSP40 and the VN210: initialization, data transmission, and idle. The initialization state takes place on radio reset and initial startup. It provides the initial conditions of the platform. Once the initialization has been completed, transmission between the NWSP unit and the MCU will begin. After a packet has been received from the VN210 radio, the MSP430 will interpret the communications and transmit the appropriate response. The NWSP will transmit the settings and status of the plug to the MCU to be interpreted and displayed by the LabVIEW GUI.

During the idle communications state between the MSP430 and the VN210, the NWSP will measure current, identify the state of the relays, voltage presence, and current status. The data is transmitted from the MSP430 to the VN210 when a timer sets an interrupt and the "appflag" is raised to 1. This flag notifies when the MSP430 should send data. This is used to define the time between each update and is configurable by the user through the GSAP client. The NWSP will transmit relay conditions (open/closed), measured current, voltage presence, user defined threshold current, and current status (under/over threshold current) using a polling method.

While the MSP430 is not in a low power mode, all fields are constantly updated. If there are no impending communications from the VN210 and the appflag has not been raised, the MSP430 will enter a low power mode to reduce power consumption. The MSP430 will stay in this mode until the VN210 requests communications or the interrupt timer fires.

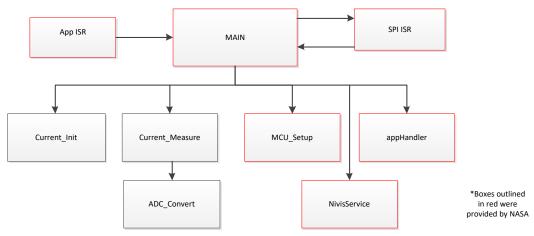

# 7.2 Hierarchy Chart

A hierarchy chart is used to aide in software planning and shows the calling hierarchy of each function. Figure 29 shows the Hierarchy Chart for the NWSP embedded software.

Figure 29: Hierarchy Chart

Boxes outlined in red were provided in the ISA100ThroughputTest program. Functions created for the NWSP include Current\_Init, Current\_Measure, ADC\_Convert, Parse\_Message, and Toggle\_Relay. The Parse\_Message and Toggle\_Relay functions interact through the SPI interrupt service routine (ISR) while the Current\_Measure function is called on each iteration of the main loop.

#### 7.2.1 Current\_Init

The Current\_Init function initializes the ADC pins and measurements used to measure the current. The ADC channels are configured for a sequence of consecutive measurements. This means when the measurements are triggered, the channels will be measured in a sequence until the end channel is completed.

# 7.2.2 Current\_Measure

Current\_Measure has an input of the NWSP message buffer. The ADC channels are measured 512 times, then averaged. An offset is computed by measuring a 2.5v line and subtracting a measured value from the ideal 2.5v ADC value. This offset provides the base number to be subtracted. A static number is subtracted from the resulting offset value to increase accuracy. After the offset has been applied, the new ADC value is sent to the ADC\_Convert function which computes the current equivalent. After the ADC value has been converted, the 120v or 28v current value is selected based on the active relay and stored in the message buffer.

# 7.2.3 ADC\_Convert

The ADC\_Convert function uses the ADC value found in the Current\_Measure function and applies a simple equation to convert the ADC value to the current equivalent. Current\_Measure passes the ADC value to ADC\_Convert in the form of a pointer. This allows the equation to be applied to the value at the address directly.

### 7.2.4 Parse\_Message

The Parse\_Message function is called after the SPI interrupt completes. The received message is passed to the function and each byte is interpreted and the commands are applied to the NWSP.

# 7.2.5 Toggle Relay

The Toggle\_Relay function takes the third byte of the message as an input and turns on or off the specified relay. A hex 0x01 activates the 28v relay and deactivates the 120v relay, a hex 0x02 deactivates the 28v relay and activates the 120v relay. Any other value will deactivate both relays.

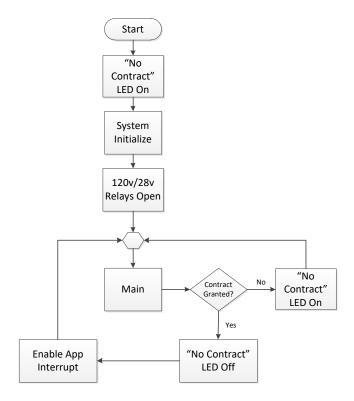

# 7.3 Flow Diagrams

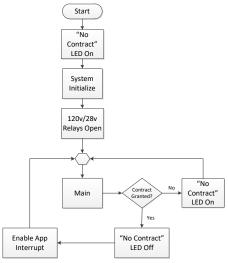

# 7.3.1 High Level Diagram

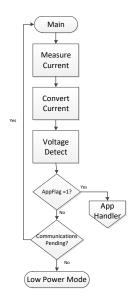

Flow diagrams are used to plan the logical flow of the software. Flow diagrams allow the programmer to see how each aspect of the program interacts with each other. Figure 30 shows the flow diagram for the high level functionality.

Figure 30: High Level Flow Diagram

The high level flow diagram shows the initialization and high level loop of the program. The main function checks the status of the contract and turns on and off an LED to indicate the contract status. Once a contract has been granted, the application interrupt is enabled. The application interrupt is a timer interrupt which tells the program when data from the MSP430 should be sent to the VN210.

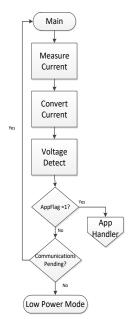

# 7.3.2 Main Loop Diagram

The main loop executes after initialization and is the center of the program. Figure 31 shows the flow diagram for the main loop.

Figure 31: Main Loop Diagram

The main loop is where current measurements are made, the current is converted from an ADC measurement to the current equivalent, the voltage is detected, and the data is sent to the VN210 if the application flag is high. If there are no pending communications, meaning the application flag is not high and the VN210 has not signaled pending SPI communications, the MSP430 will enter into a low power mode. If the processer is in a low power mode, interrupts will return the processer to the normal mode of operation.

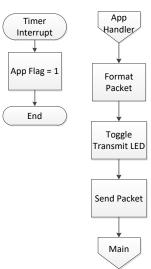

# 7.3.3 Application Flow Diagram

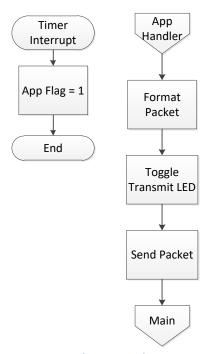

The application flow diagram shows how the message is created and triggered to be sent. Figure 32 shows the application flow diagram.

**Figure 32: Application Flow Diagram**

The timer interrupt is fired when the internal counter of the MSP430 reaches the user defined value. The interrupt sets the application flag high which signals the processer it is time to send the data packet to the MCU. The application handler then moves all information from the temporary NWSPmsg buffer to the outgoing message buffer. An LED is then toggled to show active communications and the message is sent from the MSP430 to the VN210 via SPI.

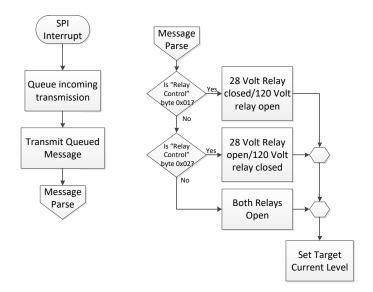

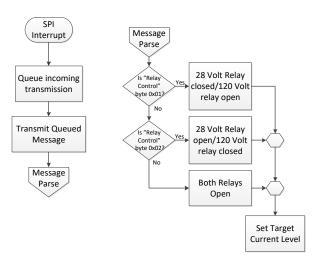

# 7.3.4 Message Parse Flow Diagram

In order to dynamically configure the NWSP, the smart plug must be able to receive commands from the MCU. It does this by relaying information from the VN210 to the MSP430 via SPI. Figure 33 shows the flow diagram for the message parsing algorithm.

Figure 33: Message Parse Flow Diagram

The MSP430 handles communications using an SPI interrupt which stores incoming information on a queue while sending information. If the queued information is a command for the NWSP, the software will enter into the message parse function. In this function, the relays are configured according to the user input and the target current level is stored into a global variable.

# 7.4 Code Description

When power is first provided to the NWSP, the microcontroller begins initialization. All digital input/output pins and communications ports are configured and the relays are initialized open. After the initialization, the software enters into a loop which executes continuously. This loop measures current, detects the input voltage sends requests and responses to the VN210 radio.

#### 7.4.1 Current Measurement

The main function of the NWSP is to measure current on either the 28v or 120v line. Both lines are measured during each measurement cycle and the channel is chosen based on the connected relay. This was accomplished using a sequence of measurements for the 28v channel, 120v channel, and ADC offset channel.

The boost converter will ideally provide exactly 5V; however, there is a small offset which impacts the current sensors' voltage range. To compensate, the ADC Offset channel utilizes a voltage divider to divide the boost convert's 5v output by 2.5V. This voltage will be input to the ADC channel, which is referencing a 3.3 volt line. Measuring this line allows dynamic calibration during measurement. The ideal 2.5v ADC measurement is subtracted by the measured value to find the offset which is subsequently subtracted from the 28v and 120v channels. To increase the accuracy, a second offset is added to the measured offset.

Each channel is measured 512 times in order to increase accuracy and decrease the impact of short spikes in current draw. Once the measurements have been made, the offset is subtracted from each channel and the resultant is compared to the current threshold limit. After this comparison has been made, the ADC value of the 28v and 120v line are passed to the ADC convert function.

#### 7.4.2 ADC Conversion

A simple linear equation was used to convert the measured ADC value to its respective current value. The input voltage from the current sensor signal conditioning is between .2v and 3.2v, which is offset from the referenced 0v and 3.3v. To compensate, the offset will be subtracted from the converted ADC value. The conversion equation looks as follows: (((ADC\_VALUE\*10)/4096)-(248/4096\*10))\*1.1. This equation converts the ADC value and the Offset to the respective current values and subtracts them to compensate for the offset. This equation makes it possible to accurately convert between the ADC values measured from the current sensors to the respective current measurement.

# 7.5 Graphic User Interface

The Master Control Unit uses a LabVIEW Graphic User Interface running on a Microsoft Windows Operating System. The GSAP client interacts with the VR900 gateway through TCP/IP. If a wireless router is used, IEEE 802.3 or 802.11 can be used. The LabVIEW GUI reads data from a log file generated by the GSAP client. The GUI will generate the byte-stream that user will enter into the transmit window of the GSAP client to control the plug.

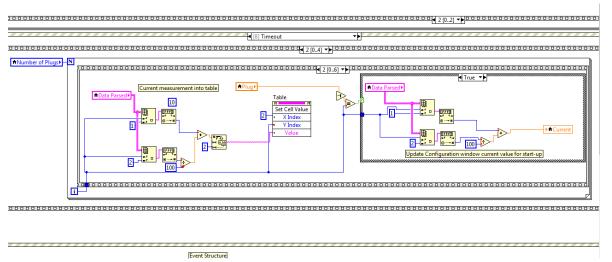

## 7.5.1 Receive Data

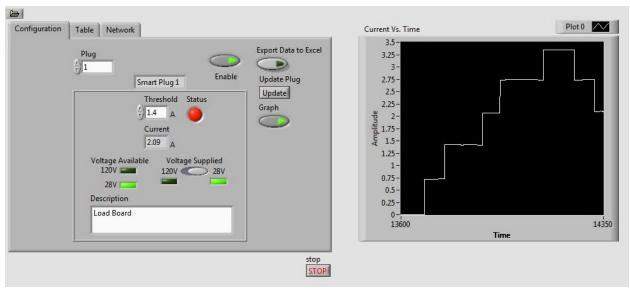

Most of the work done by the GUI involves reading the log file from the GSAP client. The GSAP client will append the last update to the end of the log file. As seen in Figure 34, the receive function of the GUI is completed by using the timeout case of an event structure. The GUI will open the log file and feed in fifteen lines from the bottom of the log file. The GUI will flip the array, so that the most recent data is on top. Next the array is searched using the MAC Addresses in the Networking table. The parsed data is then placed in an array. The GUI will interpret the parsed data and populate the Table and Configuration tabs of the GUI.

Figure 34: LabVIEW GUI Receive Function

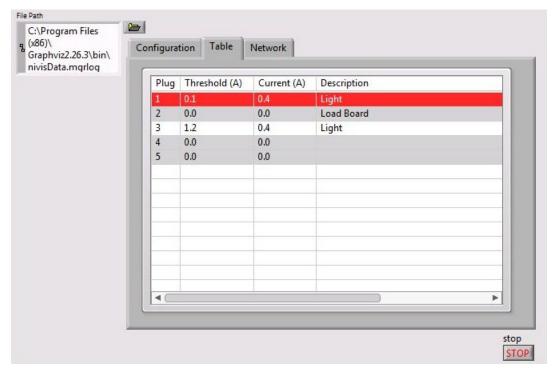

The Table tab will show all the plugs that have been added to the MCU. Figure 35 shows the table view. The table view shows every plug, each plug's current value, target current, and a description that the user can add to identify plugs. As seen in Figure 35 the table will highlight every plug that is in the over current state. These plugs will be highlighted red. If no relay is closed then the table will highlight the plug in gray. When the relay is closed and the plug is not in an over current state the plug will not be highlighted.

Figure 35: LabVIEW GUI Table View

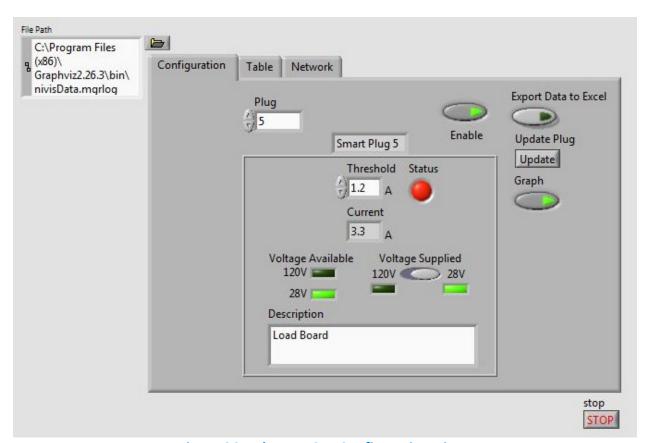

#### 7.5.2 Transmit Data

The GUI will read the settings in the Configuration tab. From these settings, it will inform the user of the byte-stream that needs to be keyed into the "Transmit Window" field of the Device Command tab in the GSAP client. The configuration tab can be seen in Figure 36. The Voltage Available LEDs will display which voltage is available at the input to the NWSP. The user must select enable and then the correct voltage to supply to the end device. The value entered into threshold will be converted into hex. Once the user hits the Update button, the GUI will generate the byte-stream. A dialog box will pop up, which informs the user of the byte-stream that needs to be entered.

Figure 36: LabVIEW GUI Configuration View

#### 7.5.3 Features

XCLL has added two features to the GUI. The first feature is graphing, which is displayed in Figure 37. Once the user has hit the Graph button, the GUI will display a real-time graph of the current being read by the plug selected in the Configuration tab. If the user hits the Graph button again, the graph will no longer be displayed. The second feature is the ability to export to Microsoft Excel. The data of the plug selected in the Configuration tab will be exported to a comma separated value file, which can be read by Excel.

Figure 37: LabVIEW GUI Graphing Feature

#### 7.6 Wireless Communication

The NWSP communicates to the MCU via the VN210 radio. The MSP430 communicates to the VN210 radio through four wire SPI communications. The VN210 is the master and provides the clock rate to the MSP430. The VN210 pulses the "Ready" line on the MSP430 to signal impending communications. The MSP430 responds with a short pulse on the "Wake Up" line to signal the VN210 the processor is ready for communications to proceed. An SPI interrupt handles the receipt and transmittal of data between the MSP430 and the VN210.

The NWSP sends data to the MCU once per second. A timer interrupt is used to maintain this frequency and enter a low power state when communications is not necessary. The timer interrupt fires when an internal counter of the MSP430 reaches a user defined value. This value can be configured by the user using the GSAP interface, but is initialized to 1 Hz. When the interrupt fires, the application flag is set to 1. The main loop polls the application flag. When the application flag is set to 1, the application handler is called and a data packet is sent to the VN210 to be wirelessly transmitted to the MCU.

# 8.0 Testing

#### 8.1 Test Matrix

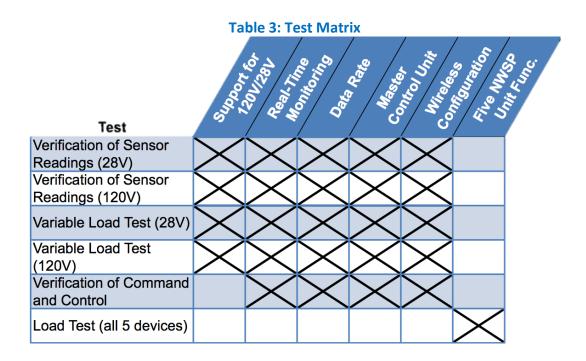

XCLL has created a Test Matrix (Table 3) to ensure that crucial tests are performed on the NWSP in order to validate all of its functionality. The row on the top of the Test Matrix (x-axis) describes all the functional requirements that the NWSP must implement as a final product. The column on the left (y-axis) contains all the test cases to be performed on the NWSP in order to validate its functionality. We marked with an "X" the test cases that validate one or more of the functional requirements.

# 8.2 Test Plan

# 8.2.1 Verification of Sensor Readings (28V)