# NASA/TM-20250008583/Volume 1 NESC-RP-23-01873

# Cold Electronics for Lunar Missions

George L. Jackson/NESC Goddard Space Flight Center, Greenbelt, Maryland

Yuan Chen Langley Research Center, Hampton, Virginia

Raphael R. Some Jet Propulsion Laboratory, Pasadena, California

Richard C Oeftering Glenn Research Center, Cleveland, Ohio

Mohammad M. Mojarradi, Erik J. Brandon, Linda Y. Del Castillo, and Jean Yang-Scharlotta Jet Propulsion Laboratory, Pasadena, California

## NASA STI Program Report Series

Since its founding, NASA has been dedicated to the advancement of aeronautics and space science. The NASA scientific and technical information (STI) program plays a key part in helping NASA maintain this important role.

The NASA STI program operates under the auspices of the Agency Chief Information Officer. It collects, organizes, provides for archiving, and disseminates NASA's STI. The NASA STI program provides access to the NTRS Registered and its public interface, the NASA Technical Reports Server, thus providing one of the largest collections of aeronautical and space science STI in the world. Results are published in both non-NASA channels and by NASA in the NASA STI Report Series, which includes the following report types:

- TECHNICAL PUBLICATION. Reports of completed research or a major significant phase of research that present the results of NASA Programs and include extensive data or theoretical analysis. Includes compilations of significant scientific and technical data and information deemed to be of continuing reference value. NASA counterpart of peer-reviewed formal professional papers but has less stringent limitations on manuscript length and extent of graphic presentations.

- TECHNICAL MEMORANDUM.

Scientific and technical findings that are

preliminary or of specialized interest,

e.g., quick release reports, working

papers, and bibliographies that contain minimal

annotation. Does not contain extensive analysis.

- CONTRACTOR REPORT. Scientific and technical findings by NASA-sponsored contractors and grantees.

- CONFERENCE PUBLICATION.

Collected papers from scientific and technical conferences, symposia, seminars, or other meetings sponsored or co-sponsored by NASA.

- SPECIAL PUBLICATION. Scientific, technical, or historical information from NASA programs, projects, and missions, often concerned with subjects having substantial public interest.

- TECHNICAL TRANSLATION.

English-language translations of foreign scientific and technical material pertinent to NASA's mission.

Specialized services also include organizing and publishing research results, distributing specialized research announcements and feeds, providing information desk and personal search support, and enabling data exchange services.

For more information about the NASA STI program, see the following:

- Access the NASA STI program home page at http://www.sti.nasa.gov

- Help desk contact information:

https://www.sti.nasa.gov/sti-contact-form/ and select the "General" help request type.

# NASA/TM-20250008583/Volume 1 NESC-RP-23-01873

# Cold Electronics for Lunar Missions

George L. Jackson/NESC Goddard Space Flight Center, Greenbelt, Maryland

Yuan Chen Langley Research Center, Hampton, Virginia

Raphael R. Some Jet Propulsion Laboratory, Pasadena, California

Richard C Oeftering Glenn Research Center, Cleveland, Ohio

Mohammad M. Mojarradi, Erik J. Brandon, Linda Y. Del Castillo, and Jean Yang-Scharlotta Jet Propulsion Laboratory, Pasadena, California

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23681-2199

## Acknowledgments

The NESC team would like to thank our consultants listed above and numerous people we have talked to from NASA, industry, academia, and other government labs and agencies during this assessment. The team would like to extend our thanks to Steve Rickman, Will Grier, William Birmingham, and Lisa Erickson at NASA as well as Milena Graziano, Sean Young, and Jacob Gehrett at the Applied Physics Laboratory for many discussions on thermal analysis and modeling and lunar environments. The team also would like to thank the following peer reviewers: Jeffery Farmer, Jim O'Donnell, Jeremiah McNatt, Steve Rickman, Wesley Powell, Joel Sills, Nicholas Uguccini, Peter Majewicz, Tim Barth, William Bluethmann, and Carolyn Mercer.

The use of trademarks or names of manufacturers in the report is for accurate reporting and does not constitute an official endorsement, either expressed or implied, of such products or manufacturers by the National Aeronautics and Space Administration.

Available from:

NASA STI Program / Mail Stop 050 NASA Langley Research Center Hampton, VA 23681-2199

# NASA Engineering and Safety Center Technical Assessment Report

**Cold Electronics for Lunar Missions**

TI-23-01873

NESC Lead, George Jackson Technical Co-Lead, Yuan Chen Technical Co-Lead, Raphael Some

July 17, 2025

# **Report Approval and Revision History**

NOTE: This document was approved at the July 29, 2025, NRB.

| Approved: | Timmy Wilson | Digitally signed by Timmy Wilson<br>Date: 2025.08.15 13:30:20 -04'00' |

|-----------|--------------|-----------------------------------------------------------------------|

|           | NESC         | Director                                                              |

| Version | Description of Revision | Office of Primary<br>Responsibility | Effective Date |

|---------|-------------------------|-------------------------------------|----------------|

| 1.0     | Initial Release         | George Jackson,                     | 7/17/25        |

|         |                         | Avionics Technical                  |                |

|         |                         | Fellow, GSFC                        |                |

# **Table of Contents**

| 1.0   | Notification and Authorization                                                           | 6  |

|-------|------------------------------------------------------------------------------------------|----|

| 2.0   | Signatures                                                                               | 7  |

| 3.0 T | eam Members                                                                              | 8  |

| Ackn  | owledgements                                                                             | 8  |

| 4.0   | Executive Summary                                                                        |    |

| 5.0   | Assessment Plan                                                                          |    |

| 6.0   | Problem Description and Background                                                       |    |

| 7.0   | State of Cold Electronics Technologies and Gap Analysis                                  |    |

| 7.0   | 7.1 Scope of Assessment and Key Definitions                                              |    |

|       | 7.1 Scope of Assessment and Key Definitions  7.2 Target Thermal Environments             |    |

|       | 7.2.1 Thermal Environment Experienced by the Electronics                                 |    |

|       | 7.2.2 Thermal Cycles                                                                     |    |

|       | 7.3 Avionic Architectures for Cold Environment                                           |    |

|       | 7.3.1 State of the Art                                                                   |    |

|       | 7.3.2 Gap Analyses                                                                       |    |

|       | 7.4 COTS Cold Electronics.                                                               |    |

|       | 7.4.1 State of the Art or Current Practice                                               |    |

|       | 7.4.2 Gap Analyses                                                                       |    |

|       | 7.5 Custom Cold Electronics                                                              |    |

|       | 7.5.1 State of the Art                                                                   |    |

|       | 7.5.2 Gap Analyses                                                                       |    |

|       | 7.6 Passives for Cold Environment                                                        |    |

|       | 7.6.1 State of the Art                                                                   |    |

|       | 7.6.2 Gap analyses                                                                       |    |

|       | 7.7 Electronic Packaging for Cold Environment                                            |    |

|       | 7.7.1 State of the Art                                                                   |    |

|       | 7.7.2 Gap Analyses                                                                       |    |

|       | 7.8 Power Systems and Energy Storage and Electronics for Cold Environment                |    |

|       | 7.8.1 State of the Art of Power Systems                                                  |    |

|       | 7.8.2 Cold Electronics: Energy Storage                                                   |    |

|       | 7.9 NESC Guidance on Cold Electronics Qualification                                      |    |

|       | 7.9.1 No Existing Qualification Standard for Cold Electronics                            | 47 |

|       | 7.9.2 NESC Guidance on Cold Electronics Qualification                                    | 47 |

|       | 7.10 Discussion of a Phased Evolutionary Development, Potential High-Value Technologies, |    |

|       | and Technology Demonstration/Infusion Examples                                           |    |

|       | 7.10.1 Phased Evolutionary Approach                                                      |    |

|       | 7.10.2 Potential High Value Developments                                                 |    |

|       | 7.10.3 Infusion Examples                                                                 |    |

|       | 7.10.4 Example Hybrid Rover Architecture                                                 |    |

|       | 7.11 Technology Interchange Meeting                                                      | 59 |

| 8.0   | Findings, Observations, and NESC Recommendations                                         | 61 |

|       | 8.1 Findings                                                                             | 61 |

|       | 8.2 Observations                                                                         |    |

|       | 8.3 NESC Recommendations                                                                 | 64 |

| 9.0  | Alternate Technical Opinion(s)                                                | 65 |

|------|-------------------------------------------------------------------------------|----|

| 10.0 | Other Deliverables                                                            | 65 |

| 11.0 | Recommendations for the NASA Lessons Learned Database                         | 65 |

| 12.0 | Recommendations for NASA Standards, Specifications, Handbooks, and Procedures | 65 |

| 13.0 | Definition of Terms                                                           | 65 |

| 14.0 | Acronyms                                                                      | 66 |

|      | References                                                                    |    |

# **List of Figures**

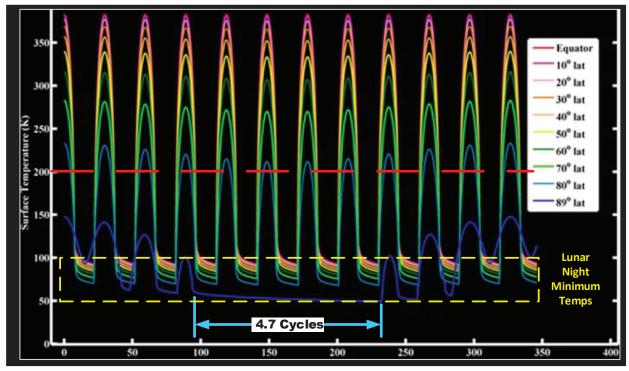

| Figure 7.2-1. Lunar Reconnaissance Orbiter DIVINER Surface Temperature Data                 | 15 |

|---------------------------------------------------------------------------------------------|----|

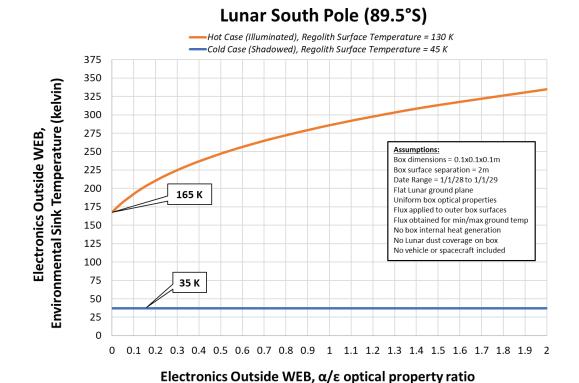

| Figure 7.2-2. An Example of Thermal Environment for a Specific Platform Configuration       | 16 |

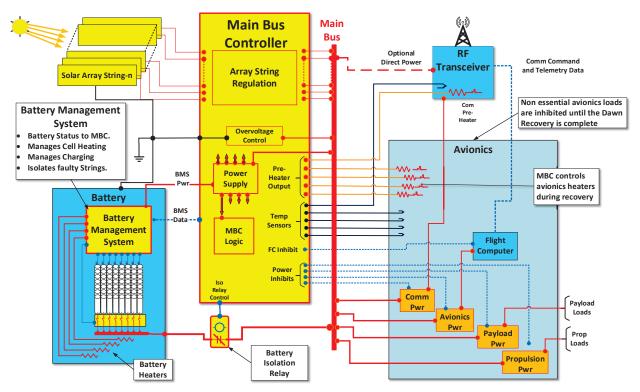

| Figure 7.3-1. Lunar Power Hibernation Architecture employing Cold Electronics without a WEB | 20 |

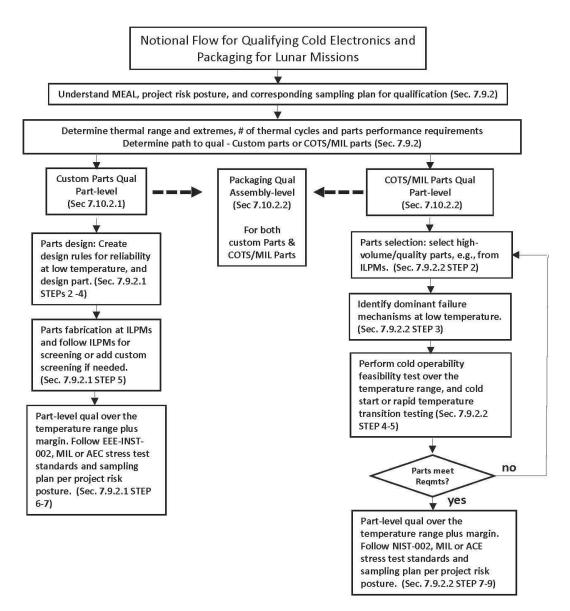

| Figure 7.9-1. Top-Level NESC Guidance on Cold Electronics Qualification.                    | 49 |

|                                                                                             |    |

| List of Tables                                                                              |    |

| Table 7.1-1 Typical Specified Temperature Range                                             | 11 |

| Table 7.5-1. Custom Electronics Development Summary                                         | 28 |

| Table 7.6-1. Performance of Various Types of Resistors at Low Temperatures                  | 31 |

| Table 7.6-2. Relative Change in Capacitor Properties from Room to Cryogenic Temperatures    | 32 |

| Table 7.6-3 Comparison of Core Materials at Cryogenic Temperature with Room Temperatures    | 33 |

| Table 7.7.2-1. State of Electronic Package Technology                                       | 38 |

# **Technical Assessment Report**

## 1.0 Notification and Authorization

Mr. Kevin Somervill, Deputy Program Director for Technology Maturation at NASA Space Technology Mission Directorate (STMD), requested an independent assessment on the state of the cold electronics technologies and the gaps for applications and challenges under lunar environments, and provide NESC recommendations for cold electronics selection, evaluation, qualification and screening for lunar missions and forward work.

Key dates in the assessment life cycle are listed below.

| Request Submitted                            | May 4, 2023        |

|----------------------------------------------|--------------------|

| Initial Evaluation Approved                  | June 29, 2023      |

| Assessment Plan Approved                     | September 21, 2023 |

| Team Kickoff Meeting                         | October 16, 2024   |

| Final Report Delivery and Stakeholder Update | July 17, 2025      |

In addition to Mr. Somervill, the stakeholders for this assessment include:

Wesley Powell, NASA STMD Principal Technologist for Avionics; Carolyn Mercer, Chief Technologist of NASA Science Mission Directorate (SMD); Florence Tan, Deputy Chief Technologist of NASA SMD; Dr. Peter Majewicz NASA Electronic Parts Program (NEPP); Susana Douglas, NASA Agency Electrical, Electronic, and Electromechanical (EEE) Parts Manager; and Program or projects needed to survive and operate under lunar environments.

#### 2.0 **Signatures**

Submitted by: NESC Lead

George Jackson

Digitally signed by George Jackson Date: 2025.08.14 10:00:33 -04'00'

Mr. George L. Jackson

Significant Contributors:

Yuan Chen Date: 2025.08.01 14:27:13

Dr. Yuan Chen

**MOHAMMAD**

Digitally signed by MOHAMMAD MOJARRADI (affiliate) MOJARRADI (affiliate) Date: 2025.08.06 11:29:03 -07'00'

Dr. Mohammad M. Mojarradi

(affiliate)

ERIK BRANDON Digitally signed by ERIK BRANDON (affiliate)

Date: 2025.08.09 12:23:02 -07'00'

Dr. Erik J. Brandon

Jean Yang-

Digitally signed by Jean Yang-Scharlotta (affiliate) Scharlotta (affiliate) Date: 2025.08.13 15:32:35 -07'00'

Dr. Jean Yang-Scharlotta

**RAPHAEL**

Digitally signed by RAPHAEL SOME (affiliate) Date: 2025.08.01 11:55:29

SOME (affiliate)

-07'00'

Mr. Raphael R. Some

Richard **Oeftering**  Digitally signed by Richard Oeftering Date: 2025.08.14 09:17:44 -04'00'

Mr. Richard C. Oeftering

LINDA DEL

Digitally signed by LINDA DEL CASTILLO (affiliate) CASTILLO (affiliate) Date: 2025.08.14 06:47:49

Dr. Linda Y. Del Castillo

Signatories declare the findings, observations, and NESC recommendations compiled in the report are factually based from data extracted from program/project documents, contractor reports, and open literature, and/or generated from independently conducted tests, analyses, and inspections.

### 3.0 Team Members

| N.T.                       | n                                           |                                  |

|----------------------------|---------------------------------------------|----------------------------------|

| Name                       | Discipline                                  | Organization/Host Center         |

| Core Team                  | A TROOP 1                                   | NEGG/GGEG                        |

| George Jackson             | NESC Lead                                   | NESC/GSFC                        |

| Yuan Chen                  | Technical Co-Lead, Electronics, Cryo        | NESC/LaRC                        |

| Raphael Some               | Technical Co-Lead, Electronics, Cryo        | JPL                              |

| Mohammad Mojarradi         | Electronics, Cryo                           | JPL                              |

| Rich Oeftering             | Power Architecture, Cryo                    | GRC                              |

| Erik Brandon               | Power, Energy Storage                       | JPL                              |

| Linda Del Castillo         | Packaging Materials, Cryo                   | JPL                              |

| Jean Yang-Scharlotta       | Electronic Component, Cryo                  | JPL                              |

| Consultants                |                                             |                                  |

| John Cressler              | Electronics - SiGe, Analogue, Digital, Cryo | Georgia Tech                     |

| Ben Blalock                | CMOS, Analog, Digital, Cryo                 | University of Tennessee          |

| Wayne Johnson              | Electronics - Packaging, Cryo               | Auburn University                |

| Zheyu Zhang                | GaN, Power, Cryo                            | Rensselaer Polytechnic Institute |

| Kristen Boomer             | Electrical Power Systems                    | GRC                              |

| Shri Agarwal               | NEPAG, Industry Study                       | JPL                              |

| Reza Ghaffarian            | Packaging                                   | JPL                              |

| Basil Jeffers              | JWST Lead Parts Engineer                    | GSFC/SSA                         |

| Peter Majewicz             | Reliability and Quality Assurance           | GSFC                             |

| Susana Douglas             | Electrical Systems                          | GSFC                             |

| Robert Hodson              | NESC Avionics Consultant                    | NESC/LaRC                        |

| <b>Business Management</b> |                                             |                                  |

| Becki Hendricks            | Program Analyst                             | MTSO/LaRC                        |

| <b>Assessment Support</b>  |                                             |                                  |

| Anissa Proctor             | Project Coordinator                         | Barrios/LaRC                     |

| Linda Burgess              | Planning and Control Analyst                | AMA/LaRC                         |

| Emily Anthony              | Technical Editor                            | AS&M/LaRC                        |

# Acknowledgements

The NESC team would like to thank our consultants listed above and numerous people we have talked to from NASA, industry, academia, and other government labs and agencies during this assessment. The team would like to extend our thanks to Steve Rickman, Will Grier, William Birmingham, and Lisa Erickson at NASA as well as Milena Graziano, Sean Young, and Jacob Gehrett at the Applied Physics Laboratory for many discussions on thermal analysis and modeling and lunar environments. The team also would like to thank the following peer reviewers: Jeffery Farmer, Jim O'Donnell, Jeremiah McNatt, Steve Rickman, Wesley Powell, Joel Sills, Nicholas Uguccini, Peter Majewicz, Tim Barth, William Bluethmann, and Carolyn Mercer.

# 4.0 Executive Summary

NASA's goal of developing crewed and robotic lunar installations has created a need for cold capable electronic parts, subsystems, and systems that can operate in the lunar thermal environment (typically -233 degrees Celsius (°C) or below to +125 °C ambient). This assessment was commissioned to evaluate the state of cold capable electronic and packaging technologies, perform a gap analysis against the continuous use of these electronics with minimal or no thermal management on the lunar surface, provide NASA Engineering and Safety Center (NESC) guidance on the qualification of cold electronics, and to give NESC recommendations for the development and utilization of cold capable electronics. The assessment did not focus on the lunar radiation environment.

## Key recommendations for the development and utilization of cold capable electronics:

The current architectural approach for avionics required to operate in extremely cold and wide environments (e.g., Mars or Deep Space) is to place the electronics in a warm electronics box (WEB) and cable out to actuators and sensors that are custom designs built for these extreme environments [F-4]. The NESC team believes that it would be highly beneficial and, in some cases enabling, to lunar surface missions if specific electronics assemblies could be located outside the WEB. However, no cold capable electronics architectures that are generally applicable to the lunar surface environment have been implemented or even studied to the degree necessary to initiate the detailed design of such an architecture [F-5]. Therefore, the NESC team concluded that a practical first step to implementing a cold capable avionics architecture is to implement a hybrid system with a WEB and selective technologies and subsystems outside of the WEB. The NESC team recommends that Science Mission Directorate (SMD)/Space Technology Mission Directorate (STMD) implement an evolutionary strategy to develop a cold capable electronics ecosystem that supports hybrid and hibernation avionics architectures (R-3). Additionally, the team recommends that STMD/SMD develop cold electronic elements for representative mission environments and plan for mission infusion opportunities (R-4). A phased evolutionary approach with identified development of high value technologies and demonstration/infusion examples are described and outlined in Section 7.10.

#### Qualification guidance on cold electronics and packaging:

No existing standards support the qualification of the electronics and packaging for the lunar environment temperature range of -233 °C to +125 °C (40 to 398 Kelvin (K)). Actual worst-case temperatures, depending on specific mission location, platform configuration, electronics location and orientation within the platform, and mission operations, could be significantly lower and will need to be identified by the project. Guidance on qualification of the cold custom electronics, commercial off-the-shelf (COTS)/military (MIL) electronics, and packaging were developed and are summarized in Section 7.9 (R-2). A given project will need to apply the appropriate guidance based on their Mission, Environment, Application, and Lifetime (MEAL) and risk posture. There is an additional recommendation for NASA Electronic Parts Program (NEPP) to develop NASA qualification standards for cold electronics and packaging, perform cold electronics testing/characterization, develop packaging guidelines, and to host a cold electronics database (R-5).

The intended audience of this report are NASA personnel and commercial practitioners who develop parts, subsystems, and systems for lunar surface missions.

#### 5.0 Assessment Plan

The NESC team performed the following tasks, which were in the initial request.

- Captured the state of the art in NASA, industry, academia, and other communities in cold capable electronics and their applications and challenges for lunar environments.

- Described the current or best practices in selecting and qualifying cold electronics and identified gaps in technology selection and evaluation processes for lunar missions.

- Provided NESC recommendations for cold electronics selection, evaluation, qualification, and screening for lunar missions, as well as forward work.

## 6.0 Problem Description and Background

NASA's goal of developing long term crewed and robotic lunar installations has created a need for electronics that can operate in the lunar thermal environment. Though some of the electronics in question will be housed within a thermally controlled environment (e.g., in a lunar habitat or a robotic platform WEB), it would be either enabling or advantageous to many systems if their electronics could withstand the lunar environment without extensive thermal mitigation. Previous work began developing and evaluating various electronics for the extreme temperatures found on the lunar, Europa/Icy Moons, and Mars surfaces. The NESC team was tasked to assess the state of the cold capable electronics and packaging technologies, perform a gap analysis of the continuous use of these electronics with minimal or no thermal management on the lunar surface, and provide recommendations and guidelines, to the extent possible, for utilization and development of cold capable electronics. The assessment was focused on the thermal aspects of the problem, and radiation tolerance needs to be verified and characterized for any combined effects on an as-needed basis for their target environments.

# 7.0 State of Cold Electronics Technologies and Gap Analysis

Section 7.1 provides the scope of this assessment and key definitions. Section 7.2 describes the lunar environments of interest, assumptions for temperature ranges, and several thermal cycles and/or shocks expected for different types of lunar missions in these environments. Section 7.3 reviews various avionics architectures and delineates some of the advantages of distributed and hybrid architectures that are enabled by cold capable electronics, which in turn lead to a prioritization of cold capable electronic parts, assembly and subsystem developments. Sections 7.4 through 7.8 describe the states of the art or practice, qualification and evaluation approaches, and gap analyses in the areas of COTS electronics, custom electronics, passives, packaging and materials, and power systems respectively. Section 7.9 provides a description of evaluation and qualification methodology and NESC guidance on cold electronics qualification.

# 7.1 Scope of Assessment and Key Definitions

The goal of this assessment was to evaluate the potential continuous use of these electronic parts and assemblies with minimal or no thermal management on missions of up to 20 years in all regions of the lunar surface (e.g., permanently shadowed regions (PSRs) and equatorial). The assessment attempts to define an 80% solution and one that is workable for general electronics parts and assemblies. The defined scope of the assessment was to capture the state of cold electronics in NASA, industry, and academia; their applications and challenges for lunar environments; identify gaps; provide NESC guidance for cold electronics selection, evaluation,

qualification, and screening for lunar missions; and provide NESC recommendations for technology advances and follow-on actions to close the gaps.

The following are key definitions in this report.

### Electronics:

- Cold Electronics and Cold Capable Electronics are used interchangeably in this report and refer to both cold operable electronics and cold tolerant electronics, which are defined below. In this assessment, the temperature range is extended to include cryogenic temperatures and wide temperature range for lunar environment.

- Cold Operable Electronics Electronic technologies, parts, assemblies, subsystems, and their packaging that are capable of operating stably in environment having a lower limit below the military specified minimum temperature of -55 °C (218 K) and can be successfully "cold-start". The military specifications are -55 to +125 °C (218 to 398 K) per MIL-PRF-38535, paragraph A.3.1.3.20.,

| Jp pp                                          |                       |

|------------------------------------------------|-----------------------|

| Standards                                      | Temperature Range     |

| Military standards and specifications          | -55 to +125 °C        |

| www.dsp.dla.mil/Specs-Standards                |                       |

| Automotive Electronics Council (AEC) standards | between -40 to +85 °C |

| www.aecouncil.com                              | and -40 to +150 °C    |

| Joint Electron Device Engineering Council      | -40 to +85 °C         |

| (JEDEC) standards www.jedec.org                |                       |

Table 7.1-1 Typical Specified Temperature Range

- Cold Tolerant Electronics Electronics technologies, parts, assemblies, subsystems, and their packaging with ability to tolerate repeated cycles into cryo-temperatures without significant degradation. It is primarily an issue of packaging materials compatibility at the part and circuit assembly level. "Cold tolerance" is distinctly separate from "cold operable," in that "cold tolerance" does not deal with operation of the electronics in and across the temperature range, but rather their ability to survive if thermal cycled or shocked while in a quiescent or unbiased state. Thermal Cycle Resistant Electronics and Cold Survivable Electronics are two other terms used in other literature.

- Cold Start In the context of electronics intended cryo-temperature operations, the term "cold start" is the condition where an electronic part or subsystem is unpowered and is at thermal equilibrium with the cold environment. This is considered the worst-case condition for starting the circuit at cryo-temperatures.

- Cryogenic Temperature or Cryo-temperature When common atmospheric gases are condensed into a liquid state at a temperature that is below the normal gas-liquid transition point (a.k.a. boiling point). Cryogenic Society of America defines the *Cryogenic Temperature* range from -150 °C (123 K) to absolute zero (-273 °C (0 K)). Note that the term cryo-electronics has been used in the study of superconductivity and quantum computing. Neither superconductivity nor quantum computing applies to this assessment

- **COTS/MIL** Any commercial, automotive, space, or military off-the-shelf parts which are not designed specifically for cold operation below -55 °C (218 K).

#### Architectures:

- Centralized Architecture The physical location of most of the avionics. A centralized architecture for a cold environment (e.g., the lunar surface) would use a single, centrally located WEB that provides a benign temperature range for the electronics. An occasional part (e.g., a focal plane readout or a position sensor) might be located external to the WEB and may or may not have heaters and/or other thermal control elements associated with it, but mostly the avionics are housed in the WEB.

- **Distributed Architecture** The physical location of most avionics subsystems. The subsystems are distributed around the vehicle or platform to be optimally located for mechanical, operational, and electrical purposes and not in a centralized WEB. The electronics are assumed to have minimal to no thermal management support and are therefore required to be robust and reliable in the extreme thermal environment of the lunar surface.

- **Hybrid Architecture** A physical distribution of the avionics such that while most of the avionics is housed in a WEB, there are significant elements of subsystems that are located outside the WEB and subject to the lunar surface environment. Examples include the lownoise amplifier (LNA) and Power Amplifier of a radio frequency (RF) system, both of which might be mounted at the antenna, while the rest of the RF system is housed in the WEB.

- Lunar Power Hibernation Architecture This is an architecture specifically intended to address the need of solar powered spacecraft to survive the 354 hour long and extremely cold lunar night (including a nearly 5 month long lunar polar winter). *This concept has no WEB* and virtually all elements of the spacecraft are exposed to the lunar night environment. When solar array output ends at lunar dusk and the battery charge is too low or temperatures are too cold for battery cells to operate, the system shuts down and hibernates until the solar arrays are illuminated at lunar dawn.

#### Level of integration:

- **Assembly** A board/substrate populated with multiple packaged parts and passives.

- Parts A part refers to a single packaged electronic device. Parts can be active or passive in its electrical behavior and may contain multiple dies or devices if they are contained in a single package.

# 7.2 Target Thermal Environments

In this section, target thermal environments are defined for this assessment. The environments are specified as:

- Thermal environment in the various regions of the lunar surface (e.g., lunar equatorial region, mid-latitude regions, polar regions, PSRs).

- Range, number, and rate (fast/slow) of thermal cycles experienced in various types of missions (e.g., exploration rover, habitat, in situ resource utilization (ISRU) mining and processing).

- Thermal environment experienced by the electronics <u>without</u> an active thermal management system on various types of platforms (e.g., rover, habitat, excavator).

- Thermal Hibernation, a special case in which the electronics are allowed to soak, in a quiescent or unbiased state, to reach equilibrium with the worst-case cold environmental temperature of the region in question and can then successfully and correctly initialize upon application of power.

- It should be noted that, for the purposes of this assessment, the temperatures and thermal cycles specified below are not the worst-case extreme temperature ranges that might be experienced by surface platform electronics, but rather an "80% worst case" that can be used for general purpose electronics selection and preliminary evaluation and qualification planning during the early development phase when mission specific data are not available. Actual worst cases for specific equipment, depending on a host of factors, could be significantly worse or better.

Much of the following discussion was developed by the Applied Physics Laboratory (APL) Lunar Surface Innovative Initiative (LSII) in a study report "Assessment on Cold Electronics for Lunar Missions" commissioned by this assessment. The full report is attached as Appendix A and summarized below. In Appendix B, additional information was provided by the NASA Lunar and Mars Environments Analysis Team (LUMENATE), which can be contacted for additional information regarding thermal design considerations, modeling techniques, and environmental; factors for assets emplaced on the lunar surface.

The orbital period of the Moon around the Earth is approximately 27.3 days, but as the Moon and the Earth are changing their positions with respect to the Sun, it takes approximately 29.5 days to observe a full lunar cycle. This results in a lunar equatorial region that is illuminated for approximately 354 hours, followed by an approximate 354 hours of continuous darkness. Moreover, the Moon has a spin axis that is inclined by 1.5 degrees from the normal to the plane of the Moon's path around the Sun. This geometry allows for extreme surface thermal hot cases at the equator (almost 127 °C/400 K) and complex illumination conditions at the poles which vary by seasons, location, and local topography. Additional determinants of the lunar surface thermal environment include:

- Due to lack of atmosphere, lunar surface temperature is primarily determined by the effective solar irradiance which is closely tied to latitude dependent solar incidence angle and local terrain slope, as well as thermal radiation exchange with the lunar regolith which is region dependent. Mare regions are relatively flat and the regolith there has higher solar absorptivity resulting in hotter surface temperatures. Highland regions typically contain steeper terrain (e.g., mountains and craters) and the regolith has higher solar reflectivity resulting in cooler surface temperatures.

- Minimum temperatures occur prior to local sunrise and are dependent on the adjacent terrain (e.g., solar occlusion, view factor to surface), thermophysical and thermo-optical properties of the lunar regolith, and the specific platform upon which an asset is mounted (influences adjacent regolith radiation exchange and view factors to space

- In the equatorial region, differences between the near side and far side temperatures are not significant and show the same variation between maximum and minimum extremes.

- The coldest locations on the lunar surface are found at the bases of large impact craters at the poles where incident solar illumination is perpetually absent. These locations are known as

PSRs. Temperatures inside PSRs can vary, but conventional practice is to assume a worst-case for this region.

- During daytime hours, local shadowing can occur due to terrain and platform geometries. This is particularly true for polar regions, where the sun never rises very high in the sky and topographical features can induce lengthy shadows that can last for hundreds of hours.

- The thermal inertia (defined as the resistance to temperature changes when subjected to heat sources) of the lunar regolith is so low that even brief shadows can result in near nighttime temperatures adjacent to otherwise illuminated terrain. The inverse is also true in that shadowed regolith can rapidly increase in temperature when illuminated for brief periods.

- Elements with significant stand-off distances such as vertical solar array technologies (VSATs), human-rated landers, and communication towers will be required to withstand extreme variations across their structures [ref. 1] (and potentially electronics) due to varying illumination durations which are dependent on separation height from the Lunar surface. This is especially true in Lunar polar regions where the Sun maintains proximity to the horizon; large gradients will be experienced both across the height and width of tall structures.

# 7.2.1 Thermal Environment Experienced by the Electronics

Several sources, including NASA Human Landing System Lunar Thermal Analysis Guidebook [ref. 2], provide extensive information regarding thermal modeling techniques for the Lunar environment which can readily be applied for electronics development applications. Measurement of lunar surface as well as platform temperatures have been taken by various missions including in extreme regions such as far side of the Moon and the floor of the Von Karman Crater. Appendix A contains specific temperature measurements made on several platforms in these extreme regions. These measurements were obtained via the Lunar Reconnaissance Orbiter (LRO) Diviner Lunar Radiometer Experiment which has a spatial data resolution is 240 meters per pixel and temperature value error of ±5 °C [ref. 3]. For polar regions where terrain topology is extremely complex and the solar elevation angle stays near the horizon, the relatively low spatial data resolution of the Diviner instrument can reduce its utility for estimating surface temperatures at a specific mission location.

Permissions per Dr. N Petro/NASA GSFC and Dr. Paige/UCLA

Figure 7.2-1. Lunar Reconnaissance Orbiter DIVINER Surface Temperature Data Thermal model calculations of monthly and annual lunar surface temperature variations at various lunar altitudes.

The LRO data, shown in the Figure 7.2-1, shows lunar surface daylight temperatures have a very cold and wide range (-173 °C (100 K) to ~127 °C (~400 K)) over polar to equatorial latitudes. Lunar nighttime temperatures have a much narrower range. Non-polar surface assets will be exposed to an approximately the 354-hour lunar night with minimum temperatures that fall between -204 °C (69 K) to 178 °C (95 K) depending on latitude. The red dashed line indicates where lithium-ion (Li-ion) battery cells freeze ~-73 °C (200 K). The yellow dashed line bounds the range of lunar night temperatures for all latitudes. Note that both the coldest minimum (~-223 °C (50 K)) and warmest minimum (~-173 °C (100 K)) temperatures appear at the polar latitudes (see dark blue 89° latitude line). This is due to the moon's ~1.5-degree inclination to the sun that creates a seasonal effect on surface temperatures at the poles. Polar missions can exploit the long daylight and short night cycles of the lunar polar summer by locating assets at points that experience near continuous solar illumination due to their high vantage point relative to adjacent terrain. However, polar missions can be confronted with, depending on the mission location, surviving a lunar polar winter where a lunar night may span 4.7 lunar cycles with temperatures sinking to below -223 °C (50 K).

There is insufficient measured lunar surface thermal data spatial resolution and no universal generic thermal model that can be used by early mission system and avionics developers to determine the thermal environmental extremes over lunar surface regions for platform or electronics outside of the WEB. At present, the avionics community generally uses the lunar regolith surface temperature in the regions of interest and assumes these are the worst-case temperatures seen by the electronics [F-1].

In Appendix B, the NASA LUMENATE uses a simplified thermal model to provide some insight into the potential differences between regolith surface temperatures and the effective thermal environment exposed to electronics outside of a WEB. One of the examples is shown in Figure 7.2-2 for a specific lunar south pole location, where regolith surface temperature range is -228 to -143 °C (45 to 130 K) and the electronics temperature is -238 to 52 °C (35 to 325 K) for typical electronics optical properties. Appendix B contains additional information and analyses, including modeling details and assumptions. As shown in Appendix B, the regolith surface temperatures only serve as a starting point when mission details required for accurate thermal environment determination are unavailable. Accurately identifying worst-case and actual thermal environments requires knowledge of the specific mission location, mission date range, platform configuration, electronics location and orientation within the platform, and mission operations [F-2].

Figure 7.2-2. An Example of Thermal Environment for a Specific Platform Configuration and Specific Lunar South Pole Location

(solar absorptivity / IR emissivity)

So, while the use of regolith temperatures is clearly an oversimplification, it is a useful first-step approximation of the worst-case for the cold end of the thermal range, although it is likely that some electronics may be exposed to even colder effective environmental temperatures. The electronics in a WEB are normally subjected to a more benign thermal environment. One significant exception being when cold soaked due to hibernation or initial startup after landing/deployment, when it is reasonable to assume that the avionics will have reached equilibrium with effective environmental temperature prior to operation. Colder temperatures may be seen, relative to the surface temperature, for example, if the part is placed above the regolith and oriented to have a view of deep space. It also noteworthy that regolith surface

temperatures as cold as -248 °C (25 K) have been measured in PSR. This assessment covered most electronics applications and accepted that in some cases more extreme thermal conditions may be experienced by specific electronic elements, which will have to be treated differently, either by providing some minimal thermal management or by qualifying to a project-determined temperature range.

The warm end of the thermal range is often assumed to be the worst-case regolith temperature. This is an oversimplification due to factors including electronics internal heat generation, incident solar flux, and reflected and emitted thermal radiation from the lunar surface. Those factors are likely to warm the electronics beyond regolith surface temperatures if no thermal management is provided. Temperatures could be biased higher because of lunar dust deposition and the resulting change in surface thermo-optical properties.

It is not uncommon that avionic developers need to start the process of reviewing, evaluating and selecting electronics technologies for an application when MEAL specifications are not available. For the purposes of this assessment, the NESC team recommends using the following generally accepted regolith surface temperatures *as the starting point* for cold electronics on lunar surface missions when no MEAL specifications [ref. 4] are not available, and engage thermal subject matter experts (e.g., NASA LUMENATE) as early as possible in the process to help define the expected temperature extremes to be experienced by the electronics outside of a WEB.

Based on empirical data, as well as scientific analyses to date, generally accepted regolith surface temperatures in different lunar areas are [Appendix A]:

- Permanently Stationed Platforms:

- Equatorial -180 to +125 °C (93 to 398 K)

- Mid Latitudes -145 to +80 °C (128 to 353 K)

- Poles -223 to -193 °C (50 to 80 K)

- PSR -233 °C (40 K) (Not absolute worst cases, but an educated assumption for the 80% case)

- Mobile Platforms:

- Transport in/out of PSR -233 to -40 °C (40 to 233 K)

- Roving broadly, -145 to +120 °C (128 to 393 K)

#### 7.2.2 Thermal Cycles

For stationary platforms, one can assume slow thermal cycles with extremely low ramp rates and long dwell times that can be worst case by standard Military Standard (MIL STD 883) and NASA standards for electronics thermal cycling (e.g., ~ 5-25 °C/min). For mobile platforms, however, when crossing through shadow, it is possible that due to a lack of atmosphere the electronics may experience a fast thermal cycle (i.e., a thermal shock) which is a rapid transition between the warm and cold temperatures (e.g., > 100 °C/min). Without additional measurement or analysis, the NESC team cannot confidently specify a ramp rate for these thermal shock events but the Military and NASA standards for thermal shock can be used for a reasonable approximation of expected worst case conditions experienced by the electronics.

Regarding the number of thermal cycles that different missions might experience, the NESC team found several canonical reference missions that may be used to bound parameters of mission duration and number of thermal cycles/shocks experienced [Appendix A, refs. 5, 6, 7].

- For stationary platforms such as habitats or power generation stations, the NESC team expects a 20-year mission duration, and thus the number of slow cycles is approximately 12 lunar day-night cycles/year x 20 years. Note that the complex shadow environment on the south pole may result in more than 12 cycles per year.

- For mobile platforms there is a similar slow thermal cycle regime, but because the platform might wander in and out of shadow during its lifetime, a number of fast thermal cycles (or thermal shocks) need to be added. In this case, the fast thermal cycle is once into shadow and once out of shadow where the transition from low to high or high to low temperature is extremely fast and the time spent in shadow or light is sufficient to allow the electronics to reach thermal equilibrium. Assuming that these fast thermal cycles only occur during the daylight period of the lunar day, and that such a shadowed area might be encountered (and arbitrarily chosen) 14 times during that period, then it is approximately 14 fast cycles/lunar day x 12 lunar days/year x 20 years.

- For ISRU mining operations, the NESC team assumed a 10-year mission duration, and excursions between the PSR region and the adjacent polar region with a 10-hour cycle (i.e., in and out of the PSR every 10-12 hours, approximately 2x28 fast thermal cycles/lunar day x 12 lunar days/year x 10 years [Appendix A, refs. 5, 6, 7]).

## 7.3 Avionic Architectures for Cold Environment

## 7.3.1 State of the Art

In reviewing various architectures for lunar surface platforms, this assessment draws on experience from Mars projects as well as various technology developments and studies (e.g., Europa Lander, Cold Rover, Mars Rovers (Mars Exploration Rover (MER) and Mars Science Laboratory (MSL)), Distributed Motor Controller for Mars Rovers, MUSES-CN Rover, Commercial Lunar Payload Services (CLPS) Cold Arm). Additionally, this assessment commissioned a study by the Applied Physics Laboratory (APL) Lunar Surface Innovation Initiative (LSII) team (Appendix A), which summarized much of the data from these references and categorized electronic elements with respect to utility for future lunar surface missions.

With the exceptions noted herein, little avionics system architecture work has been done in implementing extreme cold electronics meeting the thermal environments specified in section 7.2. The exceptions are applications of individual parts such as an operational amplifier for Jet Propulsion Lab's (JPL's) Mars Rover Motor Control subsystem, which is required to be resident at the motor, various infrared focal plane read out parts (which are similarly required to reside in the cryogenic environment of the focal plane), and various Mars Rover cameras. These are mostly custom, one-off parts that do not address the broader issue of cold capable electronics or avionics architectures.

Studies of cold rovers for Mars [ref. 8] and similar applications have been performed. For the most part, these have not been implemented and while the studies to date show feasibility, they do not necessarily define an evolutionary path toward a fully cold capable architecture. Further, these studies have generally been for a Mars environment and for landers and rovers. While these provide useful information for a Lunar Cold Capable Avionics Architecture, they fall far short of the requirements for a lunar surface mission set.

A notable exception is the Lunar Power Hibernation & Recovery Architecture introduced in a GRC study in 2022 [ref. 9].

STMD ranked "survive and operate through the lunar night" as the number one "shortfall" in capability [ref. 10]. The lunar power hibernation is a near-term approach that employees cold electronics to meet the shortfall [F-3]. It is an architectural approach that integrates cold electronics and Li-ion cells capable of surviving multiple freeze/thaw cycle into a power architecture that can hibernate and survive the lunar night and successfully recover at lunar dawn. It was developed specifically for the low-cost robotic missions of the CLPS program but is applicable to a broad range of lunar missions and provides an evolutionary step requiring only specific parts of the power system to be cold operable while allowing the remainder of the system to be cold survivable.

Hibernation is a strategy that addresses the problem of a lack of power generation at night and insufficient energy storage to maintain operating temperatures for standard electronics in the extreme cold environment (-173 °C to -223 °C (100 K to 50 K)) of the lunar night [ref. 11]. In this architectural approach, the bulk of the electronics are not required to operate in extreme cold but are only required to survive the cold without degradation (i.e., most of the avionics including the flight computer and the battery cells). The cold operational electronics are limited to a portion of the power management and distribution subsystem as required to perform a reliable cold-start and to operate at lunar dawn temperatures.

To minimize the changes to existing spacecraft, cold-operable electronics are limited to portions of the power system essential for hibernation recovery (i.e., solar arrays, main bus control, and battery management). These elements represent the core of the cold-operable electronics needed for dawn recovery. This approach minimizes the electronics redesign and requalification effort, thus enabling an evolutionary approach to cold operational avionics systems. Li-ion batteries are cold survivable but are limited in operation since they lose the ability to charge or discharge at a temperature well above the lunar night temperatures. The success of the power hibernation approach depends on the use of cold electronics for reliable recovery of the battery.

The diagram in Figure 7.3-1 illustrates the lunar power architecture and some of the cold electronics functions needed to recover from a lunar hibernation. The diagram shows systems operable at cryo-temperatures in yellow, most notably the main bus controller (MBC). These systems must be cold-capable and able to achieve a cold start at lunar dawn. The remaining electronics are required to be tolerant of cryo-temperatures, but not expected to operate until nominal temperatures are regained.

When the arrays are initially illuminated at lunar dawn, the hardware will be at its coldest point in the cycle. At very low temperatures, solar arrays will generate substantially higher open circuit voltages than at normal temperatures [ref. 8]. To protect the arrays and power bus from overvoltage damage, it is necessary to manage the array output shortly after the array is illuminated. A simple overvoltage shunt circuit capable of a cold-start and operating at lunar dawn temperatures provides overall protection. Normally a spacecraft starts upon connecting the battery power to the main bus at which point the power system executes a power-up sequence. However, in the case of hibernation recovery at lunar dawn, the battery will be frozen and isolated from the main bus after experiencing a lunar night. Further, avionics and other loads are intentionally inhibited and remain in a passive unpowered state until the main bus is fully stabilized. The MBC, capable of a cold start at extreme cold temperatures and operating on the solar array output alone, is required to start the power-up sequence and is the essential element to the recovery process. As the sun rises the photovoltaic (PV) array power output continues to increase. The MBC must begin to regulate arrays while the avionics is still unpowered, and the

battery is hibernating. The MBC begins to methodically distribute power to heaters as the array output climbs. The MBC slowly raises the temperature of the batteries and the other hibernating systems to their respective operational temperature range. Without a battery to stabilize the power bus, it is important that the loads are activated in a stable manner. To avoid instability, large reactive loads, such as motors, are inhibited until the battery is warm and ready to be connected to the main bus.

Figure 7.3-1. Lunar Power Hibernation Architecture employing Cold Electronics without a WEB

To manage the battery recovery, a Battery Management System (BMS) is required to monitor the recovering battery through the cell thaw process, and thus must be operational before the battery is thawed. The battery cells will not warm uniformly without some form of active temperature control. Cells at significantly different temperatures will have differing states of charge and cell voltages. Warm cells will tend to charge colder cells. Charging of very cold cells degrades the electrodes and damages the cells. Therefore, the BMS will manage the thermal recovery to assure the battery cell temperatures are uniform. As cells thaw and recover their normal state of charge (SOC), the BMS may need to check the individual cell state and, if necessary, perform cell balancing. As the battery temperature is returned to its normal operating state, the BMS reports the battery voltage and SOC to the MBC.

If the MBC detects a significant mismatch in main bus and battery voltage after thawing the battery, then the BMS may need to perform a battery "pre-charge" cycle to match the main bus to assure that the battery does not disrupt the main bus when reconnected. When voltages match, the MBC commands the isolation relay to reconnect the battery to the bus thus stabilizing the power system.

Once avionics are warmed up to operating temperatures, the MBC then begins methodically activating the power distribution system to power up the avionics. The highest priorities are

mission dependent but are likely to be the radio transmitter, flight computer, and data network. With the flight computer active, the power management can be taken over by a software module in the flight computer. With the data system, flight computer and RF communications reestablished the spacecraft can resume interaction with mission control as necessary for the mission.

Motor control is the area where cold electronics have been studied the most and at least partially implemented. With the possible exception of the hibernation architecture above, this may be the most compelling application for cold capable electronics in Mars and Lunar missions, primarily for rovers and similar vehicles, which have many motors and actuators. The NESC team found three significant efforts in this area<sup>1</sup>:

- 1. The Motiv company's motor controller for the JPL STMD Cold Arm project utilizes mostly existing off-the-shelf parts. For this project, Motiv developed a cold capable power converter -part for this specific application. The Motiv Cold Arm motor controller was tested to -180 °C and provides a strong existence proof for cold capable electronics and the potential utility of both custom and COTS parts. It is not generally applicable to the broader lunar surface mission set as it was designed to provide capability for the defined CLPS mission.

- 2. The initial Mars Program Distributed Motor Controller Technology Development developed a fully functional prototype of a cold capable distributed motor controller with all electronics capable of being mounted adjacent to rover motors. While a prototype was developed and tested, it was never fielded due to the complexity and perceived unreliability of the subsystem due to the large number of parts and the complexity of the design. The motor controller was implemented with readily available discrete parts comprising thousands of parts in an extremely complex design and an even more complex fabrication process.

- 3. The Follow-On Mars Program Distributed Motor Controller Technology Development developed a single cold capable mixed signal application specific integrated circuit (ASIC) that replaced the majority of the of discrete parts in the original Mars Distributed Motor Controller and simplified both the design and the fabrication process. The ASIC was implemented in 0.5 micrometer (µm) Silicon Germanium (SiGe) technology and fundamentally changed the design of this motor control subsystem. Although the ASIC was tested between -125 °C and +85 °C (148 K and 358 K) and was demonstrated in a prototype system to be of significantly higher efficiency than commercially available motor controllers of the day, due to budget limitations, it was never implemented in a full prototype or qualified for use in the Mars environment. Neither the technology nor the subsystem was fully developed. This technology project, however, is the closest the NESC team found to a part/subsystem implementation that can provide an example of a hybrid architecture and a paradigm for an evolutionary approach to cold capable avionics architectures. It utilized a warm box to house the main power conversion and computing elements of the system and a cold capable mixed signal miniaturized module that housed the local power conditioning and control, actuator, and sensor electronics. The module, about the size of a thick credit card, utilized chip on board technology to mount the above-mentioned ASIC and associated discrete elements to optimally perform local sensing and control of actuators. The module also implemented a dual redundant serial bus to communicate with the WEB-housed computing system. This architecture allowed use of extant off-the-shelf computing and power generation parts and subsystem assemblies within the WEB while distributing the

<sup>&</sup>lt;sup>1</sup> Based on discussions with JPL and industry engineers.

actuator-associated electronics. Thus, the amount of copper penetrating the WEB was minimized and the digitization of low-level sensor signals and modulation of motor power signals was placed as close as possible to the actuators. Not only was the amount of harnessing and connectorization minimized, but it also optimized the EMI/C environment, thus significantly improving subsystem performance as well as SWaP-C. The fundamental principles of architecture optimization, developed and demonstrated in the Follow-On Mars Program Distributed Motor Controller Technology Development paved the way for cold capable avionics architecture evolution and a roadmap for the development of cold capable electronics parts.

Finally, a notable exception to the above was the JPL MUSES-CN Nano-Rover, a very small, extremely low power rover developed for a one-month asteroid exploration and sample acquisition mission. The rover had no thermal management system and was designed to withstand a temperature range of -180 °C to +110 °C (93 K to 383 K). It was successfully tested in a thermal vacuum chamber to those temperatures. The rover utilized selected COTS parts and custom packaging. It did not use a battery, relying instead of ambient solar illumination for power. Although the MUSES-C mission was cancelled, and thus the rover not finally qualified or flown, this technology development project does validate that, at least for short duration missions without significant thermal cycling, it is possible to develop such a system by utilizing carefully selected COTS parts and clever packaging [refs. 12, 13].

It is also noteworthy that the Mars Helicopter, while not designed for hibernation or cold operation, did survive a Mars winter, during which it "froze" (i.e., the battery was not able to maintain survival temperature throughout the winter, causing the electronics to experience the Mars winter temperature and the battery to freeze). Upon receiving sufficient solar illumination and warming conditions, the helicopter was able to resume operation.

The current architectural approach for avionics required to operate in extremely cold environments, such as Mars or Deep Space, is to place the electronics in a WEB and cable out to actuators and sensors that are custom designs built for these extreme environments [F-4]. While it is desirable to eventually enable all the avionics to be cold capable, an intermediate or interim evolutionary step would be to prioritize the avionic subsystem elements that provide maximum benefit if allowed to operate outside the WEB.

The WEB itself is usually highly insulated to ensure that heat from internal heaters and electronics is retained. This results in a potential for overheating due to electronics self-heating. Further, the requirement to cable through the WEB walls to access external sensors and actuators incurs the penalty of a large gap in the WEB thermal barrier that must be accounted for. Additionally, for systems which are required to hibernate, internal heaters are typically needed in the WEB, and possibly in any external electronic parts, due to a general inability of electronic parts to correctly start up and initialize in the cold environment, even if they can operate well in the cold once active as well as reliability concerns (e.g., due to hot electron injection effects) in long term operation of these parts in the cold.

Aside from work in avionics, there are some efforts focused on developing electronics for other cryogenic applications. For example, the Advanced Energy Technology Platform (AETP) program funded by the government of New Zealand is supporting the development of cryogenic electronics, for use with hydrogen storage and superconducting motor applications for large scale transport [refs. 14, 15, 16, 17]. This includes evaluating commercially available Gallium-Nitride

(GaN) High Electron Mobility Transistors (HEMTs) at -196 °C (77 K), developing new nanocrystalline based inductors optimized for cryo-temperatures, as well as design of full switched mode power converters capable of operating under these conditions. Many of these parts and design approaches can be transferred to lunar applications.

### 7.3.2 Gap Analyses

The gap between what is required per Section 7.2 and the state of the art per Section 7.3.1 is essentially that no cold capable avionics architecture meeting requirements like those of lunar surface missions has yet been fully implemented. Studies and technology readiness level (TRL) 3<sup>2</sup> prototypes show the feasibility of such an architecture, but none has yet been fully built, qualified, or fielded.

Given the state of the art as described in 7.3.1 above, the gap analysis is relatively straightforward. No cold capable electronics architectures that are generally applicable to the lunar surface environment have been implemented or even studied to the degree necessary to initiate the detailed design of such an architecture [F-5]. Basic principles and optimization approaches leading to an evolutionary roadmap to cold capable architectures are evident and have been initially validated by studies and technology developments aimed at Mars-capable avionics subsystems and the hibernation power subsystem.

From an architecture implementation perspective, given the lack of cold capable electronics technology maturation, it is impractical to immediately implement a fully cold capable avionics architecture for lunar surface systems [F-6]. Rather, the NESC team recommends an evolutionary approach. Estimating relative difficulty of development (and therefore development costs) versus benefits to future projects, it was deemed prudent to prioritize the cold electronics technologies and products to be developed. In determining maximum benefit and return on investment, several primary considerations emerged:

- Minimizing any thermal paths through the walls of a WEB.

- Minimizing noise and electrical path length of small signals between instrument transducers and support electronics.

- Minimizing noise and electrical path length of large signal excursions (and thus potential EMI/C) between support electronics and actuators.

- Supporting the maximum number of platforms and missions with the minimum number/cost of electronics developments.

- Maximizing near-term return on investment (ROI) to prove the efficacy of this approach and encourage continued funding for these developments by NASA as well as other entities including industry and Department of Defense (DOD).

- Focusing on near-term needs (i.e., items that will enable or enhance missions expected to be developed/fielded in the next 5 to 10 years).

- Enabling key steppingstone hybrid architectures such as the hibernation architectures.

-

<sup>&</sup>lt;sup>2</sup> https://esto.nasa.gov/trl/

### 7.4 COTS Cold Electronics

#### 7.4.1 State of the Art or Current Practice

COTS parts offer advantages for use in cold environments (e.g., lunar missions) in some aspects of such projects. They are significantly lower in cost, easier to procure and offer a broad range of functionalities and capabilities. Furthermore, technology analysis and experimental data suggest that many COTS/MIL parts are capable of operation, and not just storage, at temperatures well beyond the manufacturer specified temperature limits.

In the last 20 years the potential for COTS/MIL operation in cold has been explored by NEPP for a wide range of parts including resistors, capacitors, discrete parts like diodes and transistors, and both analog and digital integrated circuits, as well as hybrid parts containing integrated circuits and discrete parts. Most of this work has been done at Glenn Research Center (GRC) with some at JPL, Goddard Space Flight Center (GSFC), and Langley Research Center (LaRC). This and other published test results for cold operation of COTS/MIL were reviewed in 2018 under a JPL internal research task [ref. 18] and organized in a table containing data for approximately 200 parts. The table is being updated and will be hosted by NASA Electronics Parts and Package Program. It will be made available to the community as part of this study. These data provide an initial knowledge base from previous exploration of COTS/MIL usage in cold environments.

More recently, quantum computing has driven the development, design, and evaluation of electronics for operating at temperatures in the single digit Kelvin temperature range [refs. 19, 20]. However, the focus has been on the characterization of technologies for use in ASICs such as LNAs. Therefore, that work has little impact on the general findings from 2018 for COTS/MIL parts. The specific ASIC papers, however, will be added to the table.

In recent years, significant advancement has occurred in enhancement-mode GaN-based HEMTs. GaN HEMTs have matured significantly in commercial use and are now widely utilized in smaller and more efficient power converter chargers for laptops and smartphones. This wide usage signals a broader community understanding of key failure mechanisms and concomitant improvement in process control capabilities, thus, this is a prime area for exploration of new COTS/MIL options for space. Several papers have been published by universities demonstrating success in operating GaN HEMT in cryo-temperatures [refs. 21, 22]. Also, at least one vendor has begun providing the community with MIL qualified, radiation tolerant, discrete GaN HEMT [ref. 23].

For most part types of interest to NASA missions, pathfinder data that describes how the baseline technology performs in cryogenic environments may already exist. In this case, the data may point to one or more COTS/MIL candidates that show promising performance and are worthy of further evaluation. Such data can be used to make an initial assessment of the parts technology's performance in cryo-temperature ranges and whether COTS/MIL parts, implemented in these technologies, may be able to satisfy the mission needs or if custom parts will be required.

When operating COTS/MIL parts in cryo-temperatures, some performance and reliability changes will result. This is especially true when the gap between the COTS/MIL design temperature and the target cryo-temperature is quite large.

Some part performance parameters may improve in the cold while others degrade. The change is part-specific and often lot-specific as COTS parts are not designed for cryogenic operation. Therefore, testing in the specific operational environment is required for optimal part selection.

Less complex parts such as passive and discrete parts may have physics-based or chemistry-based descriptions for performance shift in cold temperatures. For example, various types of COTS/MIL diodes (including high current, small signal, Zener, Schottky, and SiGe diodes), tested between -190 °C and 25 °C (83 K and 298 K), all show similar shift of the forward bias current-voltage curve as predicted by the diode current equation, but details of curve shape and the amount of shift are dependent on diode design and fabrication technology.

Similarly, COTS/MIL power metal oxide semiconductor field effect transistors (MOSFETs) all show decrease in on-state resistance as temperature drops due to reduction in phonon vibrations, but the curve is different for parts from different vendors.

There are some COTS/MIL resistor and capacitor types that have cryo-temperature performance very similar to room temperature [ref. 18], so they would be viable candidates for use if the passives are further tested for reliability under actual use conditions. Passives' behavior in cold and selection criteria will be discussed in more detail in Section 7.6.

Some parts technologies have significant limitations at low temperatures. Silicon-based bipolar junction transistors (BJTs), for example, suffer from a decrease in current gain (β) as temperature drops below -196 °C (77 K). These parts, therefore, should be avoided for low temperature application. For this reason, silicon-based complementary metal oxide semiconductor (CMOS) integrated circuits should be checked for the presence of BJTs. This may be a challenge for COTS. In contrast, in some COTS parts, SiGe heterojunction bipolar transistors (HBTs), which is an excellent option to use instead of BJTs, as their direct current (DC) gains increase as temperature drops, may have been used. This technology is therefore also a key option for custom electronics for cold and discussed more in Section 7.5 [ref. 18].

Integrated circuits, both analog and digital COTS/MIL, have been explored for their potential utility in cold environments.

Mixed signals seem to be limited by analog circuits. An option may be to separate digital and analog parts to be able to choose the best cold performing parts for each case, but at the cost of less available board real estate.

Microcontrollers and field programmable gate arrays (FPGAs) are important to run the system or spacecraft, and COTS/MIL testing reveals that many COTS/MIL FPGAs start to behave poorly at temperatures as high as -123 °C (150 K). There are some candidates such as the Artix7 FPGA, which seem to have good performance down to -269 °C (4 K) except for increased jitter<sup>3</sup>.

Hybrid circuits, especially direct current to direct current (DC-DC) converters, and voltage regulators are an important part of power systems and discussed in more detail in Section 7.8. COTS/MIL parts from 9 different vendors were evaluated and some begin to show abnormal behavior at -40 °C (233 K) while others were able to perform normally until -178 °C (95 K)<sup>4</sup>. Detailed element analysis of the constituent parts is recommended before testing to rule out known problematic technologies such as silicon BJTs [ref. 18].

NESC Document #: NESC-RP-23-01873, Vol. 1

<sup>&</sup>lt;sup>3</sup> Based on discussions with JPL and industry engineers.

<sup>&</sup>lt;sup>4</sup> Based on discussions with JPL and industry engineers.

#### 7.4.2 Gap Analyses

Although much of the data collected through these studies is promising, there are several limitations that should be addressed before these parts can be selected for flight use. Most of the data have been focused on demonstrating capabilities at the temperatures of interest. Little to no data exist addressing reliability at these temperatures. The traditional high temperature acceleration may not be appropriate or sufficient here. Further, most testing of parts for operation at cryo-temperatures has not considered self-heating, wherein part temperature is raised due to thermal dissipation of the power expended by part operation.

This reliability data deficiency is partially due to the increased amount of testing and characterization needed to extend COTS/MIL operation into cryo-temperatures by as much as 123 °C/K below their design limits. Such a large temperature extension requires significant characterization and testing. When COTS/MIL parts are used outside of their datasheet specified thermal range, reliability and stability are not ensured and the lot-to-lot variation in operational parameters are expected to be significantly higher than in normal operation [F-7].

There is a lack of cold start data in the literature. Most of the capability studies are continuous operation studies where temperature is gradually lowered until abnormal behavior is observed. Cold start test data would be critical to eliminate self-heating effects [F-8].

## 7.5 Custom Cold Electronics

#### 7.5.1 State of the Art

For the Mars Science Laboratory (MSL) Rovers, NASA's Thermal Cycle Resistance Electronics (TCRE) Program developed a custom cold capable quad operational amplifier as an integrated circuit that is capable of operating between to -180 °C to 80 °C (93 K and 353 K). To meet the radiation requirements of Mars, the quad operational amplifier was designed in a radiation hardened process 0.35-µm silicon on insulator (SOI) CMOS [ref. 24]. In addition, the TCRE Program characterized performance of selected number of COTS parts at temperatures as low as -150 °C (123 K). This evaluation was performed to understand the COTS operating temperature margin as compared to what was advertised in their catalog. Through these characterizations, the TCRE program identified a set of COTS parts that were capable of operating at temperatures as low as -150 °C (123 K), suitable for Martian nights [ref. 25]. These parts, together with the cold capable quad operational amplifiers, were used to build the electronics for the "cold encoder" modules for the MSL Rovers. The TCRE program also developed the technology for packaging and assembly of the cold encoder electronics that made it possible for the electronics to operate on the Mars surface for long durations without any thermal protection [ref. 26]. This effort was necessary because the cold encoder modules needed to be positioned at the exterior of MSL actuators (without any thermal protection) for sensing and electrical encoding the position of their shafts.

The present state of practice for custom cold electronics is determined mainly by the following activities:

1. The recent development in cold and wide operating temperature range (i.e., -180 °C to 120 °C (93 K to 393 K)), radiation-hardened, custom electronics using SiGe bipolar CMOS (BiCMOS) technology (SiGe HBT + Si CMOS) for space exploration applications (which includes both naturally radiation tolerant and low temperature capable 90 nanometer (nm) SiGe HBTs) [ref. 27];

- 2. The development effort of CMOS-only (e.g., 180 nm or 90 nm) electronics for sense and control of cryogenic detectors (e.g., infra-red (IR) focal plane arrays (FPAs)), capable of operating over a narrow, low-temperature range of -180 °C to -150 °C (93 K to 123 K) [refs. 28, 29]; and

- 3. Use of Fully Depleted SOI CMOS for cryogenic applications [refs. 30, 31].